硅基毫米波收发前端集成电路研究进展

2021-10-14邱枫宛操罗雄耀邓帅徐涛涛梅术聪

邱枫 宛操 罗雄耀 邓帅 徐涛涛 梅术聪

0 引言

毫米波通常指的是波长为10~1 mm范围内的电磁波,其对应的频率为30~300 GHz.尽管对于毫米波的研究早在1889年就已提出,然而受材料、制造工艺、测试仪表的限制以及毫米波功率源等关键部件的不成熟,毫米波通信技术的发展较为缓慢.自20世纪70年代起,随着先进半导体器件的开发以及集成电路工艺的发展,使得器件性能大幅提升,生产成本大幅降低,毫米波通信技术也得到了较快速的发展与普及.

随着近年来微波6 GHz以下频段(sub-6 GHz)日益拥挤,其严重受限的带宽和较严重的干扰难以满足对无人驾驶、工业物联网等新兴应用对于高速率、低时延通信的要求.毫米波通信以其大带宽和丰富干净的频谱资源成为无线通信发展的重要方向.相较于sub-6 GHz频段通信,毫米波通信具有极宽的带宽,可以获得更快的数据传输速率;此外,毫米波通信可大幅缩小天线尺寸,便于实现大规模阵列集成;同时,毫米波通信往往利用窄波束进行传输,相较于sub-6 GHz频段的全向辐射,提高了通信的安全性.

然而,毫米波通信也存在不可避免的缺点:传输衰减严重.与sub-6 GHz频段信号相比,毫米波信号在恶劣的气候条件下,尤其是降雨时的衰减要大许多,严重影响传播效果.针对毫米波通信传输损耗大的问题,目前广泛采用的是Massive MIMO和波束赋形技术,可进行空分复用,形成较窄波束,降低干扰,提升信噪比和功率效率.在实际场景部署中,可借助多通道和多天线的收发增强对基站上下行覆盖进行增强,针对高低层建筑以及线状路面提供差异化的覆盖方案.

为了实现Massive MIMO 和波束赋形技术,毫米波的收发前端电路与sub-6 GHz频段的收发前端电路也有着较大的区别并具有以下特点:

1)大规模的收发通道数量.由于采用了Massive MIMO 技术,毫米波收发前端包含了更多的收发通道,以实现窄波束、高效率传输.然而由于通道数量的增加,系统的复杂度、功耗、成本也相应地提高,因此目前有部分研究集中在如何简化毫米波收发前端的架构,使其在保证性能的基础上,实现低功耗、低成本和小型化.

2)电路设计对尺寸更为敏感,需求的加工精度高.由于毫米波的波长较小,其性能对于尺寸较为敏感,因此增加了毫米波电路设计的难度,同时也对加工的精度提出了更高的要求.

3)对于移相精度要求高.由于采用了波束赋形技术,因此需要高精度的相位以实现对波束方向的准确控制.

4)与天线集成.在微波频段,由于天线的尺寸较大,很难和前端电路集成,而毫米波较小的波长,极大地缩减了天线的尺寸,方便了天线的集成.目前天线的集成包括片上天线集成、封装天线集成和混合集成等方式.

本文将介绍近年来的毫米波通信收发前端和毫米波雷达收发前端的一些新的技术.

1 毫米波通信收发前端进展

本节介绍毫米波通信收发前端的一些最新技术,包括新型的毫米波频率源、双向毫米波的收发前端架构、本振(LO)移相毫米波收发前端架构、TDD/FDD/FD毫米波收发前端、毫米波收发前端的天线技术.

1.1 毫米波频率源

频率源是收发机中的重要组成部分,可以提供信道的载波频率,为信号调制(如FMCW、两点调制等)提供参考信号.应用于毫米波收发机的频率源面临着低相噪、高频、宽带三方面的挑战,电路设计人员通常需要在这三者之间做权衡.目前常见毫米波频率源实现方案有两种:

第一种方案是直接使用工作在毫米波频段的锁相环,包括模拟锁相环[1-4]、数字锁相环[5-7].2018年,瑞典隆德大学的Ek等在IEEEJournalofSolid-StateCircuit杂志上发表了一款用于5G毫米波频段收发机的频率源系统[1],如图1所示,通过对PLL产生的信号进行上变频和下变频以得到需要的信号频率,这样的好处是可以减小频率源系统的高频生成压力,同时降低正交精度要求,压控振荡器(VCO)只需要输出载波频率的2/3就可以了.在接收机中,从天线接收到的24.5~29.5 GHz的信号与PLL产生的本振信号进行第一次混频,可以得到中频(IF)信号,约为载波频率的1/3.IF信号再经由正交混频器进行下变频到基带信号,此时本振信号由PLL输出信号经过二分频之后提供.在发射机中,信号变化方向正好相反,首先是将正交基带信号上变频后得到IF信号,然后再将IF信号与PLL输出信号混频后得到的上变频信号即为载波信号.这种方案整体框架简单,VCO的带内噪声得到了较好的抑制,但是由于输出频率与参考频率之间相差太大,即分频比太高,会导致PLL输出相噪高,恶化接收机信噪比.另外,由于VCO工作在毫米波频段,要想实现较宽的带宽对设计来说也是一个挑战.

图1 用于5G毫米波频段收发机的频率源系统芯片照片(左)及其系统框图(右)[1]Fig.1 Die photograph of PLL (left) and system architecture (right) for 5G millimeter-wave transceiver[1]

第二种方案是对低频锁相环的输出进行倍频得到毫米波频段的信号,这是目前毫米波频率源最常用的方案[8-14].在2021年的International Solid-State Circuits Conference(ISSCC)上,加州大学伯克利分校的Naviasky等发表的一篇28 nm CMOS工艺加工、工作在71~86 GHz的多用户波束成形接收机即采用该方案[11].如图2所示,整数型Ⅱ型锁相环的参考信号为3~3.5 GHz,VCO输出信号为24~28 GHz,经过注入锁定三倍频器(ILFT)变换之后得到65.5~87 GHz的射频信号,之后利用λ/4传输线对该信号进行功率分配分别进入不同的通道.为了实现更高的频率,也有级联多级倍频器的情况[12].数字锁相环也可以用于这种方案[15].除此之外,如文献[8-10]所示,三倍频也可以通过PLL输出信号与正交注入锁定振荡器(QILO)耦合后实现.使用第二种方案的好处在于避免设计高频VCO,倍频器的引入带来的噪声恶化很小,因此可以得到更好的相噪特性.但是第二方案依旧没有解决宽带的问题.

图2 工作在71~86 GHz的多用户波束成形接收机频率源的系统框图(a)和接收机芯片(b)[11]Fig.2 Frequency synthesizer used in 71-86 GHz multi-user beamforming integrated receiver,system architecture (a) and die photograph of receiver (b)[11]

1.2 毫米波双向收发前端

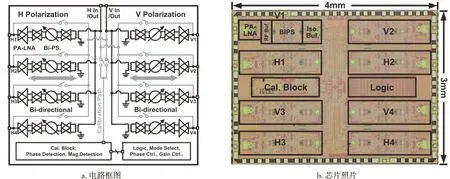

2020年,东京工业大学的 Pang 等[15]采用标准 65 nm CMOS 工艺实现了一款利用双向中和差分放大技术的 28 GHz 相控阵波束形成收发机(图3),适用于5G毫米波双极化多输入多输出(DP-MIMO)系统.在这项工作中提出了一种新型的双向中和差分放大技术,把发射链路与接收链路的有源放大单元对向连接,将自身的晶体管寄生电容作为对向链路的中和电容,并且共用匹配网络,通过尾电流源作为开关控制电路工作在发射或接收状态.这样的设计能够实现发射机和接收机共享完全相同的电路链,显著减小芯片面积,降低设计成本.此外,该项工作中还将 4H(水平极化)+4V(垂直极化)相控阵波束形成收发机芯片用于16H+16V 的双极化子阵列模块中,每个子阵列模块均由4个4H+4V芯片组成.两个子阵列模块就能够实现-50° 至 +50° 的波束扫描以及 45.6 dBm 的饱和等效全向辐射功率(EIRP),并且在 1 m 距离内,模块可以支持 15 Gb/s 的最大单载波(SC)模式数据速率以及 256-QAM中的 5G 新空口下行链路分组传输,而单元波束形成器所需的核心面积仅为 0.58 mm2.

图3 28 GHz双向相控阵波束形成收发机前端的电路框图(a)和芯片照片(b)[15]Fig.3 28 GHz bi-directional beamforming phased-array transceiver front-end,block diagram (a) and die photograph (b)[15]

2021年,清华大学的Zhu 等[16]采用 65 nm CMOS 工艺实现了一款基于耦合开关的W波段双向收发机前端(图4),适用于W波段毫米波成像雷达和通信系统.在这项工作中,提出一种新型的基于耦合的发射/接收(T/R)切换开关来控制通道工作在发射或接收状态,解决了传统λ/4 传输线T/R切换开关体积庞大以及需要附加额外匹配网络的问题.此外,还分别提出了新型、高性能基于耦合的移相器和衰减器,实现高分辨率移相以及稳定的增益控制功能.测试结果表明,该系统的3 dB带宽为 92~97 GHz,接收增益达到 25.2 dB,噪声系数小于 9 dB,发射增益达到 34.9 dB,饱和输出效率为 15.1 dBm 以及饱和 PAE达到12.3%,整体芯片面积仅为 0.99 mm2,是一款结构紧凑且性能良好的毫米波双向收发机前端.

图4 W波段双向收发机前端的电路框图(a)和芯片照片(b)[16]Fig.4 W-band bi-directional transceiver front-end,block diagram (a) and die photograph (b)[16]

1.3 毫米波本振移相收发前端

为了实现相控阵波束赋形,相位控制可应用于射频端、本振端或数字基带端.射频移相结构以其面积小、功耗低、可共享性等优点被广泛应用于毫米波收发机系统中,然而射频相移通常导致增益变化从而影响波束质量.基带移相具有最高的灵活性,但随着阵列规模增大从而导致系统复杂度和直流功耗显著提升.本振端的移相结构因为移相器的插入损耗、非线性不会直接影响射频前端性能,因此可以在不提高复杂度的前提下实现非常精细的波束转向分辨率以及增益不变的相位调谐[17-20].

2017年, Wu等[18]基于65 nm体硅CMOS工艺实现了具有波束赋形校准的4通道60 GHz相控阵接收机芯片,如图5所示.该项工作采用二次变频的方式,第一级LO由移相器和注入锁定倍频器组成的相移生成链产生,这种结构使得移相器只需要实现从-30° 到30°线性移相即可产生-90°到90°有效相位范围的LO输出,从而消除了传统注入锁定移相器中线性差和相位调谐斜率高的问题,同时有效抑制了输出振幅的变化.第二级LO采用片上多相滤波器将不同LO转换为正交信号,然后驱动正交注入锁定振荡器.通过顺序执行增益均衡、LO1的精确线性相移调谐和LO2的I/Q校准实现波束赋形的校准.对于22.5°的相邻通道相位差,经过校准后相位失配和幅度失配分别由±20°和±2 dB减小到±0.6°和±1.1 dB,合成的4通道阵列方向图的峰空比从17.5 dB提高到28.5 dB.

图5 4通道60 GHz相控阵接收机芯片[18]Fig.5 4-element 60 GHz phased-array receiver chip [18]

2019年,东京工业大学的Pang等[19]采用标准 65 nm CMOS 工艺开发了一款基于本振移相结构的4通道28 GHz相控阵收发机芯片,如图6所示.本振移相结构可以抑制相位调谐过程中引起的增益变化和旁瓣再生.该项工作实现了小于0.2 dB射频增益变化和0.3°相位误差的准连续相位调谐.为了实现精细的移相步骤,该项工作中设计的LO生成电路首先将24 GHz LO经相位滤波器产生四相信号,再经由象限选择器选择后进入移相器,从而移相器只需覆盖90°的移相范围,实现了线性和高分辨率的相位调谐.该项工作在-50°到50°的精确波束控制下实现了小于9 dB的旁瓣电平,在0°时达到了39.8 dBm的饱和等效各向同性辐射功率.

图6 4通道28 GHz相控阵收发机芯片[19]Fig.6 4-element 28 GHz phased-array transceiver chip [19]

2020年,东京工业大学的Wang等[20]同样基于本振移相结构设计了一款包含4个子阵列收发单元的64元39 GHz相控阵收发机芯片,该芯片内置了相位和幅度校准,允许在相位校准过程中具有恒定增益特性,实现了在360°全调谐范围内0.04 dB的最大增益变化.该项工作中提出了一种相位数字转换器和高分辨率相位检测机制,T/RX在RF级的相位和幅度信息可以向下传递到IF级,内置校准的测试精度为0.08°均方根相位误差和0.01 dB均方根幅度误差.此外还提出了一种用于LO馈通消除和通道间LO-LO隔离的伪单平衡混频器,采用双音信号输入的平方律检测器,从而不需要额外的LO输入.由16片该芯片组成的相控阵收发机在1 m距离的OTA测试中,在5G NR 400 MHz 256QAM OFDMA调制方式下实现了-30 dBm EVM,并且饱和输出下,其等效全向辐射功率为53 dBm.

图7 4通道39 GHz相控阵收发机芯片[20]Fig.7 4-element 39 GHz phased-array transceiver chip [20]

1.4 TDD/FDD/FD毫米波收发前端

为了满足增强移动宽带、海量互联网设备和超可靠低时延通信等场景的需要,5G通信采用灵活双工以及全双工工作模式.双工工作模式,允许两点之间同时在两个方向上传送信息.采用两个不同的频率用于发射和接收的称为频分双工(FDD),采用同一射频,不同的时段分别传送上、下行链路数据的称为时分双工(TDD).频分双工相对时分双工技术更加成熟,而时分双工可以节省一半的频谱资源,提高频谱利用率.不同于4G通信,5G时代很多应用场景中上下行链路业务对频率/时间资源的使用是随时间动态变化、不对称的.灵活的双工就是动态地分配使用频率或时间资源.全双工则是使用相同的射频同时进行上下行链路信号的传送,使系统的频谱效率加倍.

时分双工(TDD)系统依赖于片外发射/接收(T/R)开关,将RX与TX的高输出功率隔离开来,而现有的片上T/R开关解决方案是窄带或高损耗的.一项调查显示在2017年以前已经发布的SoC系统中,许多还没有集成T/R或带开关功能[21-24].

2017年,加利福尼亚大学的Xiao等[25]提出一种宽带集成T/R开关技术,消除了信号通路中传统的有损串联T/R开关,如图8所示,仅利用直流模式控制开关使TDD共存,系统将PA重新配置为LNA.在保持发射机功能和性能的同时,实现了扩频放大器到千兆赫宽带LNA的转换.在信号通路中没有串联RF开关,只有低频模式控制开关的情况下,实现了射频频率下的TDD共存.在PA模式下,饱和输出功率达到20 dBm,峰值漏极效率为32.7%.

图8 采用PA复用技术TDD前端嵌入的收发机的电路框图(a)和芯片照片(b)[25]Fig.8 The TDD transceiver embedded using PA multiplexing technology,schematic block (a) and chip micrograph (b)[25]

2019年,Rostomyan等[26]采用45 nm CMOS工艺,通过将4层PA输出和电感源简并级联LNA输入匹配网络与T/R开关结合成一个网络,如图9所示,使TDD前端总体损失最小化并且提高了毫米波收发器的PA效率和降低了LNA噪声系数(NF).PA达到23.6 dBm的饱和输出功率,峰值功率增加效率28%,而LNA达到3.2 dB的NF.该T/R组件结构具有较高的线性度,并能处理较大的PA输出电压波动.

图9 采用开关匹配网络TDD前端的收发机的系统框图(a)和芯片照片(b)[26]Fig.9 The TDD transceiver using switch matching network,system block (a) and chip micrograph (b)[26]

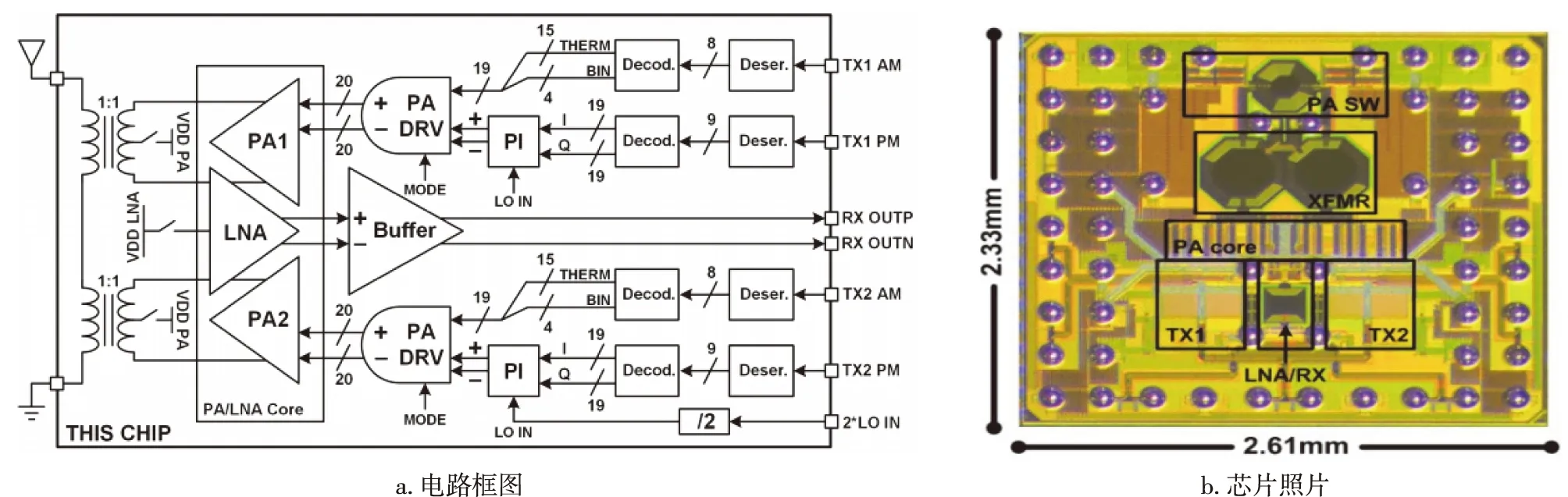

同年,卡内基梅隆大学的 Mondal 等[27]使用 65 nm CMOS 工艺实现了一款支持大规模多输入多输出时分双工(MIMO-TDD)技术与载波聚合时分双工(TDD)和频分双工(FDD)/全双工(FD)技术,并具有自干扰消除功能的可重构双向 28/37/39 GHz毫米波前端收发系统(图10).在该项工作中采用了同时支持 28/37/39 GHz 的双向射频前端收发机结构,将发射功能与接收功能融合到同一电路链路中,从而促进了多天线载波聚合(CA)或MIMOTDD 技术的使用,使得面积更加紧凑,成本降低.相较于传统的 PC-HBF系统,FC-HBF系统能够实现自干扰消除(SIC)机制,使得该前端适用于 FDD/FD 多天线系统,可直接应用于双频带数字波束形成器(DBF).该系统工作在 RX/TX模式下的功耗分别为 37.5/116.2 mW,在 28/37/39 GHz 工作频率下发射增益分别为 28.5/26.2/20.3 dB,饱和输出功率达到 15.8/16.8/16.7 dBm,PAE为 20%/21.6%/22.2%,接收增益为 16.1/10.9/8.3 dB 以及 6.2/7.0/7.9 dB 的接收噪声系数.

图10 28/37/39 GHz 毫米波前端收发系统芯片的系统框图(a)和芯片照片(b)[27]Fig.10 The 28/37/39 GHz millimeter-wave transceiver chip,system block (a) and chip micrograph (b)[27]

1.5 毫米波收发前端的天线集成技术

收发机的实际应用必然需要连接天线进行信号的辐射和接收.适用于毫米波收发前端的天线有封装天线和片上天线两种.片上天线较封装天线更加直接,芯片可以实现“零距离”互连.但是片上天线会大量占用芯片面积,对于先进工艺而言成本增加较大;同时硅衬底损耗较高,例如65 nm的CMOS工艺衬底电导率约为10 S/m,天线辐射效率低.因此,对于目前的毫米波通信应用,封装天线是一种主流方案.

总体而言,对于完整集成封装天线阵列的毫米波收发机的报道不是很多[28-30].2018年,LG电子的Kim等在JSSC上发表了一款封装了2×4天线阵列的直接变频收发机[31],该收发机工作频带为28 GHz,采用CMOS 28 nm工艺制造,用于5G通信.如图11a所示为收发机系统原理图,图11b为收发机与天线的封装结构.收发机中天线采用Yagi结构[32],如图12a所示,图12b为2×4天线阵列,天线阵列带有交叉极化双馈电,封装采用的是芯片级倒装结构[33].

图11 带有天线阵列的收发机的系统图和(a)天线下方封装的RFIC(b)[31]Fig.11 Transceiver with antenna array,schematic block (a)and packaged RFIC formed beneath the antenna array (b)[31]

图12 折叠Yagi天线[32](a)和2×4天线阵列[33](b)Fig.12 Folded Yagi antenna[32](a) and 2×4 antenna array[33](b)

测试结果表明,该收发机工作频率为25.8~28 GHz,发射机的EIRP可达31.5 dBm,输入噪声系数为6.7 dB.单个天线增益为4 dBi,8单元天线增益则为13 dBi.采用64QAM调制方式,发射到接收距离最大达到75 m.

2020年,加利福尼亚大学圣地亚哥分校的Nafe等[34]在IEEETransactionsonMicrowaveTheoryandTechniques上发表了一款2×64单元双极化双波束单孔径相控阵5G收发机,如图13所示.PCB上印有两个独立的威尔金森功率分配网络,两个收发机置于合路端口.图14a所示为12层PCB板,第7到12层用于放置天线.在天线阵列里采用了2×2的小阵列,即次级阵列,可实现较好的交叉极化性能.

图13 双极化双波束5G相控阵[34]Fig.13 2 × 64-element dual-polarized dual-beam 5G phased-array[34]

图14 PCB堆叠结构(a),收发机系统结构(b),芯片照片(c)[34]Fig.14 Stacked-up PCB structure (a),systen diagram of the transceiver (b),and chip micrograph (c)[34]

该收发机芯片采用0.18 μm SiGe BiCMOS工艺制造,工作频率为28~32 GHz.接收机的噪声系数为4.8 dB,输入1 dB 压缩点为-21 dBm,单芯片功耗为163 mW;发射机的输出1 dB压缩点在11~12 dBm之间,压缩点处单芯片功耗为228 mW.2×2多输入多输出阵列测试时,64-QAM调制方式下的空口传输速率可达2×30 Gb/s.

前文提到的由东京工业Wang等[20,35]研发的收发机也集成了天线.图15为PCB的正反面,该封装采用了16个芯片收发机,天线阵列则采用了64阵列,一个芯片对应4个天线,极化方式为单极化.

2 毫米波雷达进展

随着半导体技术的快速发展,极大地提升了硅基工艺晶体管的截止频率,硅基毫米波雷达成为研究热点.近3年来,在调频连续波(FMCW)雷达[36-39]、相控阵雷达[40-42]方面以及支持多种模式的毫米波雷达[43]等方面取得了较大的研究进展.

2.1 毫米波FMCW雷达

2018年,德国航空航天中心的Jeon等[36]发表了一种同时输入正交波形的多输入多输出(MIMO)雷达系统.该系统工作在W波段,频率范围是93.5~94.5 GHz,带有调频连续波(FMCW)信号,主要优势为拍频(beat)信号的带宽远小于传输带宽,可以大大降低采样要求.如图16所示,系统由收发机、天线和信号处理器组成,其中收发机包括两个发送通道和两个接收通道.在93.5~94.5 GHz的频率范围内,收发机通道1的发射功率范围是18.49~19.25 dBm,通道2的发射功率范围是18.06~19.31 dBm,两通道的接收功率都高于18 dBm.可以看出,发射机具有较高的发射功率,可在100~150 m范围内对小雷达反射截面物体检测成像.在1 kHz频率偏移下,该收发机发送路径的相噪低于-80 dBc/Hz,接收路径的噪声系数为19 dB.两通道间的隔离度为39 dB.该系统设计并采用了紧凑型喇叭天线和高数据采样率的两通道模数转换器(ADC).利用拍频分割(BFD)产生四组同时发送的正交波形,通过获取不同信号路径的一维距离像(range profile)对雷达系统的MIMO能力进行测试.实验结果表明,所有距离在100 m范围内的目标都能够被检测到.对目标的脉冲响应进行分析,距离分辨率(range resolution)峰值为0.15 m,满足范围分辨力和检测范围的要求,表明该雷达系统可以适用于高分辨率成像应用.但该系统为了实现收发机不同通道之间的波形分集,每个发射通道将使用不同的输出频率配置,需要多个锁相环(PLL)来生成不同输出频率的发射信号或通过数模转换器(DAC)来调制发射通道中FMCW啁啾信号上的数字偏移信号,系统设计较为复杂.

图16 同时输入正交波形的MIMO雷达系统[36]Fig.16 The W-band MIMO FMCW radar system based on quadrature input[36]

2020年,清华大学微电子研究所的Ma等[37]发表了一款基于混合模式锁相环啁啾发生器的雷达收发机,工作频率范围为76~81 GHz,系统结构和芯片照片如图17所示.该雷达集成了两个发射机(TX)和三个接收机(RX),可实现MIMO工作模式,并且具有可重构环路带宽和倍频方案的38.5 GHz混合模式锁相环(PLL)用于生成可重构FMCW线性调频波形.该雷达采用了粗精细电流DAC用于支持具有快速频率下降能力的锯齿FMCW线性调频,并且还用基于延迟锁定环(DLL)的延迟时间校准改善了嵌入式2-D游标时间-数字转换器(TDC)的线性度.无源下变频用于提高RX线性度,以防止TX泄漏和短程干扰,提出了一种底部开关吉尔伯特型调制器来实现双相调制,并采用磁耦合谐振器技术有效扩展链路带宽.

该FMCW TRX能生成可重构的线性调频脉冲,其带宽为0.25~4 GHz,周期为0.03~10 ms.对于具有4 GHz带宽和300 μs周期的锯齿状线性调频,均方根(RMS)频率误差为110 kHz.TX的最大输出功率为13.4 dBm,通过调节可低压差稳压器(LDO)电压可以实现3 dB的调节范围.RX在600 kHz中频时可达到15.3 dB的噪声系数和-8.5 dBm的输入1 dB 压缩点.当雷达收发机全开时,总功耗为921 mW,芯片照片如图17b所示.基于所提出的TRX芯片,开发了原型硬件和数据处理算法.实时实验结果表明,所获得的MIMO雷达的距离和角分辨率分别为5 cm和9°.

在2020年的ISSCC上,麻省理工的Yi等[38]采用65 nm CMOS工艺实现了一款带宽达到100 GHz的FMCW梳状雷达,如图18a所示,可以看到100 GHz的带宽被分为了5段,每一个20 GHz.使用具有相等间隔的载波频率(梳状)的收发器阵列(信道)同时扫描这些段,每个收发器都有自己的天线,接收的回波信号与发送的信号混合在一起以产生IF输出.该雷达具有1.5 mm的分辨率,最小噪声系数为22.8 dB,多通道汇总EIRP为0.6 dBm,峰值接收机增益为22.2 dB.由于采用了梳状结构,在100 GHz带宽内的发射机输出功率波动为8.8 dB,接收机噪声系数波动为14.6 dB,梳状结构有利于压制这两个性能波动.距离分辨率为1.5 mm,功耗为840 mW.芯片照片如图18b所示.

2.2 毫米波相控阵雷达

如上文所述,随着多通道相控阵收发机集成电路的发展,其应用也从通信领域扩展到雷达方面.

在2020年Very Large Scale Intergration(VLSI) 会议上,清华大学的Deng等[40]发表了用于FMCW相控阵雷达收发机的发射机和接收机前端,工作频率为35 GHz.收发机采用CMOS 65 nm工艺制造,如图19所示.虽然典型的FMCW相控阵雷达收发器在TX和RX前端都使用RF路径相移方案,但Deng等[40]介绍的Ka波段TX和RX前端是专为TX模拟和RX数字波束形成相控阵列雷达系统,并研究了Ka-band相控阵雷达收发器的链路预算.为了提高TX输出功率电平,引入了具有四路功率分配/合成器的功率放大器(PA),对功率放大器的详细分析和设计考虑进行了研究,提出的TX和RX前端采用1P9M 65 nm CMOS技术实现和制造,测得的TX输出功率为19 dBm,达到了迄今为止使用CMOS技术在Ka波段上输出功率最高的FMCW模块.RX实现了最高达到29.6 dB的转换增益.TX占用1.42 mm2面积,消耗588 mW功耗.RX面积为0.59 mm2,消耗72 mW功耗.

图19 35 GHz雷达收发机前端的发射机(a)和接收机(b)[40]Fig.19 Die photograph of the 35 GHz radar front end,transmitter (a) and receiver (b)[40]

随后在2020年的11月,新加坡南洋理工大学的Tang等[41]实现了一款四收四发的啁啾相控阵雷达收发机并发表在了JSSC上,可应用于X波段合成孔径雷达.该收发机采用65 nm CMOS工艺制造,如图20所示,在单个CMOS芯片上实现了波束控制/波束赋形功能.该芯片级雷达TRX由4个发射器(TX)和4个接收器(RX)组成,它们的中心工作频率为10 GHz,带宽为1 GHz.为了实现具有精细角度步进的宽带波束转向,在TX里提出了两级延迟控制.在延迟控制里使用基于延迟锁定环(DLL)的多相合成器(MPS)来控制基带啁啾的粗实时性.在射频(RF)路径中用有源移相器(PS)精调相位.在1.2 V电源下每个通道消耗228 mW的功率,可提供约10.2 dBm的功率,纹波小于1.3 dB.延迟线测试表明,在1 MHz/μs的线性调频速率下,经过消减后的信号达到了-13 dB的峰瓣旁瓣比(PSLR),相位相干误差在±1.2°以内.该工作演示了相控阵雷达TRX原型样机,天线阵由具有8 dBi增益、6 GHz带宽的Vivaldi天线组成,天线排列间隔6 cm.实验结果表明,光束转向/波束形成达到了±60°,步距约为1°.基于TX中的两阶段波束控制和RX中的数字波束形成进行了SAR成像实验,验证了相控阵雷达TRX原型机在SAR成像应用中的能力.

图20 芯片照片和测试PCB板[41]Fig.20 Die and chip on board micrograph and the test PCB[41]

近年来,除了常见的FMCW雷达和相控阵雷达的研究,也存在其他新颖的雷达设计.2020年,美国IBM T.J.Watson研究中心的Lee等[43]发表了毫米波多模式雷达发射机,如图21所示.这种多模式类型的雷达首次被详细的分析和设计,以激励多模雷达模块的进一步研究和开发.该雷达发射机工作频率在60 GHz频段,采用45 nm CMOS绝缘体上硅(SOI)工艺实现,同时集成了宽带三倍频、两级前置放大器、两个功率混频器以及混合信号基带波形生成电路.发射机雷达在多种模式下工作主要是通过配置功率混频器和相关的波形基带电路实现的.多模式主要支持三种关键雷达波形:1)连续波(CW/FMCW); 2)脉冲;3)均来自单个前端的调相连续波(PMCW).并提出了一种基于电流重用拓扑的新颖宽带频率三路复用器设计技术,以用于产生输出分数带宽大于59%的LO.

图21 毫米波多模式雷达发射机的多模发射机架构(a)和芯片照片(b)[43]Fig.21 Multi-mode millimeter-wave radar transmitter,architecture (a) and chip micrograph (b)[43]

测试结果表明,在连续波模式下,完整发射机在晶片上测量结果显示,从54到67 GHz的平均输出功率为12.8 dBm,峰值功率为14.7 dBm,谐波抑制比大于27 dB.脉冲模式下的测量表明可编程脉冲宽度为20到140 ps,转换对应为大于 40 GHz的雷达信号带宽.PMCW工作模式在使用10 Gb/s PRBS调制雷达信号也得以验证.总功耗为0.51 W,占用面积2.3 mm×0.85 mm.

3 结束语

近年来,基于硅基的毫米波通信和雷达收发前端集成电路取得了飞速的进步,在性能不断突破的同时,毫米波收发前端的架构也在不断优化.同时,由于硅基工艺低成本、易集成的巨大优势,硅基毫米波收发前端电路与天线融合设计与封装集成、基带数字电路的SOC系统化设计成为当前的发展趋势.