基于JESD204B协议的多板卡同步采样设计与实现

2021-09-25张松柏

孙 磊,张松柏

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

数据采样系统被广泛应用于雷达、声纳、射电天文和医疗成像等探测领域,为满足这些领域对高精度探测的需求,通常通过扩展阵列孔径(即增加数据通道)来提高分辨率。然而在实际工程应用中,由于制造工艺的偏差,2个以上数量的通道采样序列通常会在时间上存在不同步现象,具体表现为具有不一致的时延。这种采样不同步问题将导致后端信号的相参处理性能恶化甚至失效。

为解决2个以上数据通道的同步采样问题,国内多家高校和科研院所,基于JESD204B同步传输协议,验证了单板双通道、4通道和8通道的同步采集性能[1-4]。随着通道数的进一步增加,受限于印制板尺寸,所有的数据采样通道将不可避免地被分布在多块印制板卡上,相较于单板内的短距离数据传输,板卡间的数据传输距离更长,增加了多板卡上模数转换器(ADC)同步采样的难度。

为解决多板卡带来的采样不同步的难题,文献[5]给出一种主从板卡的设计架构,由主板卡提供相参时钟给从板卡,从而保证2块板卡的采样具有相参性。然而,这种主从板卡的架构设计,只适用于采样通道较少的应用领域,不具备扩展性。为扩展更多的板卡参与同步采样,文献[6]通过引入时钟扇出电路来满足更多数量板卡的时钟需求。但大量的板间时钟电缆增加了硬件设计系统的复杂程度。

本文针对现有设计的不足,根据实际项目需求,提出了一种基于JESD204B协议的多板卡同步采样设计。基于JESD204B协议的子类1模式,实现单印制板内的多通道同步采样。通过外部等长输入的同步脉冲确定所有采样板的起始采样点。采样点内的相位偏差则通过调整输入相参时钟的延迟参数来进一步减少。通过对实际硬件采样的数据进行分析,验证了本设计的可行性和有效性。

1 设计实现

设计采用了8块ADC采样板+1块数据接收板的架构设计,该架构可通过增加采样板卡数量来扩展采样通道,且各ADC采样板卡能够互换,便于验证可扩展性测试。为实现多板卡的同步采样,本设计通过2个步骤来建立全部通道的同步。第1步是基于JESD204B协议,实现各个印制板板内8个通道的同步采样;第2步通过数据接收板扇出到8块采样板的相参时钟和同步脉冲,实现所有64个通道的同步采样。

1.1 JESD204B协议

JESD204B协议是用于连接模数/数模转换器(ADC/DAC)和逻辑器件之间、逻辑器件和逻辑器件之间[7]的一种串行接口协议。相较于传统的低压差分信号(LVDS)并行接口协议,JESD204B协议的速率带宽高达12.5 Gb/s,且数据管脚更少,是新型高速ADC/DAC的首选传输协议。从研发的角度出发,JESD204B协议规定在数据流中插入特定的加扰和界定字符,增强了数据传输过程中的鲁棒性,同时简化了接收端的串并转换逻辑设计。此外,现有Xilinx 公司的JESD204B IP核可通过AXI4-Lite接口对JESD204B协议进行动态的读写配置,便于对整个传输链路的状态监测。

1.2 板内同步设计

板内多通道ADC的同步设计,是基于JESD204B协议的子类1模式进行的设计,其设计框图如图1所示。JESD204B协议的子类1模式需要2类时钟:器件时钟(Device CLK)和系统参考时钟(SYSREF CLK)。其中器件时钟是ADC和现场可编程门阵列(FPGA)的工作时钟,彼此独立,可以工作在不同的频率。系统参考时钟是ADC和FPGA间JESD204B协议的同步基准,保证传输链路收发两端的同步工作,是板内多通道ADC的同步设计的关键部分。后面为描述方便,将器件时钟和系统参考时钟一起称作JESD204B时钟对。

图1 AD采样板板内同步采样设计框图

为实现板内基于JESD204B协议的同步传输,外部相参时钟经时钟管理电路,分别往ADC和FPGA扇出JESD204B时钟对。印制板设计中,所有的JESD204B时钟对都要求等长设计,从而保证所有的ADC通道到FPGA的同步传输。为满足系统参考时钟对器件时钟的建立和保持时间要求,设计中通过降低系统参考时钟的频率,增加高电平的持续时间,从而便于器件时钟捕获系统参考时钟[8]。

1.3 板间同步设计

在实现板内ADC同步采样后,这里提出一种基于同步脉冲的多板卡同步设计,原理框图如图2所示。图中,所有采样板的同步采样设计,由数据接收板扇出至各采样板的同步脉冲和相参时钟实现。同步脉冲的等长设计,保证板间的采样误差在一个采样周期内。而采样周期内的误差,则通过计算各通道相对于参考通道的时延误差,再调整对应相参时钟的延迟,来进一步提高对应通道的同步性能。

图2 板间同步设计框图

其中,时延误差的测量,可通过采样单频点信号,并计算采样数据的自相关和互相关来实现[1,9]。

设给定单频点信号s(t)=Asin(2πft+φ),其中A为信号振幅,f为信号频率,φ为初始相位。对应通道k的采样数据sk(n)为:

sk(n)=gkAsin(2πf(nTs+Δtk)+φ)+οk

(1)

式中:n为采样点数,n=1,2,…,N;k=1,2,…,64;gk为通道k上的传输增益;Δtk为采样信号传输延迟,不失一般性,这里将通道1设为参考通道,即Δt1=0;οk表示采样通道k的偏置误差。

根据采样数据计算各通道k的偏置误差:

(2)

(3)

得到通道k的时延误差:

(4)

根据计算出的时延误差,通过调整数据接收板上相参时钟扇出电路对应时钟的延迟参数,即可实现通道k和通道1的同步,最终实现所有通道的同步采样。当然,这里的同步存在一定数值范围内的时延误差,其误差精度取决于时钟扇出电路上固定的模拟延迟步长,以及可调的数字延迟步长设计。

相较于现有文献给出的JESD204B时钟对扇出设计,本文用同步脉冲信号来替换系统参考时钟,避免了将JESD204B时钟对扇出到各个板卡的硬件设计需求,同时减少了一半的时钟数量需求,工程上简化了电缆的传输空间。

2 性能验证

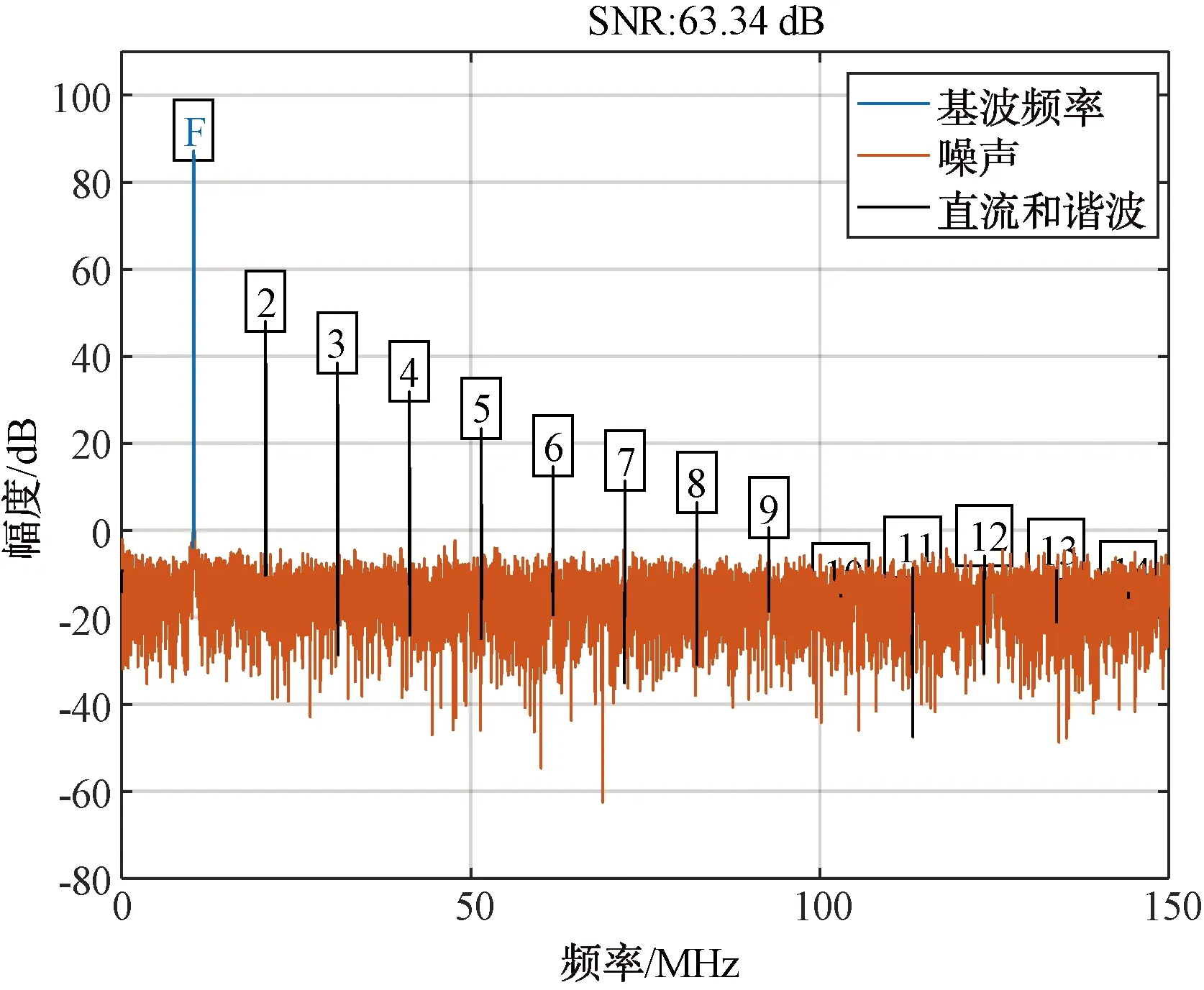

性能测试包含两部分:AD采样性能和多板卡的同步性能。为简化分析,实验选取了采样板1上通道1(k=1)和采样板2上第2个通道(k=10)的采样数据,用于计算通道1的ADC的信噪比(SNR)指标,以及2个通道的板间时延误差。两部分实验的采样频率fs都为300 MHz,采样点数N=16 384。

2.1 ADC性能

实验中通过对通道1上ADC采样通道的数据进行信噪比计算,验证AD电路的采样性能。分别给定f=10.3 MHz和f=305 MHz的正弦信号,并确保信号满量程输入。将2次采样数据分别导出,用Matlab工具进行分析,其结果如图3和图4所示。

图3 10.3 MHz信号的采样数据频谱

图4 305 MHz信号的采样数据频谱

图3和图4中,在剔除直流和各次谐波成分后,计算出信噪比分别为63.34 dB和61.71 dB,设计指标满足实际要求。

2.2 同步性能

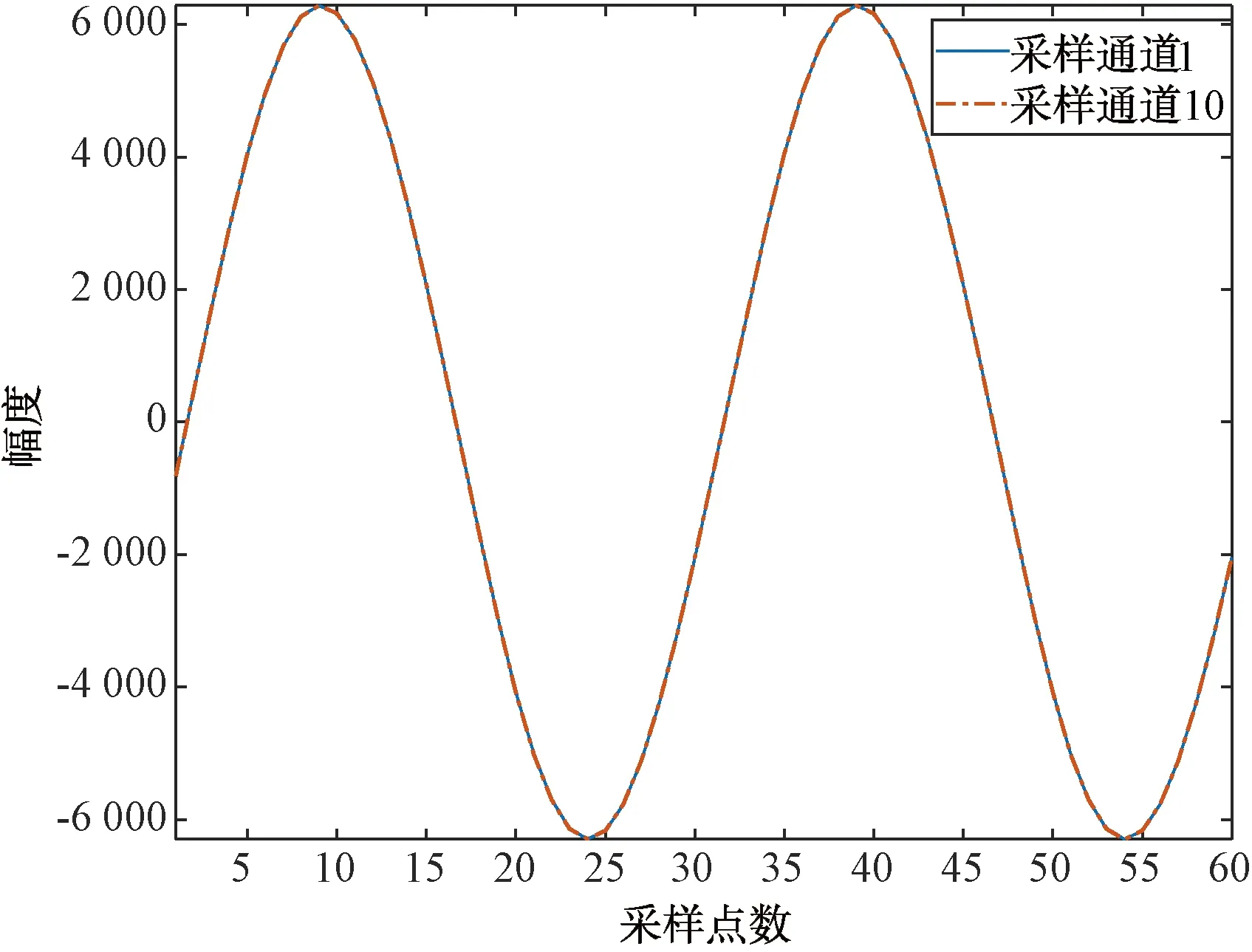

通道间的采样同步性能,在时域上表现为采样数据在一个采样点内的相位偏差,甚至是相差1个或多个采样点。基于本文的架构设计,所有采样板将板内通道的采样数据通过光纤链路送至数据接收板。为验证多板间的同步性能,将信号源输出频率f=10 MHz的点正弦信号通过功分器扇出同轴电缆,连接至采样板1的第1个采样通道和采样板2的第2个采样通道。

将2个通道的采样数据导出,根据式(4),计算出Δt10=1.73 ns。为直观显示,图5给出了2个通道同时刻的60个采样数据。从图中可以看出,此时通道10与参考通道(通道1)在时域上存在不同步现象,有个时延误差。

图5 相参时钟2调整前的采样数据波形

接着,根据计算出的时延误差值,通过调整数据接收板上相参时钟2的模拟和数字延迟,再次触发采样,得到如图6所示2个通道同时刻的60个采样数据波形,经计算得到时延误差Δt10=17.2 ps。

图6 相参时钟2调整后的采样数据波形

从图6可以看到,通过调整相参时钟2的延迟参数,两通道的采样数据实现了重叠,实现了同步采样。不失一般性,这种同步方法可扩展到其他采样板上的采样通道上,从而实现所有通道的采样同步。

3 结束语

本文通过分析现有多通道同步设计方案的不同,基于实际工程需求,提出了一种板内基于JESD204B协议,板间基于同步脉冲和相参时钟的多板卡同步采样设计。相较于现有方案,所提设计具有很好的通道扩展性,减少了一半数量的时钟电缆连接。通过对实际采样数据的分析和计算,验证了所提设计的可行性和有效性。