基于DMA的XVC协议性能优化

2021-09-25刘剑,赵赟

刘 剑,赵 赟

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

现场可编程门阵列(FPGA)远程调试由于不受调试线缆传输距离的限制,大量学者近年来对其在船舶、核实验等工况环境下的应用展开了研究[1-4]。赛灵思虚拟电缆(XVC)[5]协议是一种基于TCP/IP的网络通信协议,适用于FPGA远程JTAG接口加载与调试,薛等[6]基于ARM单芯片实现了XVC协议的多目标FPGA菊花链式远程网络调试,但其JTAG加载性能较差。随着可编程SoC和AXI总线标准的快速发展和应用,李[7]和薛[8]分别采用软核和硬核可编程片上系统(SoPC)实现了AXI转JTAG方式的XVC远程调试,SoPC远程调试系统相较于ARM进一步提升了远程调试的加载性能。但目前XVC远程调试方案在FPGA加载速度和效率方面普遍仍低于传统JTAG线缆,这限制了XVC协议在大容量、多目标FPGA远程调试和加载方面的进一步推广和应用。

本文从基于SoPC的XVC协议性能优化方面开展研究,提出一种改进型JTAG转换器结构,引入AXI-DMA[9]和非阻塞IO传输机制,提高XVC协议的JTAG数据转换速率,最终得到性能优化的FPGA远程调试系统。

1 系统结构

基于ZYNQ硬核SoPC构建XVC远程网络调试系统,系统结构如图1所示。ZYNQ SoPC用于远端目标FPGA的JTAG接口控制,其可编程逻辑(PL)部分用于构建XVC协议专用JTAG数据转换器,具有逻辑加速的特性,并通过处理器系统(PS)的高性能(HP)从机AXI总线接口,JTAG-DMA转换器主动地执行高效率数据传输;在以ARM处理器为核心的PS部分,Linux内核模块管理PL端JTAG转换器的DMA读写驱动,XVC服务器软件适用于操作JTAG-DMA设备进行多目标FPGA的JTAG信号同时传输;本地计算机与ZYNQ SoPC通过以太网-局域网互联,XVC客户端以点对点或交换的方式连接远端XVC服务器下特定端口,对指定的目标FPGA进行远程加载与调试。

图1 XVC远程网络调试系统结构

XVC远程网络调试系统适用于多目标FPGA、多设备节点场合下的多人协同远程调试和开发,可通过网络长距离布线远离调试设备环境。

2 XVC协议性能优化

2.1 JTAG-DMA转换器

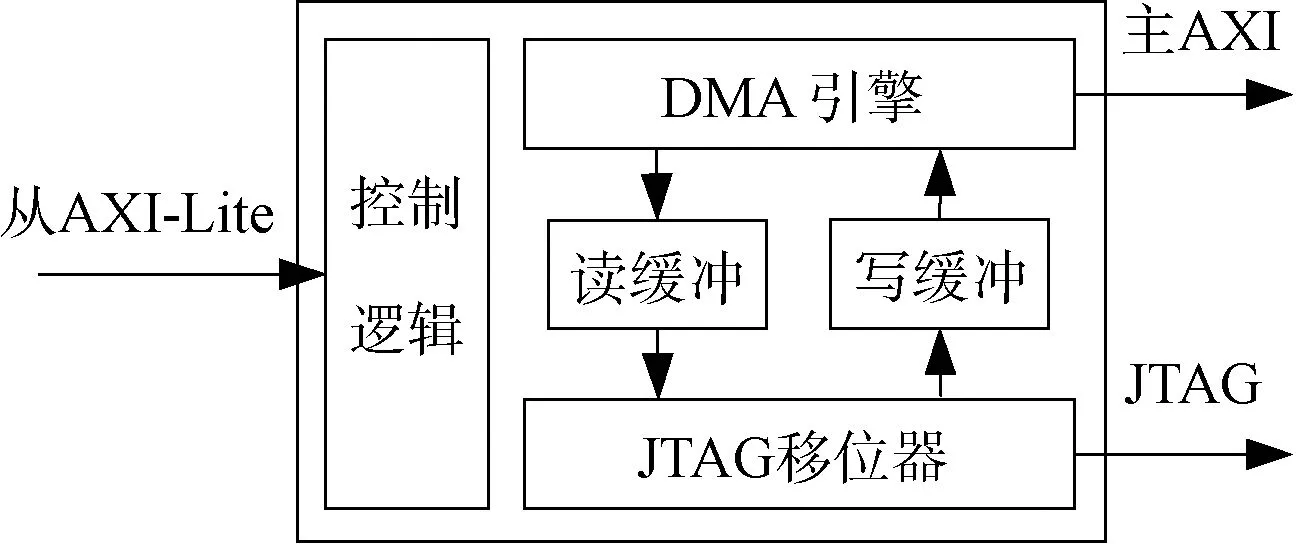

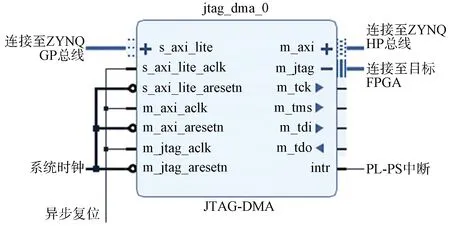

提出的改进型JTAG转换器结构如图2所示,典型JTAG转换器仅由JTAG移位器和控制逻辑组成,JTAG数据均由处理器通过AXI-Lite总线进行搬运。通过引入DMA引擎,提出的改进型JTAG转换器将JTAG数据搬运事务转由转换器内部DMA逻辑进行控制。在JTAG数据传输效率方面,AXI总线位宽和突发传输长度可变,相比于AXI-Lite总线传输带宽和传输效率更高;DMA引擎可以直接通过AXI总线读写共享内存,降低处理器在数据总线上的占用率,提高JTAG数据的传输速度,进而提高JTAG转换器的转换效率。

图2 JTAG-DMA转换器结构

2.2 JTAG数据传输模型

改进型JTAG转换器执行1次JTAG数据转换,其流程为控制字传输,JTAG数据传输和JTAG移位转换,时序如图3所示。改进型JTAG转换器将控制字传输与JTAG数据传输分离,由控制字指定数据阶段的目标/源地址、传输位长等参数,并启动JTAG转换;在转换过程中JTAG数据由DMA引擎进行AXI主动传输控制,JTAG移位器在启动前将JTAGTMS和TDI数据由内存搬运至移位器中,完成JTAG移位后,回读的JTAG TDO数据由DMA从移位器再搬运回指定内存地址。

图3 JTAG转换时序

AXI总线一次读写突发数不能超过256,同时其传输字节长度也不能超过4 kB寻址范围,单次JTAG最大转换比特数受限于AXI总线传输量。考虑到AXI总线读写时间会占用一部分单次转换时间且该时间在高速JTAG下不可忽略,这影响到总JTAG转化效率。在AXI-DMA与JTAG移位器之间加入读写缓冲区,可将单次JTAG数据长传输微分为N个多次JTAG数据短传输,其读写时序如图4所示。Rx表示AXI-DMA从指定内存地址取JTAG TMS和TDI数据,rx表示读缓冲区内容更新,Sx表示第x次JTAG移位器移位,Wx表示JTAG回读数据向写缓冲区写入,wx表示AXI-DMA将写缓冲区的JTAG TDO数据写入内存。读写缓冲区的引入使得单次JTAG长传输不受到AXI总线读写量的影响,可提高JTAG单次传输长度和JTAG数据转换效率。

图4 JTAG转换器长传输读写时序

在第x次的JTAG短传输中,短传输开始时更新读缓冲区rx,同时开始上一次短传输的写入wx-1和下一次短传输的预读Rx+1,短传输过程中JTAG TDO的回读数据直接写入缓冲区Wx。基于AXI-DMA的改进型JTAG转换器,单次转换的JTAG比特转换效率理论值为:

(1)

式中:Ns表示JTAG移位个数;fTCK表示JTAG TCK频率;ts为JTAG短传输转换时间,ts=Ns/fTCK;tc表示AXI-Lite总线控制字传输时间;tR表示AXI总线读时间;tw表示AXI总线写时间。

当JTAG总移位数足够大时,AXI总线读写时间在总转换时间中仅为一次短传输读写时间,可忽略不计,理论JTAG效率接近100%;JTAG短传输移位时间必需大于AXI总线读写所需时间之和,以保证短传输过程中AXI总线数据正常传输。

2.3 内核驱动模型

在远程网络调试系统下,以太网传输可能产生网络阻塞、丢包、并发等情况,XVC协议在传输包解析过程中会产生连续的IO请求。在内核模块中JTAG转换器设备驱动需实现非阻塞式读写,以用于应用层连续读写请求的及时响应,消除连续IO请求引起的外设读写阻塞行为。

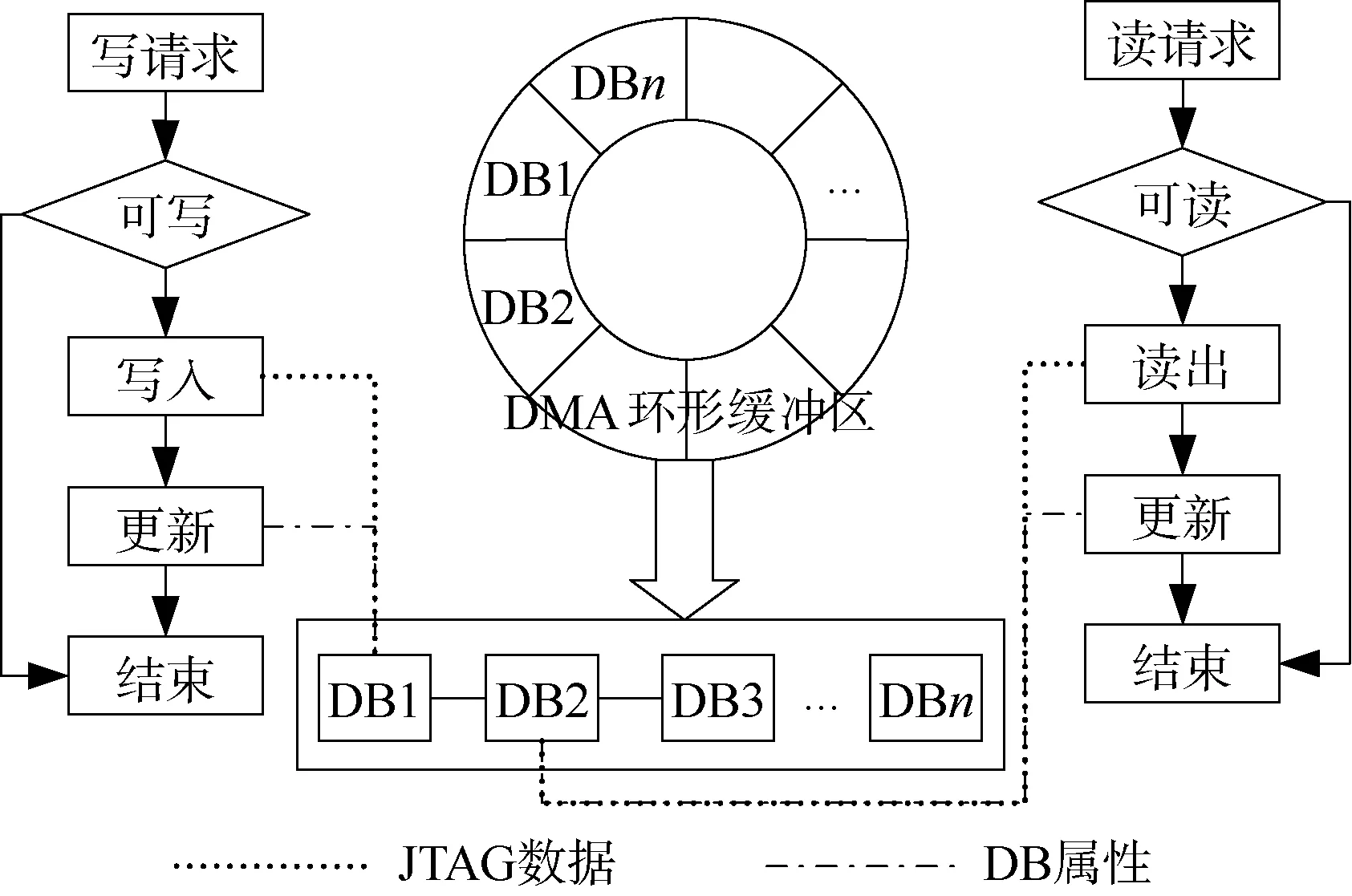

考虑到JTAG-DMA转换器的DMA传输机制,采用基于DMA环形缓冲区的非阻塞IO驱动模型,IO请求处理框架如图5所示。DMA池是为JTAG-DMA转换器分配的固定物理内存空间,由多个DMA块(DMA Block,DB)组成,并为每一个DMA块指定可读、可写和忙属性,对应内核中状态机跳转和JTAG转换器控制字管理。产生读写请求时,首先检查DMA块是否可读可写,写操作时将JTAG数据拆分并重新打包拷贝至DMA块,读操作时将DMA块数据拷贝出来组包为JTAG回读数据,并更新DMA块属性,立即结束读写流程。

图5 JTAG-DMA驱动IO请求处理框架

JTAG-DMA转换器内核设备驱动的非阻塞传输机制适用于多目标JTAG设备、连续IO的应用条件,提高XVC协议JTAG数据包转换效率和传输可靠性。

3 加载试验

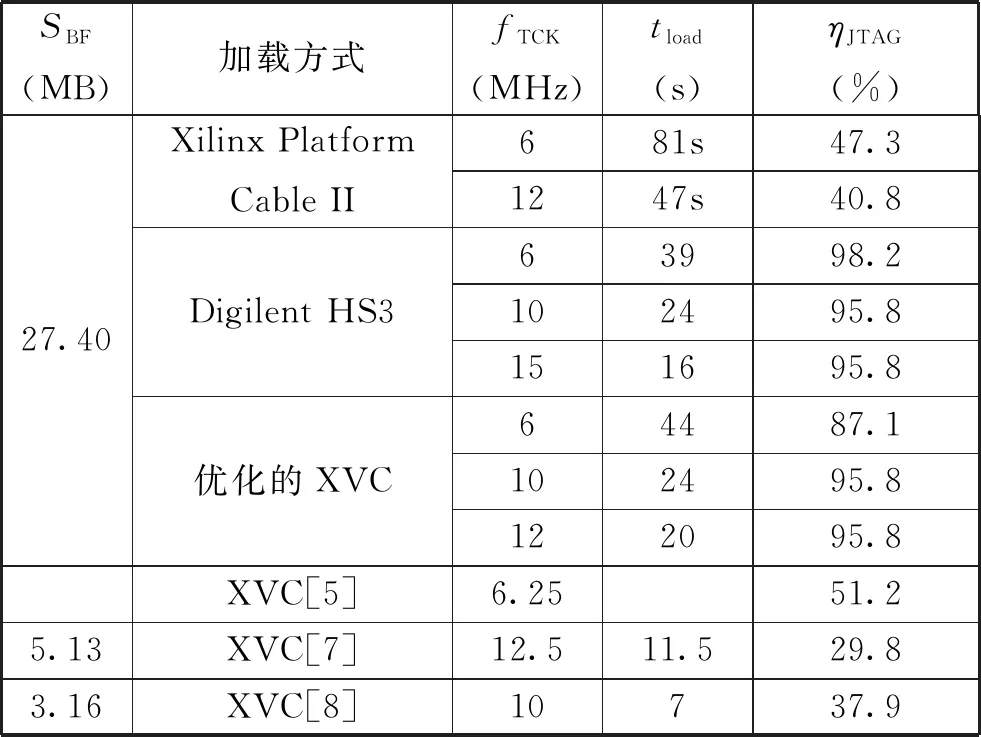

根据提出的XVC协议优化方法,搭建FPGA远程调试系统,并采用课题组研制的预处理板[10]实施FPGA位流加载实验。测试软件平台为Vivado 2019.1,图6展示了预处理板ZYNQ SoPC硬件平台下设计的JTAG-DMA IP核;测试目标FPGA芯片为Xilinx Virtx7 690 T,并使用JTAG线缆(Xilinx Platform Cable II和Digilent HS3)加载同一位流文件进行测试,测试结果如表1所示。实际JTAG比特效率为:

表1 位流文件加载测试结果

图6 JTAG-DMA IP核

(2)

式中:SBF表示目标FPGA比特流文件大小;tload表示实际加载时间,由Vivado控制台日志信息得到。

4 结束语

本文提出了一种基于AXI-DMA的改进型JTAG转换器结构,并引入基于DMA环形缓冲区的非阻塞IO驱动模型,用于优化XVC协议JTAG转换效率。实验结果表明,优化后XVC协议的加载性能相比于典型XVC远程调试系统有巨大的提升,其JTAG比特效率超过或可达到JTAG线缆的性能。