一种数字化多相信道化接收机的设计

2021-09-23王力

王力

(四川九洲电器集团有限责任公司 四川省绵阳市 621000)

随着信息技术的快速发展,频谱资源的利用越发紧密,数字信号传输通道要求具备有宽频率覆盖范围,较高的灵敏度,实时信号处理等特点[1],引入数字信道化技术将信号信道化处理可以有效解决这个问题[2]。

待侦查、探测的信号通常具有信道数量多、信道带宽较宽的特点,设计良好的数字化接收机可以有效的缓解信号处理时运算量偏大的的压力,因此,本文通过改进现有的信道化接收机,将一个高阶的原型滤波器用多个低阶的滤波器替代,阐述了一种数字化多相信道化接收机的设计方案。

1 基于多相滤波器组的信道化接收机

数字信道化可使高速信号分成并行的多路低速率数据进行处理,每个支路的输出都是对应在输入信号宽带内的不同中心频点的窄带子信号,将大带宽的信号转换为多个小窄带的信号进行处理,可大大缓解高速信号实时处理的速度瓶颈[3]。其信道化接收机的基本模型如图1所示,用hLp(n)表示抗混叠低通滤波器,整个信道化结构的分支可以看做由某一分支复制后并联在一起构成。

设滤波器个数(信道数)为 K,抽取倍数为D,则满足K=F·D( F为正整数)的关系,且每一个子信道的中心频率是wk,k=0,1,...,K-1,其值由信道划分形式决定,通道划分通常包括偶数堆叠和奇数堆叠两种类型[4],其中偶型排列第k个信号的中心频率为奇型排列第k个信号的中心频率为且奇偶排列中两个临近的信道距离相同,都是

根据奇偶情况,对图1信道化结构进行多相推导,可得到不同情况下的数字信道化接收机的高效结构。信道偶数划分时第k个子信道的输出如下:

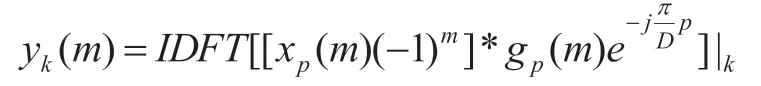

信道奇数划分时第K个子信道的输出为:

通过原型滤波器hLp(n)的多相处理,每一支路滤波器的阶数就只有原来滤波器阶数的1/K,减少滤波运算的累积误差,提高计算精度。通过以上推导,基于多相滤波器组的信道化接收机数学模型如图2所示。

2 设计仿真与分析

本文采用线性相位FIR低通滤波器,输入信号的模数转换的采样率取1024MHz,信道个数K=16,采取均匀的信道划分方式,每个子信道的覆盖范围为1024MHz/16=64MHz,按顺序对各子信道进行编号并将中心频率与信道编号对应,得到各信道中心频率为fk=64kMHz,频率覆盖范围为[64k-64, 64k+64]MHz(k=0,1,...,15)。现随机选取175MHz和465MHz的多频率信号作为输入信号,如图3所示。

将测试信号分别输入到改进的多相滤波器组信道化接收机和原有的信道化接收机中进行信号处理,得到图4所示的仿真输出,以及图5输出对比结果。

图1:数字信道化接收机基本模型

图2:多相滤波器组信道化接收机数学模型

图3:输入信号时域波形和频谱

图4:多相信道化仿真输出

图5:两种数字接收机输出对比

根据前面的分析可知,测试信号理论上应落在3号子信道和8号子信道,图4可以看出改进的多相滤波器信道化接收机输出与理论相符合。图5中用三角形表示原有信道化接收机的输出,用星号表示改进的多相滤波器组信道化接收机输出,从图中看出,两者输出结果完全相同,从而验证了改进后的基于多相滤波器组的信道化接收机的正确性。

3 结论

相比原型数字信道化接收机结构,本文推导出的多相滤波器组信道化接收机结构,可以有效地降低整体工作数据速率,更易于在FPGA上进行实现。通过引入多相滤波器组的改进方法,将高速串行数据转换为低速并行数据,从而获取信道数量较多的侦查、探测等信号的全部有效信息。