基于SoC的多轴驱控一体化平台设计*

2021-08-27何敏佳孙永平

何敏佳,孙永平,张 军

(1.广州数控设备有限公司,广州 510535;2.哈尔滨工业大学电气工程及自动化学院,哈尔滨 150001)

0 引言

目前,运动控制系统大多采用运动控制器+伺服驱动器的方式,运动控制器与伺服驱动器进行信息交互的方式主要为脉冲指令、工业总线、工业以太网的方式,其具有应用广泛、技术可靠等优点。但随着工业需求的发展,要求多轴运动控制产品具有小型化、低成本、高可靠性和灵活性[1]。采用传统的通信方式,伺服驱动与运动控制之间传输的信息种类有限,无法满足更多高性能运动控制算法的需求。

随着工业界的需求以及微电子行业的发展,采用FPGA和ARM 的架构芯片Xilinx ZYNQ 全可编程片上系统Sys⁃tem-on-Chip(SoC)被广泛应用在工业控制领域,其集成双ARM核和FPGA核,非常适合伺服驱动与运动控制高集成技术。

FPGA 已经广泛地应用于运动控制以及伺服驱动平台[2],通过FPGA高速运算能力实现伺服系统电流环运算,可以显著提升电流环带宽,进而提升整个伺服系统性能。对于电机驱动器来说要求其能实现高级的伺服算法[3-4],例如谐振抑制、末端抖动抑制、参数辨识提高伺服系统的性能以及可靠性。本文采用Zynq7020 作为驱控一体硬件控制核心芯片,一个ARM核完成多轴的位置环、速度环算法,同时可以完成伺服高级算法如谐振抑制、参数自整定、参数辨识等高级算法,另一个ARM 核完成多轴轨迹生成、人机交互、示教在线功能,集成的FPGA实现多轴硬件电流环协同控制,提高系统整体带宽[5-7],简化系统时序规划,实现多轴ns级同步精度以及机器人更精确的位置轨迹,相比于分布式结构的基于CiA402运动控制协议工业以太网的数据传输[8-9],驱控一体机内部数据通过共享内存以及高速内部总线的方式进行交换,可以达到Gb/s 级别,传输信息更加丰富,例如读取机器人各个轴的位置、速度、力矩,以及伺服控制核心算法识别出的惯量等信息,便于机器人建模,更好地完成机器人的运动控制、柔顺控制等算法,以及空间轨迹、人机交互等任务。同时,外部总线的减免,使得系统的体积和成本得到减小和降低的同时,提高了系统的可靠性。

1 基于Zynq-7020 SoC分析与设计

1.1 Zynq-7020 SoC控制系统结构

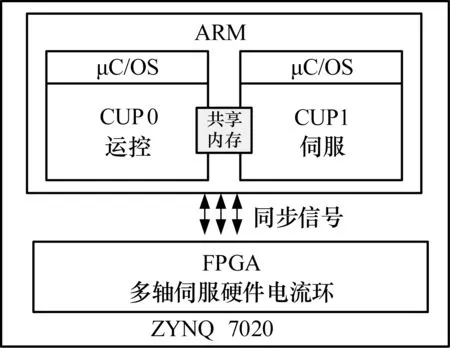

驱控一体机的框架如图1 所示。核心的主控制芯片采用目前市场上主流的Xilinx Zynq 系列SoC,集成了两个高性能ARM 芯片和FPGA 模块,用于取代传统的多DSP 控制器的分布式构架,避免复杂冗余的外部总线,缩小体积,提高可靠性。

图1 Zynq-7020多轴控制系统机构Fig.1 Architecture of the Zynq-based multi-axis control system

在伺服电机驱动反面驱动器方面,借助于FPGA模块,采用硬件电流环算法,在不增加算法整体复杂度的情况下,借助于FPGA高速并行运算能力,减少计算延时,显著提高系统电流环带宽。同时,考虑FPGA资源有限,为了实现多轴协同控制,采用时分复用算法,搭建流水线架构的多轴硬件电流环,以增加少量的计算时间为代价,使硬件资源占用量降低了一个维度。电流采样部分采用AD7401芯片,其为模拟转数字采样,方便FPGA进行采样处理,同时提高采样精度,编码器信号的协议解析同样也采用FPGA完成,便于时序的规划和信号的细分。涉及较多高级和扩展算法的位置环及速度环控制则由ARM芯片承担,便于程序的拓展和调试。

双ARM SoC中,一个CPU完成多轴的位置环、速度环和电流环的算法,同时可以完成伺服高级算法如谐振。另一个CPU完成交互功能、多轴轨迹规划等,SoC内部ARM和FPGA之间的信息交流则由高速内部总线和共享内存空间加以实现。Advanced extensible interface(AXI)进一步地利用驱控一体化实现驱控信息共享,根据系统的空间位置和伺服电机各种状态反馈,在线地调节系统各类参数,最大限度地优化机器人轨迹,减小轨迹误差。

1.2 Zynq-7020 SoC控制系统结构

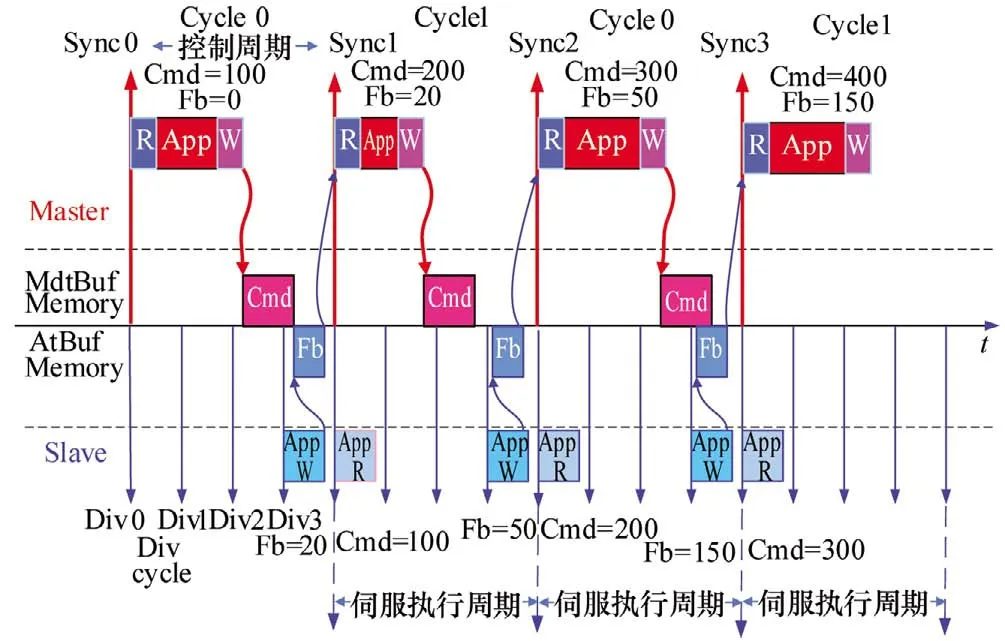

多轴驱控一体双核交互架构如图2 所示,双核数据交互为共享内存的方式,共享内存大小为64 kB,交互信息为实时信息,速度快且数据量大,为方便系统调度双核架构双核ARM 嵌入式系统μC/OS 嵌入式系统,可以实时调度系统资源加速度,本文双核交互数据包括位置、速度、负载力矩、负载惯量等信息。

图2 驱控一体化双核ARM数据交互架构Fig.2 Architecture of the dual core data interaction

双核交互数据时钟同步信号以及ARM 与FPGA 之间数据交互时钟由FPGA提供。双核交互数据采用经典的乒乓缓冲策略,如图3所示,伺服数据反馈区设置2个,数控指令区同样设置2个。防止数据双核数据读取的时候产生冲突,在周期0主机读AtBuf1,写MdtBuf0,从机读MdtBuf1,写AtBuf0,在周期1 主机读AtBuf0,写MdtBuf1,从机读MdtBuf0,写AtBuf1,通过数据缓冲完成双核交互运控与伺服数据内容的读写。

图3 双核兵乓缓冲数据交互Fig.3 Architecture of the dual core data interaction

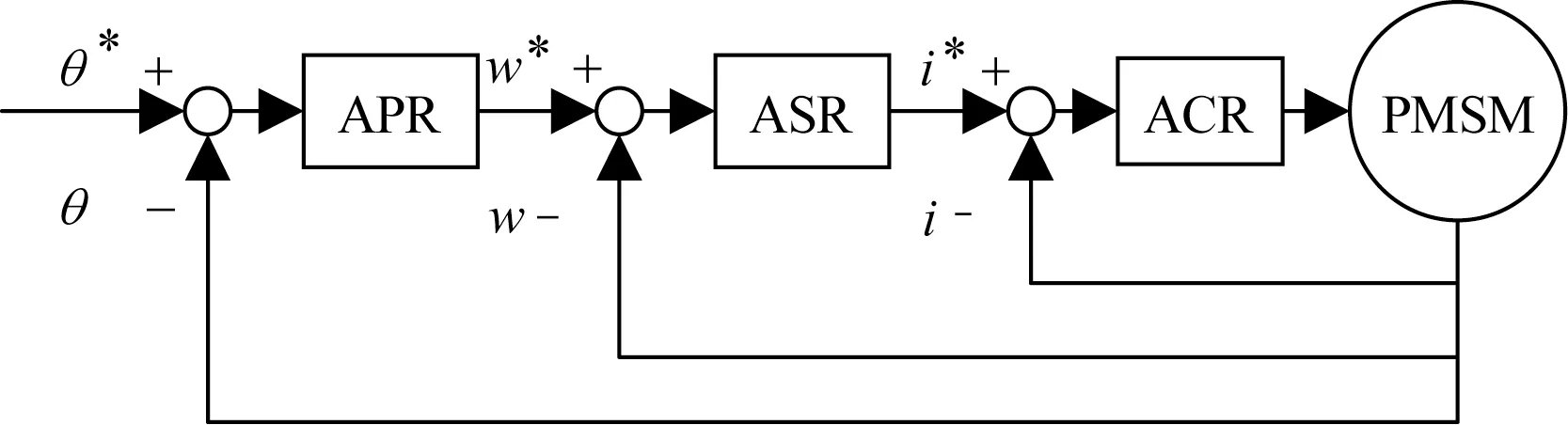

1.3 单轴伺服控制器结构

单轴控制系统控制框图如图4 所示。位置环采用比例控制器WAPR(s)=KP,速度环采用比例积分控制器,电流环采用比例积分控制器采用传动的控制策略,由于控制平台的优越性可以提高系统的性能。

图4 单轴控制框图Fig.4 Block diagram of the single-axis control system

2 多轴电流环控制器设计

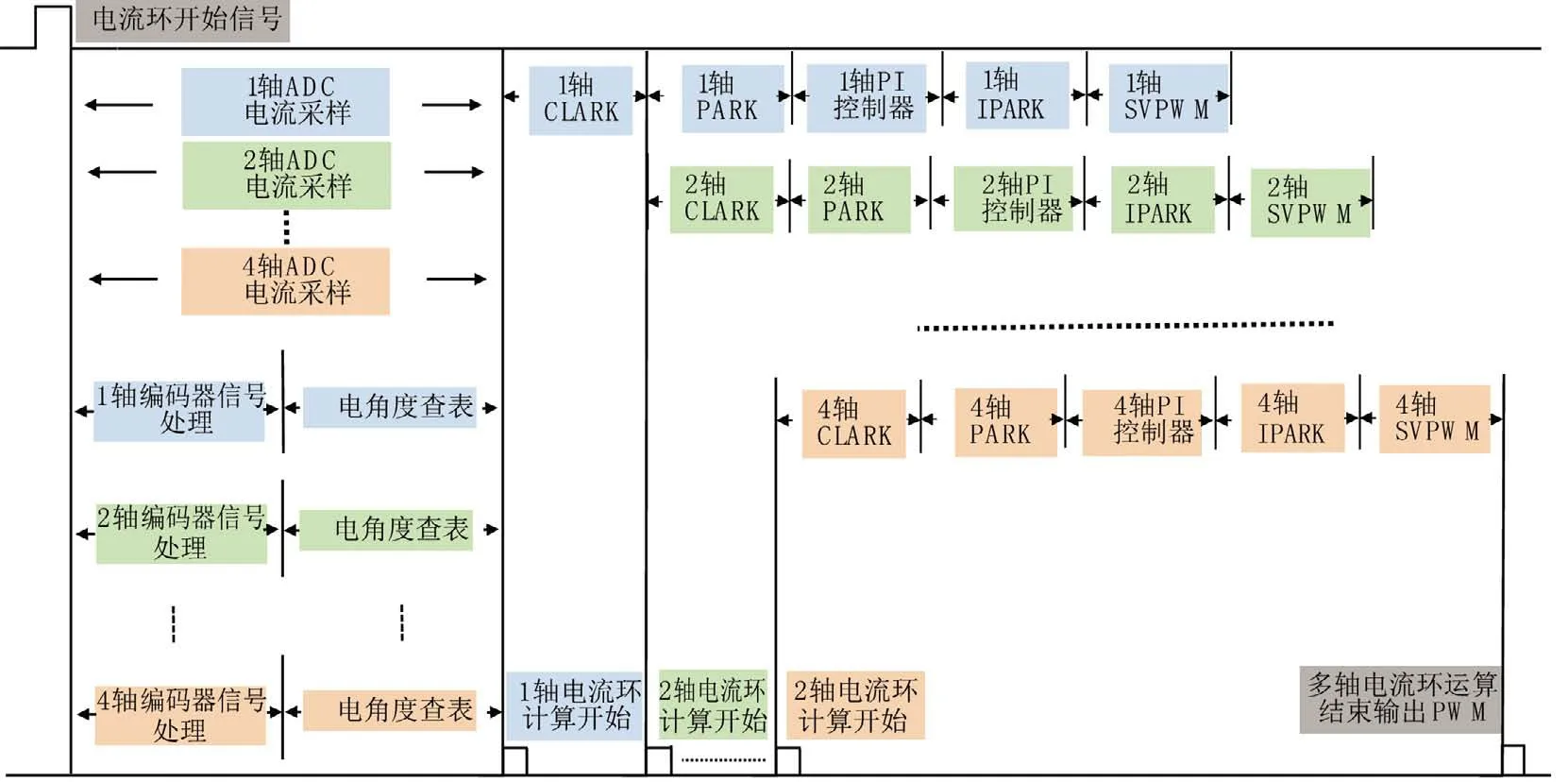

2.1 多轴流水线电流环控制策略

流水线结构的时序调度原理如图5 所示,在进行流水线电流环计算之前,FPGA 部分先进行4 轴电流环采样,得到4轴相电流信号。编码器得到6轴角度信号,通过查表法得到各轴正弦值、余弦值,按照时分复用的思想,要求同一功能模块在同一时刻只能进行某一个电机轴的控制运算,流水线电流环分为Clark 变换模块、Park 变换模块、PI 控制器、Park逆变换模块、SVPWM 调制模块。当1 轴的Clark 变换模块结束后启动1 轴的PARK 变换,之后进行1 轴的PI 控制器,接着进行PARK 逆变换,以此类推,直到启动SVPWM 运算模块对1 轴的运算,如果1 轴完成Clark 变换进行PARK 变换,则启动Clark 变换模块对2 轴的运算,直到完成SVPWM 运算。以此类推,直至完成4 轴电流环模块,然后进行PWM输出,这样可以保证多轴同步性、电流环快速计算性能,又可以节约FPGA资源。

图5 多轴流水线电流环Fig.5 Diagram of multi-axis current loop pipeline structure

2.2 基于FPGA双采样双更新算法实现

目前伺服驱动器主流的控制芯片还是以应用DSP 单采样单更新控制策略为主,但是由于DSP的运算特点,PWM零阶保持器以及数字延迟的影响,使得执行一次电流环需要时间较长,一般带来1.5 倍的电流采样延迟,限制了电流环的带宽,通过减少采样与运算延迟可以显著地提高控制器电流环带宽。

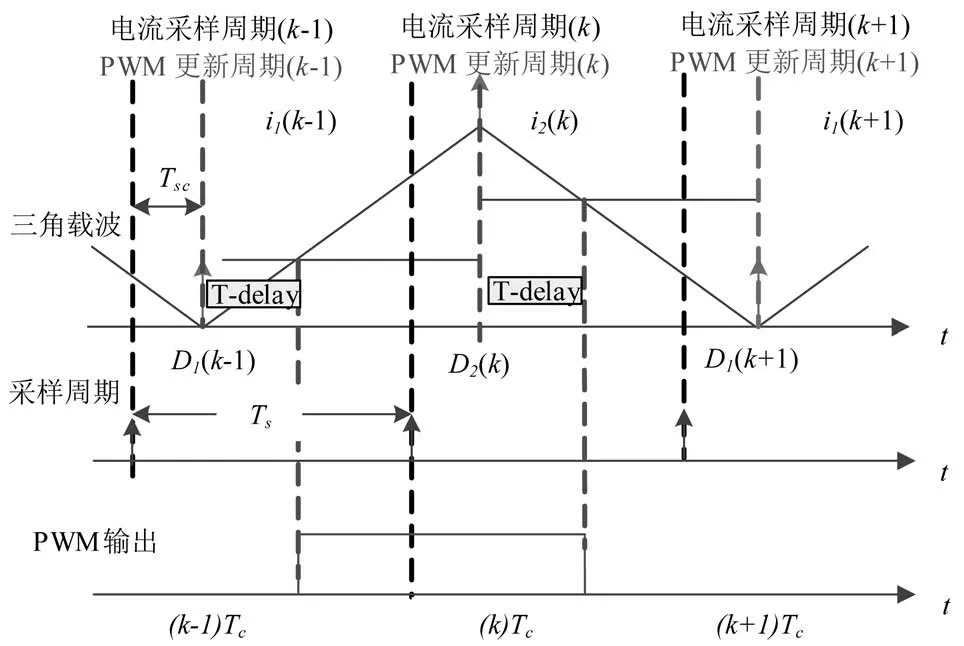

因此,近些来,基于FPGA电流环控制器的电机控制算法被广泛研究[10],由于FPGA具有快速的并行计算能力使得电流环运算速度非常快,可以控制在几十纳秒内完成,并且采样时间点和PWM更新点可以自由设置,其中较为经典的双电流采样和双PWM占空比更新时序如图6所示。图中Dm(k)为第k个周期内第m次PWM占空比更新,im(k)为第k个周期内第m次电流采样(m=1,2),Ts为电流采样周期,也表示电流环的运算周期,Tc为载波周期。对电流采样和PWM 占空比更新进行分时处理。其中,PWM占空比更新仍然在三角载波的波峰和波谷进行,而电流的采样位置则位于PWM占空比更新前的几μs 处。由于FPGA并行数据处理的特点,在电流采样之后,PWM占空比更新值能够及时输出。此时,电流环的电流采样和计算延迟与电流环其他延时环节相比可以忽略不计。因此,电流环运算延迟T-delay≤0.5Ts,整体延迟小于0.75Ts。减小电流环闭环系统的延迟,能够提升电流环带宽,从而达到提升电流环的动态响应性能的效果。

图6 双采样双更新控制策略Fig.6 Strategy of double sampling and PWM duty cycle double update

3 伺服驱动控制器设计

3.1 电流环控制器设计及参数选择

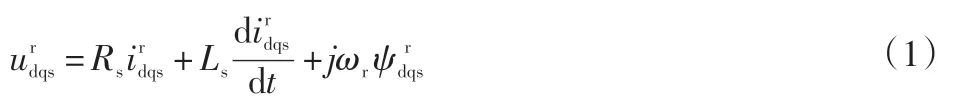

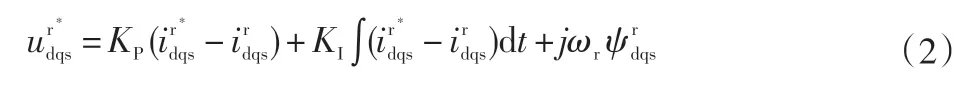

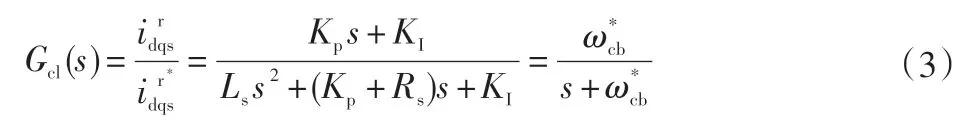

伺服电机为表贴式永磁同步电机,其电压方程如下[11-12]:

式中:Ls为电机d-q 轴电感;Rs为定子电阻;为d-q 轴电压;为转子磁链;ωr为电机电角速度。

电流环采用PI 控制,其对电机参数变化有很强鲁棒性,根据PI控制器输出,电压输入如下:

系统的传递函数由系统的零极点以及带宽决定。

3.2 速度环控制器设计及参数选择

伺服电机机械方程如下:

式中:Tem为电机的电磁转矩;J 为电机的负载惯量;ωr为电机转速;B为系统的阻尼系数;Tload为负载转矩。

速度环采用PI控制器以及系统的传递方程如下所示:

其中控制参数选择KP_sr=Jωc_sr,KI_sr=Kv_scKP_scωc_sc,ωc_sc为速度环带宽;Kv_sc为速度环带宽设置系数,选择0.2。

3.3 位置环环控制器设计及参数选择

伺服系统电流环带宽高一边等效1,速度环等效一阶低通环节,在此基础上根据系统设定带宽进行,伺服系统位置环普遍采用比例控制策略,本文也采用比例控制策略,控制参数选取如下:

4 实验平台及实验验证

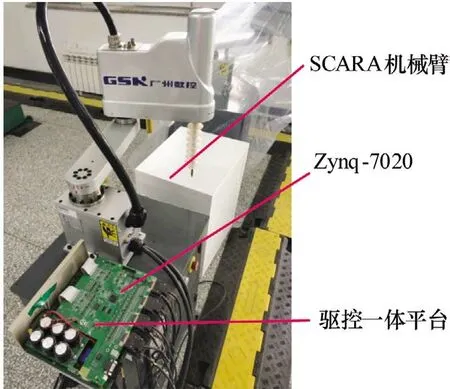

实验平台为基于Zynq打造的驱控一体平台,驱控一体集成4轴驱动与SCARA运动控制组成,实验平台,如图7所示。

图7 SCARA 驱控一体平台Fig.7 SCARA experimental setup with SoC platform

4.1 扫频带宽测试

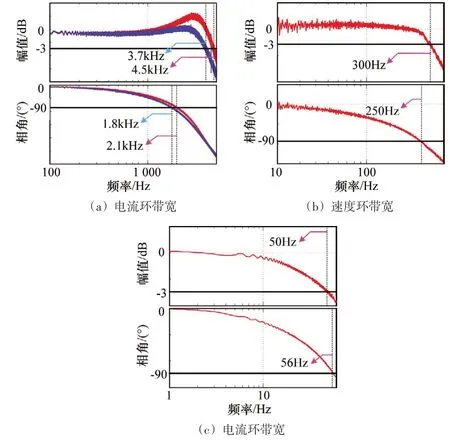

采用FPGA伺服驱动设计,控制器设计以及参数参考第3节进行设计,伺服系统带宽提升显著,下面就伺服系统位置环、速度环、电流环进行扫频测。扫频所用电机为多摩川750 W,测试条件为空载测试。

由于采用FPGA 双电流采样、双PWM 更新策略,以及零极点匹配策略,如图8所示,电流环带宽可达2.1 Hz,速度环带宽可达300 Hz,位置环带宽为50 Hz。由于采用了FPGA电流环控制策略,电流环带宽提升,进而三环带宽同步得到了提升。

图8 SCARA驱控一体平台三环带宽测试Fig.8 Three-loop bandwidth test of SCARA experimental platform

4.2 多轴数据反馈与监测

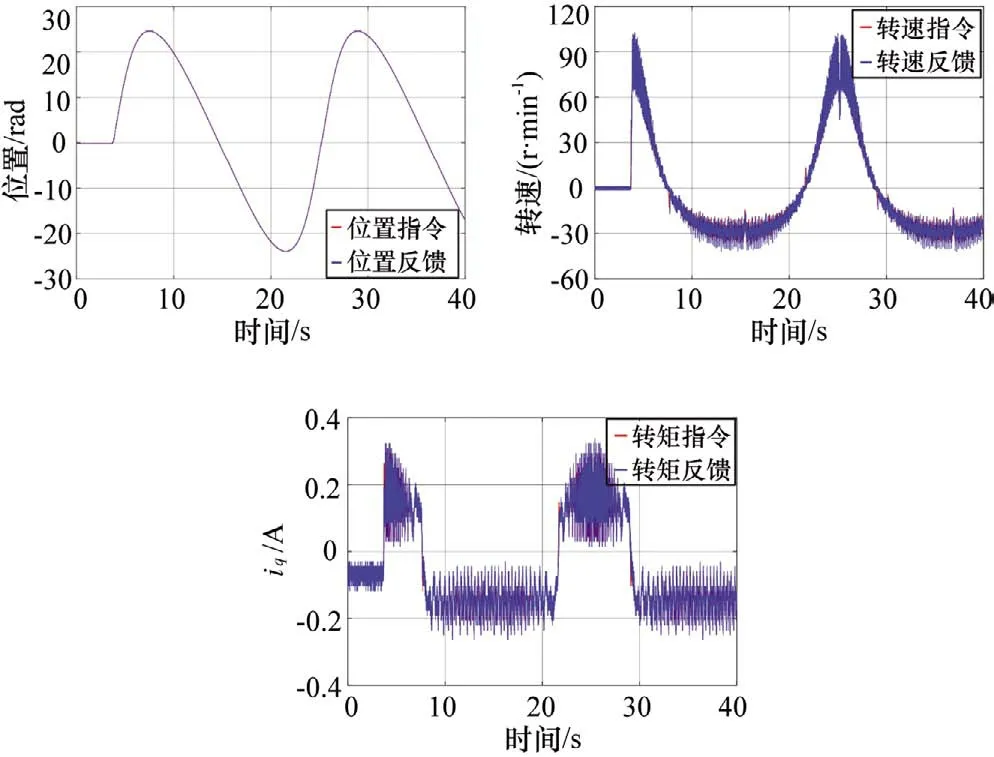

图9 所示为SCARA 机械臂在完成末端圆弧轨迹时,伺服关节信息通过ARM1核传递给运动控制ARM0核心。

图9 SCARA 圆弧轨迹2轴伺服信息Fig.9 SCARA circular path 2 axis servo information

通过驱控一体化平台可实现机械臂伺服关节状态的检测。由于采用基于Zynq-7020 作为驱控一体的控制核心。机器人的运动控制和伺服关节可以交互更多信息,不会局限于基于工业总线的通信方式,通信信息种类多以及通信速度快。后期进行更深层次算法开发可进行机械参数如关节惯量、控制参数在线调整传输等算法。

5 结束语

本文系统地介绍基于Zynq-7020 SoC驱控一体化平台,系统介绍了芯片内部资源分配,通过合理分配双核ARM资源以及FPGA资源,进行驱控一体化平台搭建,并采用乒乓缓冲的数据交互策略,区别于以太网通讯,实现运动控制与伺服驱动之间高速通信。采用双采样双更新硬件电流环控制策略,极大提高了电流环带宽,由于电流环电流环带宽提升,使得速度环、位置环带宽也获得了显著提升,在多轴硬件电流环采用流水线硬件电流环的方案,节省FPGA资源。根据期望带宽设计位置环控制器、速度环控制器、电流环控制器。最后进行了三环扫频实验,验证平台性能,以及多轴数据同时进行采集进行验证,方便机器人算法开发。