一种射频单元中FPGA的远程升级方法

2021-08-16彭磊磊辛利

彭磊磊 辛利

针对TD-LTE无线通信系统中远端射频单元的维护升级问题,提出一种FPGA固件远程升级方法。该方法采用CPRI接口的以太网信道传输固件数据、控制命令和状态信息,利用FPGA内部逻辑完成Flash的识别、擦除和写入,并在Flash分区存储的基础上,通过控制FPGA加载起始地址实现远程升级和失败回退。经验证,该方法具有易操作、可移植性强和可靠性高的特点。

当前,TD-LTE无线通信系统凭借通信效率、抗干扰性以及QoS业务保证等方面的技术优势,成为城市轨道交通系统中CBTC、PIS和CCTV综合业务承载的主要无线通信技术体制,得到了越来越广泛的应用。TD-LTE无线通信系统采用分布式架构设计,将基带处理单元集中部署在机房,而射频单元通过光纤拉远后沿轨道线路部署,形成全线的无线信号覆盖。虽然此种部署方式减少了射频信号在传输过程中的衰减,提升了信号覆盖的质量,却给壁挂于隧道内或架高于塔架上的射频单元在维护升级方面带来一定困难,间接影响了轨道交通的运营效率和安全。因此,有必要设计一种针对射频单元中FPGA固件的远程升级方法,降低维护难度,提高维护效率。

射频单元远程升级示意图

射频单元远程升级示意图如图1所示。系统维护升级时,控制中心将新版本(1.2版)的FPGA固件通过网线和光纤介质传输到射频单元。射频单元将新版本固件更新到闪存,替换旧版本(1.1版)。升级成功后断电重启,射频单元的FPGA将以新版本启动。如果升级失败,FPGA将以备份版本启动。

硬件设计

硬件设计如图2所示,主要包括三部分:微控制单元(MCU)、Xilinx 公司7系歹]FPGA以及SPI Flash。

射频单元的FPGA通过CPRI协议接收上层传来的以太网数据(包含控制命令、固件数据),并以媒体无关接口发送到MCU。MCU接收以太网数据并处理,再以本地总线(localbus)发送到FPGA。FPGA通过内部逻辑完成SPI Flash的识别、擦除和写入,并将状态信息通过以太网信道反馈给上层。

SPI Flash采用Spansion公司的s25fl256,该芯片是串行NOR Flash。FPGA 采用Xilinx 公司的XC7K325T-2FFG900I,该芯片属于Kntex7系列,具有高性价比、低功耗的特点。FPGA需要配置成主SPI加载模式,配置电路如图3所示。

Flash分区设计

本文的FPGA远程升级方法具备升级失败后自恢复的能力,设计思路是Flash存储分区。如表1所示,SPI Flash的存储区域分成三部分:FPGA加载地址控制区、备份区以及升级区。FPGA加载地址控制区存放一组用于IPROG命令的比特流,备份区存放备份固件,升级区存放升级固件。

Spansion公司的s25fl256存储空间是32MByte,其扇区类型有2种规格,一种是统一64KyteB大小,另一种是统一256KByte大小,本文选取后者。FPGA芯片XC7K325T- 2FFG900I生成的固件大小约为11.9MByte,备份固件和升级固件可同时存放在s25fl256中。

首先分配IPROG命令比特流,如表2所示。

这组比特流中,“AA995566”是同步头。FPGA只有在收到同步头后才开始接收配置数据,而同步头之前的数据后被FPGA忽略。本方案把“AA995566”放到Flash第一个扇区的最后四个字节上。同步头后的比特流按次序从Flash的第二个扇区开始位置存放并执行16个字节对齐,不足的比特流用空操作指令填充。其中热启动起始地址(WBSA)是升级固件的起始地址,本方案确定该地址为0X00B40000。

IPROG命令比特流之后开始放置备份固件。备份固件结束之后升级固件开始之前的空间放置比特1。升级区从指定地址0X00B40000开始,并按512byte对齐,不足的比特填充‘1。升级区最后的32bit是CRC32校验码,计算升级区域所有比特的CRC32值,但不包括最后的32bit。

FPGA固件修改

初始化Flash

实现在线升级功能,需要初始化Flash,即用JTAG线把修改后的固件烧录进Flash。该初始化工作只需要执行一次。修改后的固件包含IPROG命令比特流、备份固件比特流和升级固件比特流,它们的起始地址按Flash分区方案确定。

固件修改可由Matlab或C语言实现,流程如下:

1.以写模式打开一个init.bin文件,写入0x3FFFC个“FF”,并在后面的四个字节写入0x“AA995566”。

2.继续写入IPROG比特流,以16个字节对齐,不足的字节填充0x“20000000”。

3.读取备份固件并写入imt.bin,其后填充比特‘1直到0X00B40000前一个地址。

4.读取升级固件按512byte对齐,不足的比特填充‘1直到最后4个字节。计算加填充的升级固件的CRC32值并放到最后4个字节。

5.写入加CRC32校验的升级固件到init.bin。

升级固件添加CRC32

FPGA从RS232接口接收修改后的升级固件,并写入到Flash实现在线升级,该过程不再需要JTAG线。

改写升级固件只需要添加CRC32,流程如下:

1.以写模式打开一个update.bin文件。

2.读取升级固件按512byte对齐,不足的比特填充‘1直到最后4个字节。计算加填充的升級固件的CRC32值并放到最后4个字节。

3.写入加CRC32校验的升级固件到update.bin。

FPGA逻辑设计

媒体无关接口

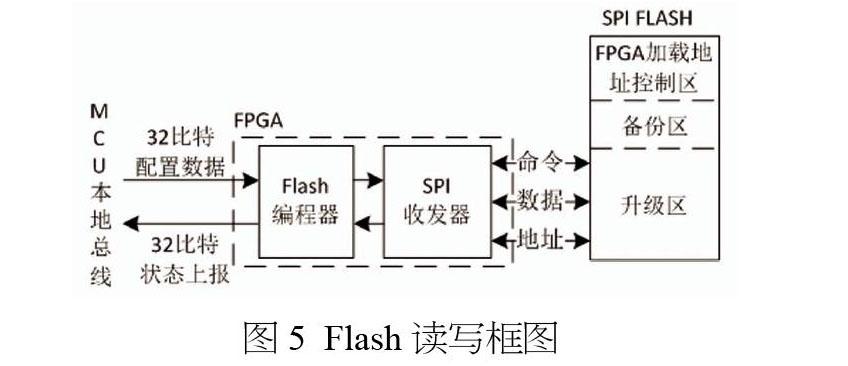

本文设计中,媒体无关接口(MII)是CPRI接口的一部分。CPRI采用Xilinx公司的IP核实现,可实现同相/正交数据、厂商特定信息、以太网数据和高速数据链路控制的传输。MII接口在CPRI接口中的位置如图4所示。

FPGA的MII接口与MCU的MII接口对接,实现以太网收发。

SPI Flash讀写

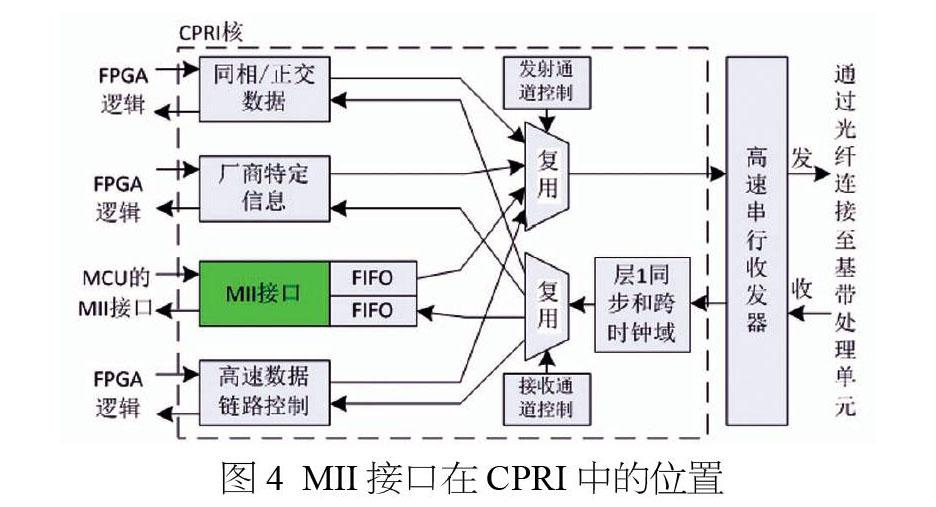

SPI Flash读写模块包含一个Flash编程器和一个基于SPI 协议的收发器,如图5所示。Flash编程器的功能是识别、擦除和烧写Flash,并通过MCU本地总线向层发送升级成功或失败的指示信号。基于SPI协议的收发器功能是向SPI Flash发送命令或数据,并从SPI Flash中接收数据。

Flash编程器实现在线升级的流程如下:

1.初始化。完成升级过程中指示信号的复位。

2.检验Flash ID并上报上位机是否正常。

3.擦除第一个扇区最后4个字节的同步头0x“AA995566”。

4.擦除升级区。

5.烧写升级区。

6.校验升级区,看CRC32余式是不是0x“C704DD7B”。

7.更新升级状态,指示升级成功或失败。如果升级成功,第一扇区最后4个字节烧写同步头0x“AA995566”。失败情况下,会给出错误类型,如超时或CRC校验有误,并不烧写同步头。

Flash编程器实现升级失败返回备份配置的关键是对同步头的控制。如果升级成功,FPGA掉电重启,检测到同步头后,执行后续的IPROG命令并跳转到升级区的起始地址开始加载;如果升级失败,FPGA无法检测到同步头,就会忽略预置的IPROG命令,从备份配置启动。

测试验证

采用多个不同的固件,在无线通信板卡上对本文方法做验证,这些固件控制板卡上的指示灯以不同的方式闪烁。选取其中2个固件并制作imt.bm初始化Flash。选取其他的固件制作update.bin做在线升级。多次执行在线升级并穿插进行人为断电操作。升级成功后,板卡上的指标灯按新固件中的逻辑闪烁。人为断电致使升级失败,板卡上的指标灯闪烁方式不变。上百次实验中,没有出现一次差错,证明本文方法具有较高的可靠性。

本文方法操作简单的特点体现在init.bin和update.bin制作上。两个文件的制作只需要简单的Matlab或C语言脚本即可实现。

本文方法的FPGA逻辑使用HDL语言编写,移植时,只需修改与Flash和固件加载地址相关的部分,具有较强的可移植性。本方法的FPGA逻辑已成功移植到以Micron公司MT25Q25做为配置存储芯片的xc7a200tfbg676-2上。

本文提出的射频单元中FPGA固件远程升级方法,操作简单、可移植性强和可靠性高,已成功应用到多个TD-LTE无线通信系统产品上,为产品的升级维护带来了便利。