环形链轮询复用测试端口的高效测试结构

2021-07-30邝继顺

张 玲,邝继顺

(1.江西财经大学软件与物联网工程学院,南昌 330013;2.湖南大学信息科学与工程学院,长沙 410082)

0 引言

测试功耗过高、测试集规模过大和由其引起的测试应用时间过长的问题是数字集成电路成本高的主要原因。如何降低集成电路测试数据规模和测试功耗成为富有挑战性的研究热点[1]。好的测试结构能以合理的硬件代价、较短的测试数据移位路径实现对集成电路(Integrated Circuit,IC)内部结点的“观察”和“控制”,将电路多个测试需求统一,获得较好的测试效果。测试结构设计是个老问题,也一直是集成电路测试的关键问题。

扫描测试是数字集成电路测试方案的基本手段,它通过将时序电路中的全部或部分时序单元设置成扫描单元来控制和观察相应电路结点的值。直链结构是最早提出的通用扫描结构,单直链结构[2]将电路中的触发器串联成单独扫描链,由于其测试数据移位路径较长,移位时间和能耗都比较大;多扫描直链结构[3]将单扫描链分成多个较短的直链,用较多的测试端口换取测试应用时间的减少和测试移位路径的缩短,但测试数据规模没有变化。为降低测试功耗和减小测试集规模,针对测试集的优化方法通过低功耗的测试产生算法[4],扫描链重排序技术[5]和无关位的填充[6]等来获得测试功耗的降低和测试集规模的减小;针对直链结构的优化主要通过扫描链的阻塞和重组[7]或阻隔扫描单元[8]来获得测试功耗的降低[9]。循环扫描结构[10]在直链结构的基础上首尾相连,其设计初衷是为电路建立自测试结构,实现零存储测试,它可以获得传统线性反馈移位寄存器自测试结构的效果,却有着普通直链相当的硬件代价[11]。循环扫描结构可实现测试数据的重用,因此它不仅可充当移动测试数据的通路实现确定性测试,而且可实现测试响应作为下个测试向量的测试模式[12],但其功耗没有降低。随机访问扫描(Random Access Scan,RAS)结构[13]可像随机存储器那样根据地址随机访问电路中的扫描单元,因此它提供了一种理想的可测试结构,理论上其测试时间和功耗问题都能得到较大改善;但电路中触发器的分布随机,硬件代价非常大,布线难以实现。针对RAS 的多数工作都是在如何减少硬件代价上[14]。

为改善测试结构本身导致的移位功耗,设计低功耗的测试结构,我们前期提出的代表扫描结构[9]将电路中的触发器分成多个环形链,为每个环形链遴选一个“代表”,这些代表组成测试数据的移位路径,实现对电路的分级管理,降低了测试移位功耗;但由于该结构的环形链和代表组成的代表链共用测试端口,它最大的缺点就是相对于直链结构,测试时间会有所损失,假设电路中有x个环形链,则每个测试向量的应用会有x个时钟周期的时间损失。为克服该缺陷,并进一步降低测试移位功耗,本文提出环形链轮询复用测试端口的测试结构RRR Scan,该结构将电路中的触发器设计成多个环形链,并串联环形链成为测试数据通路,实现测试端口的轮询复用。环形链的环形移位模式具有测试数据重用的特性,可以减小测试数据规模;而其轮询复用则缩短了测试数据的移位路径,具有低功耗的特性。该结构除具有通用扫描结构的所有性质外,本身还具有低功耗、数据重用的特性,灵活性大大增加。

1 环形链轮询复用测试端口的测试结构

1.1 环形链轮询复用测试端口的结构原理

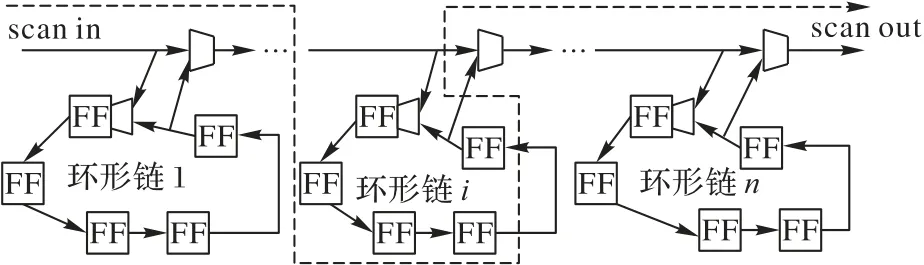

图1 给出环形链轮询复用测试端口的结构示意图,该结构包含n个环形链,测试时,环形链可工作于三种模式:直链扫描模式、隐身模式和环形移位模式。当为第i个环形链传输测试数据时,则该环形链处于直链扫描模式,其他环形链处于隐身模式(数据流向见图中虚线)。相对于传统直链来说,该结构较大地缩短了测试数据的移位路径,因此降低了测试移位功耗。对于每个环形链来说,可工作于环形移位模式,因此可实现测试响应作为下个测试向量的测试模式,实现了测试数据的重用。该结构根据电路触发器的物理分布布线,将物理上相近的触发器设置在一个环形链中,并根据测试端口个数将这些环形链串联成多个测试数据通路,不会产生较大的布线代价。但是,如何实现该结构,并以较小的硬件代价对该结构的工作过程进行准确控制是关键,也是难点。

图1 环形链轮询复用测试端口结构的示意图Fig.1 Schematic diagram of RRR Scan architecture

1.2 结构的实现

为以较小的硬件实现该结构,本文将电路中的触发器设计成同样结构的环,见图2,设该结构包含n个环形链,每个环形链包含x个触发器,还剩下m个扫描单元(m<x),环形链i包含的触发器编号依次为FFi1,FFi2,…,FFix,对应的时钟信号表示为CLOCKi,测试主路径(Main path,Mp)在图中用虚线给出。环形链中的扫描单元与传统扫描单元一样,由Scan_Enable(SE)使能,只需在环形链i的入口扫描单元FFi1上增加一个二选一选择器,用来选择来自外部的测试数据(Mp上的数据)和来自扫描链本身的测试数据,在出口扫描单元FFix上增加一个二选一选择器,用来选择来自环形链的测试数据或来自外部的测试数据(Mp的测试数据)。

表1 给出了环形链轮询复用端口的测试结构的工作模式(图中X 表示无关位,其值可以为0 或为1)。如表1 所示,SE=0 时,该电路工作于功能模式(Functional mode),如表中第一行所示。SE=1时,电路处于测试模式,以图2中的环i来说明,Ci1=0,Ci2=1,则FFi1选择来自Main path(Mp)上的数据,即Oi1=Mp=Scan_in;而对于FFix来说,Ci2=1,它被Main path 选择,即Oi3=Oi2,此时环i工作于直链扫描模式(Linear scan mode),如表中第二行所示。Ci1=1,Ci2=1,则FFi1选择来自FFix的数据,即Oi1=Oi2;而对于FFix来说,Ci2=1,它被Main path选择,即Oi3=Oi2,此时环i工作于循环移位模式(Ring shift scan mode),实现了测试响应作为下个测试向量的测试模式,如表中第三行所示。Ci2=0,对于FFix来说,Oi3=Scan_in,所以Ci1无论为什么值(用x表示),环形链均被隐藏,此时环i工作于隐身模式(Stealth scan mode),实现了测试数据移位路径的缩短,如表中第四行所示。

图2 环形链轮询复用测试端口的一个测试通路结构Fig.2 Architecture of one test access of RRR Scan

表1 工作和扫描模式的控制Tab.1 Control of work and scan modes

图3 给出包含11 个触发器的扫描通路的例子,11 个触发器被分到3 个环形链中,其中每个环形链包含3 个触发器,触发器编号如图3 所示,从右到左分别为第0 个环形链(由触发器FF01、FF02、FF03组成)、第1 个触发器(F11、FF12、FF13组成)和第2个环形链(由触发器FF21、FF22、FF23组成)。作为通用扫描结构,假设其任意两个相邻测试向量为V1和V2,对应测试响应为R1,R2,其中:V2对应的测试数据为(V21,V22,V23,V11,V12,V13,V01,V02,V03,V0),它们分别对应触发器FF21,FF22,FF23,FF11,FF12,FF13,FF01,FF02,FF03的测试数据;V1对应测试响应数据为(R21,R22,R23,R11,R12,R13,R01,R02,R03,R0),分别对应触发器为FF21,FF22,FF23,FF11,FF12,FF13,FF01,FF02,FF03的测试响应。其具体工作过程在表2中给出。

图3 环形链轮询复用测试端口结构的例子Fig.3 Example of RRR Scan

如表2 所示:第一列表示测试时间,单位为时钟周期;第二、三、四列分别表示三个环形链的扫描模式;最后一列为测试数据的应用过程。如表1 所示,在第一个时钟周期,为了将直链上的测试数据送入,并将测试响应移出,三个环的第3 个扫描单元的选择器C22、C12、C02均为0,即都选择来自数据通路Mp上的数据,处于隐身模式,它们的时钟CLOCK 均为0,处于维持状态,此时完成扫描单元F0的测试数据R0的移出和V0的移入,如表中第二行所示。

表2 环形链轮询复用测试端口结构工作过程的一个例子Tab.2 One operation example of RRR Scan

在第2~4 个时钟周期,对于环形链0 来说,它的第1 个扫描单元的选择器的控制信号C01=0,所以选择器输出O01=Scan_in;它的第3 个扫描单元选择器的控制信号C02=1,因此输出O03=O02,即该环被展开,并串到链上;对应时钟CLOCK0等于扫描时钟clk,环0工作于直链模式;C22、C12均为0,因此环1 和环2 依旧工作于隐身模式,保持数据。这3 个时钟周期为环0传输测试数据,完成测试响应R01、R02、R03移出和测试向量V01、V02、V03的移入,如表第三行所示。

在第5~7个时钟,环形链1的第一个扫描触发器的选择器控制信号C11=0,对应输出O11=Scan_in;第三个扫描单元控制信号O12=1,对应输出O13=O12;对应时钟CLOCK1等于扫描时钟clk,环1 工作在直链模式;C22,C02均为0,因此环0 和环2 工作于隐身模式,此3 个周期为环1 传送测试数据,完成测试响应R11、R12、R13移出和测试向量V11、V12、V13的移入,如表中第四行所示。

在第8~10 个时钟周期,第2 个环形链第一个扫描单元的选择器控制信号C21=0,对应输出O21=Scan_in;第三个扫描单元控制信号C22=1,对应输出O23=O22;对应时钟CLOCK2等于扫描时钟clk,环2 工作于直链模式;C12、C02均为0,环1 和环0 工作于隐身模式,此3 个周期为环2 传送测试数据,完成测试响应R21、R22、R23的移出和测试向量V21、V22、V23的移入,如表中第五行所示。

除可用于通用测试结构外,由于每个环形链可工作于环形移位模式,该结构还可用于数据压缩场合。用于数据压缩时,环形链工作于环形移位模式,测试响应在移出扫描链的同时,还传送给扫描链作为下个测试向量使用。另外,该结构将物理上相近的触发器设置在同一个环形链中,再将这些环形链根据测试端口个数分配到不同的测试通路中去,不会增加较多的布线代价,但布线问题和测试压缩的具体应用不属于本文讨论范围,本文主要讨论具有数据重用和低功耗性质的通用测试结构。

2 环形链轮询复用测试端口结构的分析

2.1 控制方式和实施方式

设该结构包含n个环形链,每个环形链具有x个扫描单元,还剩m(m<x)个扫描单元直接设置于Mp 上,则这n个环形链轮询地使用测试端口(test pin),而其他环形链工作于保持模式,其时序控制在图4中给出。图4给出了一个测试向量的移入和其上个测试响应的移出过程,其中clk 为扫描时钟,CLOCKn,CLOCKn-1,…,CLOCK1分别为第n个环形链、第n-1个环形链,…,第1个环形链的时钟。

如图4 所示,其具体时序描述如下:经过m个时钟,将直链上的测试数据移入和移出;在下x个周期内,为环形链n移入测试数据,并移出测试响应,此时,环形链n的时钟CLOCKn=clk,其工作于直链模式,而其他环形链的时钟控制信号为0,工作于隐身模式;在下x个周期内,再以同样的方式为环形链(n-1)分配测试数据和移出测试响应,直到完成n个环形链的测试数据的分配和移出,即完成了一个测试向量的应用和测试响应的移出。从该时序图中可以看出,该结构中的每个环形链的时钟控制信号CLOCKi是一组完全相同的信号,它们很容易从扫描时钟信号clk 中获得,而无须增加额外的测试端口。

图4 环形链轮询复用测试端口测试结构控制时序图Fig.4 Control sequence diagram of RRR Scan

2.2 测试功耗和代价分析

与代表扫描结构[9]不同,该结构直接将不参与移位的环形链屏蔽掉,因此移位功耗的降低与屏蔽掉的路径的长度有关,屏蔽掉的扫描单元越多,则测试数据移位时产生的功耗越低。与文献[9]一样,先假设任意两个扫描单元之间的测试向量和测试响应均存在跳变,则可反映任意位置可能发生的跳变,并用Matlab对此关系进行了分析,其中所有电路均被设置成一个测试通路(多个测试通路的分析方法相同)。

图5 给出针对电路S5378 和S9234 的分析结果,其中横轴x表示环形链的大小,纵轴表示总的移位功耗(用总的跳变数WTC 计算[9]),图中给出了扫描直链(Pcon)、代表扫描链结构(Prp)和本文提出环形链轮询复用测试端口的测试结构(Prtm)的功耗结果。

图5 移位功耗曲线图Fig.5 Curve of shifting power consumption

从图5可以看出,传统直链的功耗与x无关,为固定值;对于代表扫描链,其功耗随环形链x的增大呈先降低后升高的趋势,因此存在功耗最低点;对于本文提出的环形链轮询复用测试端口的测试结构,其功耗随着x的增大而升高,一个极端情况,扫描通路中的所有扫描单元组成一个环形链,这时该结构就成了著名的循环扫描结构[10];而另一个极端,x=1,即每个扫描单元本身就是一个环形链,每个扫描单元都能被随机访问,该结构就成了随机扫描结构(RAS)[13]。而在所有情况下,相对于传统扫描直链结构和代表扫描结构,环形链轮询复用测试结构都能获得较低的测试功耗。除此之外,所有环形链均可工作在环形移位工作模式,可以实现测试响应作为下个测试向量的测试模式,实现了测试数据的重用。

实际上,我们对所有的ISCAS89 大时序电路以及ITC99电路进行了分析,所有移位功耗都是随着环形链x的增大而增大,且它们的移位功耗曲线变化的规律完全相同,这是因为本结构中环形链大小的变化均是由1 到其最大值。当环形链为1 时,可随机访问每个扫描单元,功耗最小,但其布线较复杂,所需的选择器较多;而当环形链达到其最大值时,即测试通路成为一个大的环形链,其移位路径最长,相应的移位功耗也最大。而其他的移位功耗均位于两个极端条件之间,在假设条件一致的情况下,它们的变化规律也会完全一致。从硬件结构上来看,相对于传统的直链结构,环形链轮询复用测试端口的测试结构在硬件代价有所增加,其硬件代价在于每增加一个环形链,会增加两个二选一选择器;相对于代表扫描结构[9]每个扫描单元都增加一个选择器来说,其硬件代价大大减小。布线代价上来看,该结构可将物理上相近的扫描单元设置于一个环形链,可结合电路本身扫描单元的布局获得优化的布线结构。从时延上来看,由于屏蔽了部分环形链,因此测试数据的移位路径长度有所缩短,即其扫描链长度有所减小,时延有所减小。测试时间上来看,环形链轮询复用测试端口的测试应用时间与传统扫描直链一样,而对于代表扫描结构,假设测试数据通路包含n个环形链,则每个测试向量多出n个时钟周期的损耗。

由此可见,相对于传统直链扫描结构和循环扫描结构,该结构提供了更大的灵活性。该结构可以通过环形链的大小来平衡硬件代价和移位功耗之间的约束,在对面积要求比较高的电路中,可以将环形链大小x设置得较大,从而在获得较低测试功耗的同时,减小硬件代价;而在对功耗要求比较高的电路中,可以将环形链大小x设置得较小,从而在合理的硬件代价下获得较高的测试功耗的节约。而相对于代表扫描结构,相同条件下,该结构均可通过较低的硬件代价减少更多的测试功耗。

3 实验和分析

本文对传统扫描直链、代表扫描结构[9]及本文提出的代表扫描链在Intel Pentium 2.13 Hz CPU,2.93 GB 内存的Linux C 环境下进行了对比。对比实验主要是对ISCAS89 时序电路的mintest 测试集[15]进行了测试,假设单个测试端口(多个测试端口分析相同)从移位寄存器大小为1 到大小为N(N为扫描直链的所有扫描单元的个数)之间进行计算,功耗比较结果如表3 所示。其中:第一列和第二列分别为电路名称和其包含的触发器个数(FF),假设电路仅一个测试端口,因此被设置为全扫描的单个测试通路;第三列给出了扫描直链结构的总移位功耗P_sa;第四、五、六列分别给出代表扫描结构[9]的功耗最低点对应的x的值、最优功耗R_sa 和其相对于传统直链所降低的移位功耗的比率sag1,其中sag1=(P_sa-R_sa)/P_sa;第七、八列给出了环形链复用测试端口测试结构的功耗结果,其中第七列给出该结构对应于代表扫描结构的功耗最低点x的功耗,第八列为其相对传统直链所减少的移位功耗比率sag2,其中sag2=(P_sa-M_sa)/P_sa;最后一列为本文提出的环形链轮询复用测试端口的测试结构的功耗M_sa相对代表扫描结构的功耗R_sa降低的移位功耗比率,其中sag=(M_sa-R_sa)/M_sa。

从表3 中可以看出,相对于传统扫描直链,代表扫描结构和环形链轮询复用测试端口的测试结构均较大程度地降低了功耗,对于S13207 来说,其环形链轮询复用测试端口的测试功耗降低比率为99.58%;另一方面可以看出,代表扫描结构的功耗最低点,环形链轮询复用测试端口的测试结构都获得了较低的移位功耗,对于S38584 电路来说,其功耗最低点的减少比率为47.30%。

表3 测试移位功耗比较Tab.3 Comparison of test shifting power consumption

4 结语

测试集规模过大和测试功耗过高是数字集成电路测试的巨大挑战,优化的通用测试结构不仅可以获得较好的测试效果,而且可以减小功耗和测试集规模。本文提出环形链轮询复用测试端口的测试结构,该结构将扫描单元设置到多个环形移位寄存器中,环形移位寄存器可工作于直链模式、环形移位模式和隐身模式,缩短测试数据的移位路径,可实现测试响应作为下个测试向量的测试模式,降低了测试移位功耗,同时可用于测试压缩,因此是一种本身具有低功耗和测试集重用的通用测试结构。理论和实验均表明,该结构克服了代表扫描测试时间增大的缺陷,是一种低端口、低功耗、可测试数据重用的通用测试结构,不会增加额外的测试端口,布线代价合理。本文下一步工作是将该结构用于测试压缩中,获得较小的测试集规模。