某型相控阵雷达脉冲压缩截位方式研究

2021-07-29中国电子科技集团公司第二十研究所赫炜亮

中国电子科技集团公司第二十研究所 赫炜亮

在雷达信号处理中,为了同时获得大的脉冲宽度和带宽,提高距离分辨能力和速度分辨能力,在雷达发射端使用线性调频信号,在接收端用匹配滤波器对回波进行脉冲压缩处理。本文提出了用FPGA进行脉冲压缩截位的改进方法,该方法能尽可能减少信号处理精度损失,并在实际工程中得到了应用。

1 FPGA实现脉冲压缩算法的过程

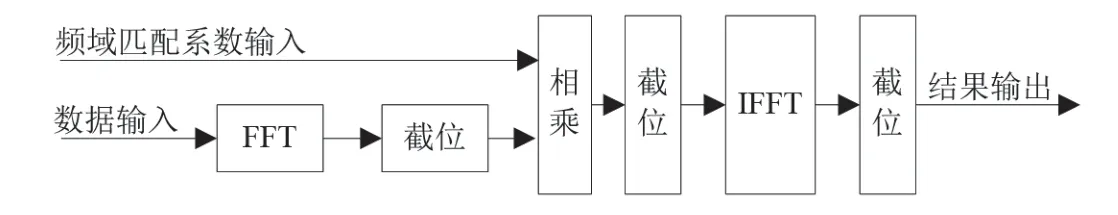

FPGA按照频域滤波的方式实现脉冲压缩,首先将理论计算的匹配滤波系数FFT值保存在ROM中,然后对输入线性调频信号做傅里叶变换,并将变换后的结果与系数相乘,最后做逆傅里叶变换,得到脉冲压缩的结果。因IP核输出位宽大于输入的位宽,而FPGA数据流位宽固定为32位(虚部和实部各16位,最高位为符号位),因此,在每一步骤结束都需要进行截位操作,然后将截位后的32位结果输入下一级IP核,如图1所示。

图1 FPGA实现脉冲压缩的过程

截位操作会带来无法避免的精度损失,而FPGA实现脉冲压缩时进行了三次截位,导致输出结果出现了无法忽略的误差,在某型雷达的信号处理中表现为信噪比不稳定,易出现漏检、错检的情况。

2 普通脉冲压缩截位方式的改进

FPGA数据流的位宽是固定的,因此脉冲压缩时必须进行截位。为了减少精度损失,应尽可能减少截位的次数,由此提出一种新的截位方式,即将输入信号的FFT值直接与匹配系数相乘,然后进行IFFT操作,对最终输出结果进行一次截位,实现脉冲压缩。如图2所示。

图2 改进后的FPGA实现脉冲压缩的过程

改进后的计算方式只进行了一次截位操作,可以将精度损失降到最低。但这种方式会增加FPGA程序的资源占用量。在雷达实际应用中,以获得尽可能准确的探测结果为第一要求,因信号处理损失过多有效信息是不能接受的,因此,在FPGA内部资源足够丰富的情况下,应该使用改进截位后的脉冲压缩算法。

3 改进截位后的结果验证

图4 FFT后结果对比

用matlab生成脉冲宽度T为6us、采样率fs为30MHz、带宽B为20MHz的线性调频信号,如图3所示,该信号为某型雷达实际使用波形,具有分析价值。用该信号作为matlab程序的输入,同时将该信号的实部和虚部分别按215-1进行归一化,作为FPGA程序的输入,将匹配系数按215-1归一化后保存至FPGA的ROM中,进行仿真,并保存每一步计算的结果,进行对比。

图3 仿真用理论线性调频信号

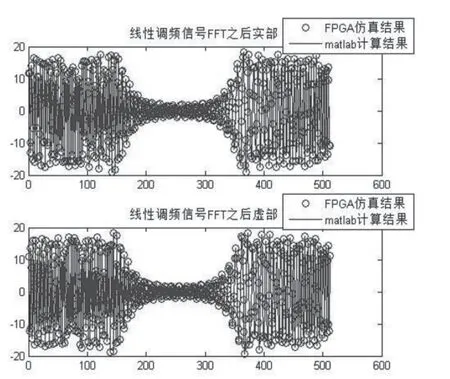

FPGA的FFT核配置配置后显示输入虚部[31:16]和实部[15:0]的格式是fix16_15,输出虚部[58:32]和实部[26:0]的格式是fix27_15,可以发现输出有效数据长度为实部和虚部各27位,且输入输出的小数位均为15,因此不会因格式产生幅度差。FPGA输入时进行了归一化,相当于扩大了215-1倍,将FPGA输出FFT结果除以该值,然后与matlab计算的FFT结果进行对比,如图4所示。

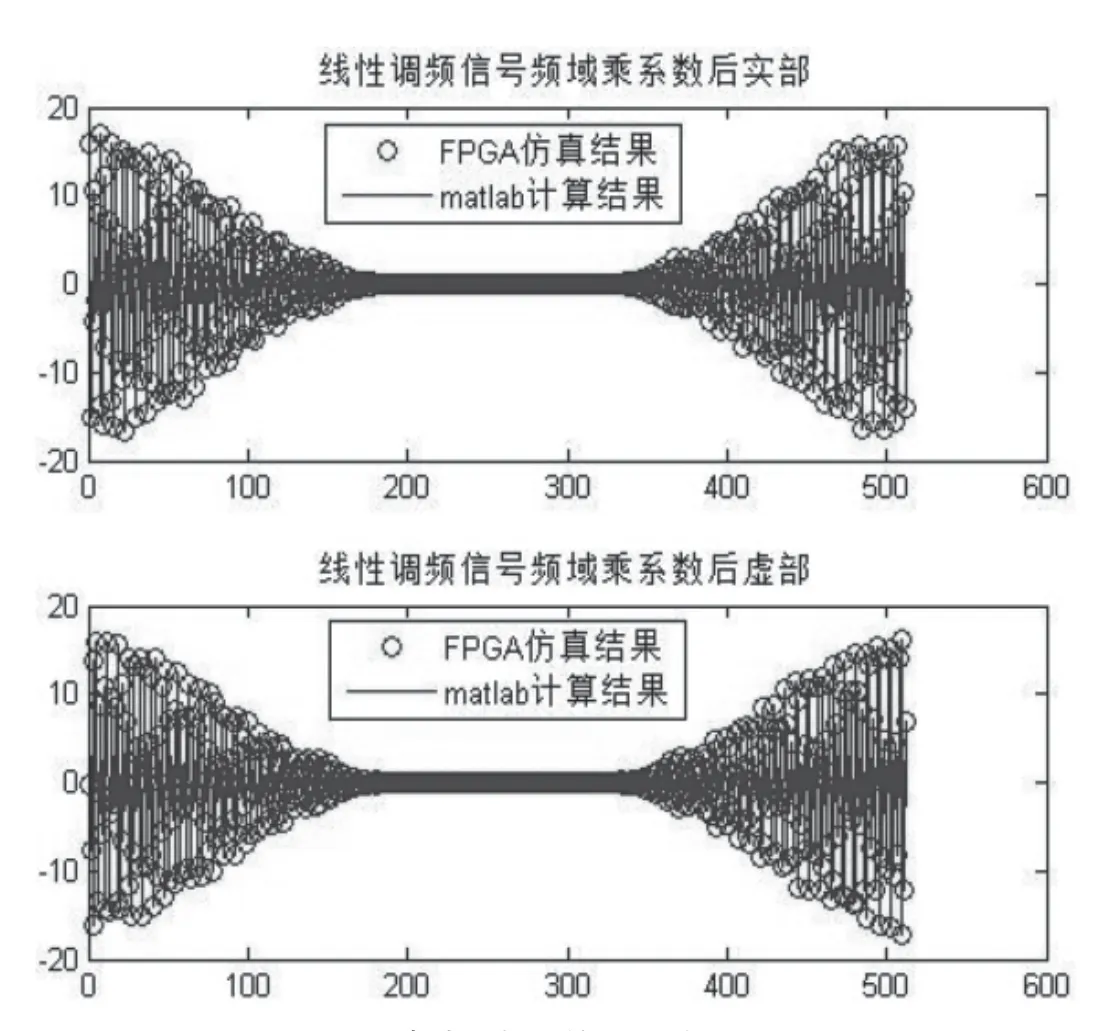

在FPGA中,将FFT的输出直接送至复数乘法器,与匹配系数相乘。配置后的乘法器IP核显示输入1的虚部[58:32]和实部[26:0]的格式为fix27_0,输入2的虚部[31:16]和实部[15:0]的格式为fix16_0,输出虚部[72:40]和实部[32:0]的格式是fix33_0。可以发现输入和输出数据的小数位都是0,不会因格式产生幅度差。同时,因FFT输出与真值相比,扩大了215-1倍。匹配系数也是扩大了215-1后作为输入,因此,将FPGA乘系数的结果除以(215-1)2,然后与matlab计算结果进行对比,如图5所示。

图5 乘滤波系数后的结果对比

在FPGA中,将乘法器输出值送至FFT核进行IFFT操作,配置后的IP核显示输入虚部[72:40]和实部[32:0]的格式是fix33_32,输出虚部[91:48]和实部[43:0]的格式是fix44_32,可以发现,输入和输出数据的小数位都是32,所以不会产生因格式产生的幅度差。因乘法器输出与真值相比,扩大了(215-1)2倍,将FPGA输出FFT结果除以该值,然后与matlab计算的FFT结果进行对比,如图6所示。

图6 IFFT后的结果对比

可以发现,用matlab处理的结果和FPGA处理结果相比,二者基本吻合,表明通过最后截位的方式,计算得到的脉冲压缩结果可靠。

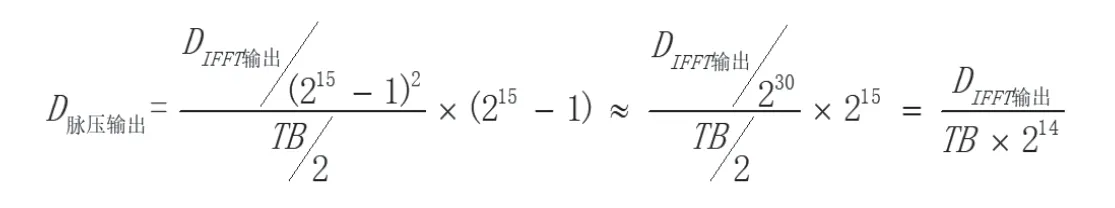

FPGA的处理位宽为32位,因此,需要将真值进行归一化。脉冲压缩比为时宽带宽积,因匹配系数乘了海明窗,实际压缩比约为时宽带宽积的一半,将真值除以该值,然后乘以215-1,进行归一化。因此,FPGA的IFFT输出结果与最终结果关系为:

结论:改进后的脉冲压缩方式实现了尽可能减少因截位产生精度损失的目标,并将此方式实际应用在了某型跟踪雷达的信号处理中,取得了预期的成果。