一种柔性透明屏LED驱动芯片设计与实现

2021-07-29范学仕王祖锦唐茂洁

范学仕,王祖锦,唐茂洁,彭 杰

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

发光二极管(Light Emitting Diode,LED)作为新型半导体照明材料,具有尺寸小、寿命长、成本低、节能环保以及高效安全等优点,发展迅速且市场火热,在显示屏、照明设备及其他电子设备中得到广泛应用[1-2]。2019年全球LED市场突破500亿,近5年复合增长率达到15%以上[3-4]。与此同时,市场对LED显示提出了画面清晰细腻、色彩自然真实、流畅无闪烁等更高的要求[5-6]。

在实际应用中,对于可绕性好、美观轻薄、能贴附在任意曲面或不规则物体表面的柔性器件的需求日益增大[7]。有机发光二极管(Organic Light Emitting Diode,OLED)虽然可以制成具有可弯曲特性的器件,但与LED相比仍有一些不足,特别是在潮湿环境中,与LED相比,OLED的寿命短、稳定性差[8]。随着科学技术的进步,实现高分辨率、明亮持久、轻薄并能应用在柔性透明屏中的LED驱动芯片已成为研究热点[9]。2005年第一支III-V族柔性材料制作出来后,研究人员用微结构GaAs制作出第一支柔性III-V族LED[10]。2009年《科学》杂志发表了一项由特殊的纳米印章技术制作的柔性无机LED[11]。2010年,研究人员开发出具有良好防水性能和生物相容性的超薄LED[12]。

针对市面柔性透明屏驱动存在的功能单一、级联个数低、电流无法调节、灰度等级低等问题,本文采用SPWM算法技术,设计了一款专用于柔性透明屏的LED显示驱动芯片。

2 驱动芯片设计与实现

2.1 总体架构设计[13]

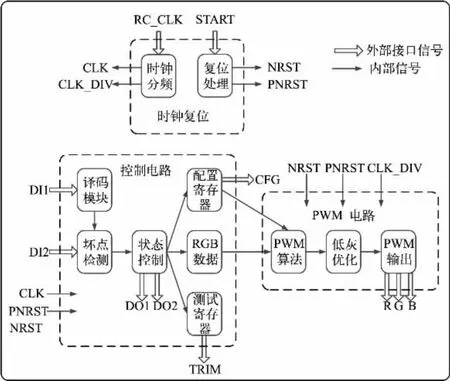

为解决市面现有产品功能单一和性能不足等问题,在设计中创新地提出图1所示的芯片整体架构。整个芯片包括时钟复位电路、控制电路和PWM电路3个部分。时钟复位电路根据内部振荡器产生的时钟RC_CLK和上电信号START进行时钟分频和复位信号处理,输出分频时钟信号CLK_DIV、整形时钟信号CLK、上电复位信号PNRST和换帧复位信号NRST。控制电路根据输入的归零码(RZ码)DI1和DI2,完成译码、坏点检测、状态控制,将相应的数据传送至配置寄存器CFG、PWM显示的RGB数据寄存器和测试寄存器TRIM中,级联数据通过DO1和DO2传递到后续级联芯片中。PWM电路根据控制电路的RGB数据,通过PWM算法和低灰优化算法,将相应的RGB数据转化为PWM输出到相应的驱动模块。

图1 驱动芯片整体架构

2.2 时钟复位电路设计

时钟复位电路包括时钟分频电路和复位处理电路两个部分。时钟分频电路结构如图2所示。内置32 MHz振荡器可以保证芯片的16 bit高灰阶数据,弥补现有产品灰度等级低等问题。内部振荡器产生的32 MHz的时钟CLK32M通过一级寄存器DFF生成2分频16 MHz的时钟CLK16M,CLK16M再经过一级寄存器生成4分频8 MHz的时钟CLK8M,依此类推,共计经过5级寄存器,生成32分频的1 MHz时钟CLK1M。分频产生的时钟根据可配置分频信号DIV_NUM,通过一个多路选择器MUX,选择产生相应的分频时钟CLK_DIV,CLK为振荡器产生的32 MHz时钟的整形输出,屏蔽复位期间的时钟,避免产生时钟毛刺。

图2 时钟分频电路结构

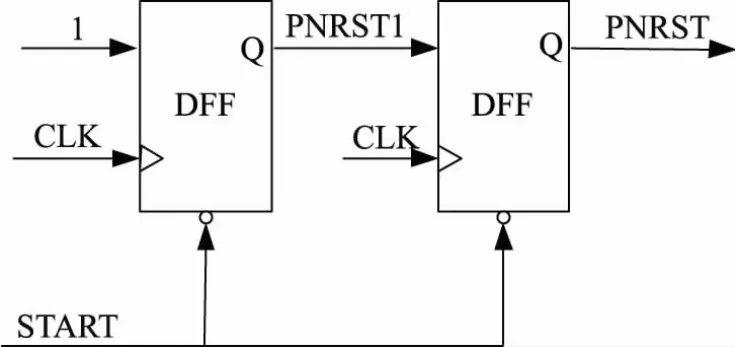

复位处理电路结构如图3所示,采用两级寄存器结构,完成异步复位,同步释放操作,避免系统出现亚稳态。在整形输出时钟CLK的上升沿,将第一级寄存器输入固定高电平(逻辑1),第二级寄存器将第一级寄存器输出PNRST1打一拍,得到异步复位同步处理之后的复位信号PNRST,而输入的上电信号START作为两级寄存器的复位信号。换帧复位信号NRST采用相同结构进行处理,在每次数据换帧时产生,通过计数低电平时间,当低电平计数器记满之后,产生换帧复位信号,用于同步所有级联芯片。

图3 异步复位同步释放电路结构

2.3 译码电路设计

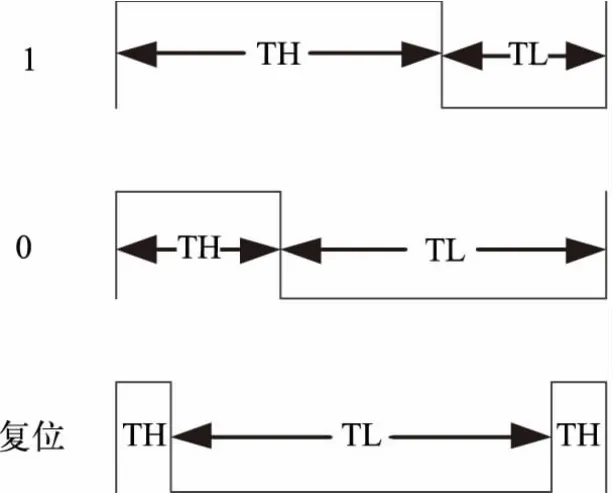

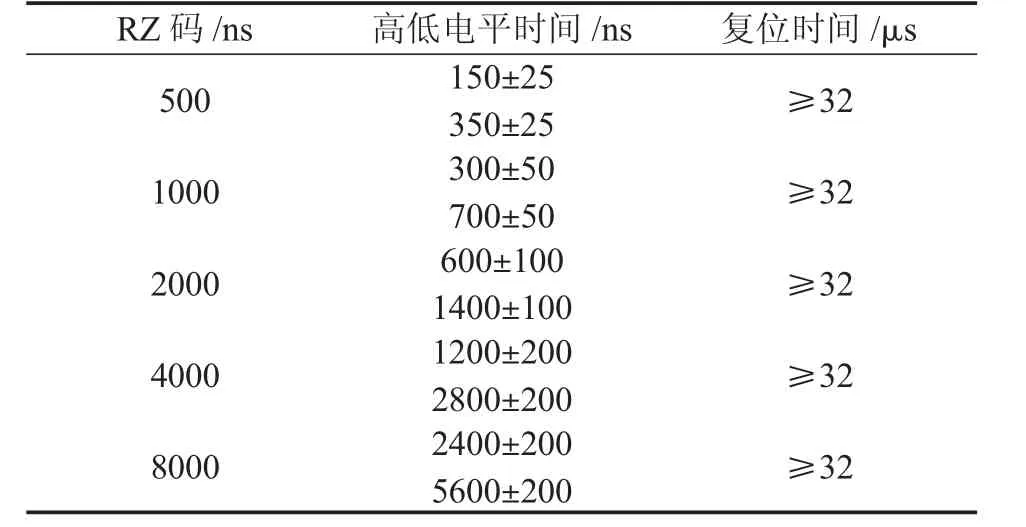

芯片采用灯芯合封的方式,要求体积小、引脚数目少。芯片采用只需单线传输的RZ方式进行传输,可以最大限度地节省面积和引脚数,配合高精度内置32 MHz时钟,可以准确地进行数据传输译码,传输速率为500 ns~8μs,其数据格式如图4所示。将通过DI1和DI2输入的RZ码数据进行同步处理,通过同步后信号的上升沿和下降沿作为计数判断依据。内部定义高电平计数器CNTH[6:0],低电平计数器CNTL[6:0],当高电平时间大于低电平时间,即CNTH>CNTL时,将RZ码译码成逻辑1;当高电平小于等于低电平时间,即CNTH≤CNTL时,将RZ码译码成逻辑0。表1为RZ码数值对应表。

图4 RZ码数据格式

表1 RZ码数值对应表

2.4 坏点检测电路设计

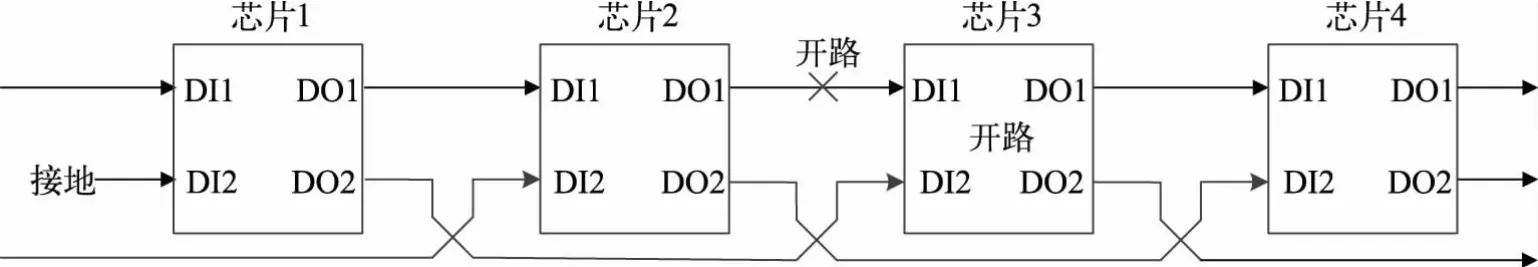

在柔性透明屏的芯片应用中,通过级联方式进行连接,一旦其中某一颗芯片出现异常,会导致整个系统瘫痪,故采用图5所示的特殊级联拓扑结构,配合内置的坏点检测电路,可以有效地保证整个系统稳定可靠的工作。坏点检测电路通过计数DI1和DI2不相等的个数来判断是否出现坏点,当主数据输入口DI1出现问题时(始终为1或者0),被判断为坏点,舍弃当前一帧的数据,切换到备用数据口DI2输入。

图5中级联芯片1~4共计4颗芯片,当芯片3被判定为开路状态时,此时芯片3的DI1不再作为数据输入,切换到备用输入DI2,舍弃出错的一帧数据,使整体系统继续正常工作。此特殊的级联结构和坏点检测电路的设计可以精准判断任何一种开路状态并完成检测,避免系统瘫痪,极大地增加了系统的稳定性。

图5 芯片工作级联拓扑结构

2.5 状态控制电路设计

芯片单线传输结构对于多种数据类型及状态控制提出了更高的要求,为解决这一问题,本文设计了状态控制电路完成串并转换、帧识别、状态跳转和整形输出处理。串并转换电路通过56位移位寄存器将译码完的串行数据转换为相应的并行数据,并根据数据的帧头,识别为配置寄存器、数据寄存器或者测试寄存器数据。配置寄存器主要用于配置电路的电流调节参数、时钟分频参数、打散方式和优化方式等系统配置信息;数据寄存器主要为电路刷新显示的RGB灰度数据;测试寄存器主要用于时钟校准和电流校准等相关测试。由于该芯片应用的级联拓扑结构,级联数据的输出需要屏蔽掉当前芯片接收的一帧数据,经过屏蔽整形后将后续级联数据输出。

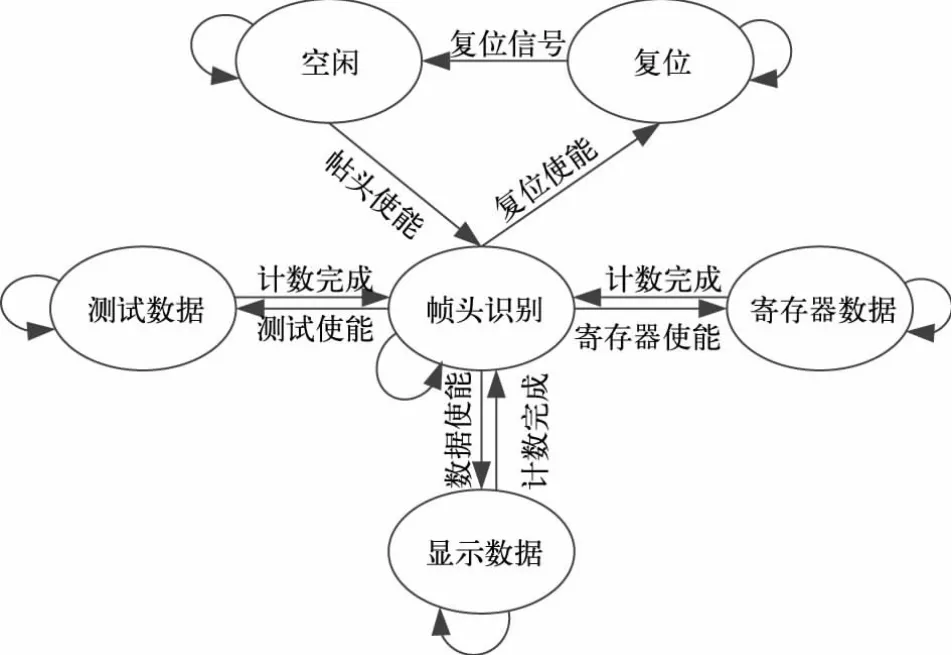

图6为系统状态跳转图,上电复位后系统处于复位状态,帧头使能信号为高时,系统进入帧头识别状态,此时同步通过移位寄存器进行串并转换操作,通过识别不同的帧头,系统跳转至相应的测试数据/寄存器数据/显示数据状态,跳转至相应的寄存器状态后,当计数记满所需要的数据量之后,再次跳转至帧头识别状态,继续下一组数据的接收;同时屏蔽当前级联芯片已接收的数据,使其不在输出通道DO1和DO2上传递,使后续级联电路接收正确数据,实现数据的整形输出。在帧头识别状态,如识别为复位帧,则系统跳转至复位状态,在复位状态完成复位和级联芯片的同步操作。

图6 系统状态跳转图

2.6 PWM控制电路

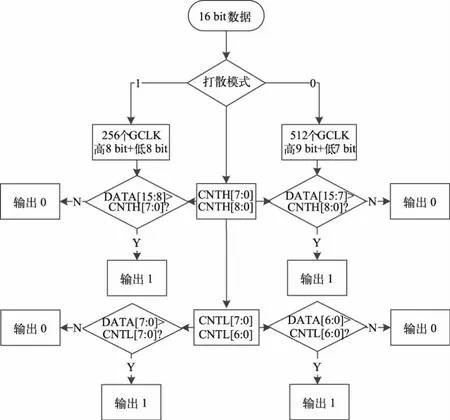

越高的灰阶位数对应的显示画面越细腻,芯片设计的SPWM算法电路可以实现16 bit(即65536种变化)。芯片采用如图7所示的SPWM打散算法对数据进行处理。将灰度数据划分为高位数据和低位数据,将高位数据和低位数据与内部定义的打散计数器进行比较,再通过反向计数的均匀分布方式,实现PWM打散。输入的16 bit灰度数据,根据可配置的打散方式SCRAMBLE_MODE选择打散成128/256组,每组分别对应512/256个GCLK。以打散256组、每组256个GCLK为例,将16 bit的数据分为高8 bit和低8 bit,将高8 bit数据DATA[15:8]与内部显示高位时钟计数器CNTH[7:0]进行比较,当DATA[15:8]>CNTH[7:0]时,PWM输出高,反之PWM输出低。将低8 bit数据DATA[7:0]与内部显示低位时钟计数器CNTL[7:0]进行比较,当DATA[7:0]>CNTL[7:0]时,PWM输出高,反之PWM输出低。

图7 PWM打散算法流程

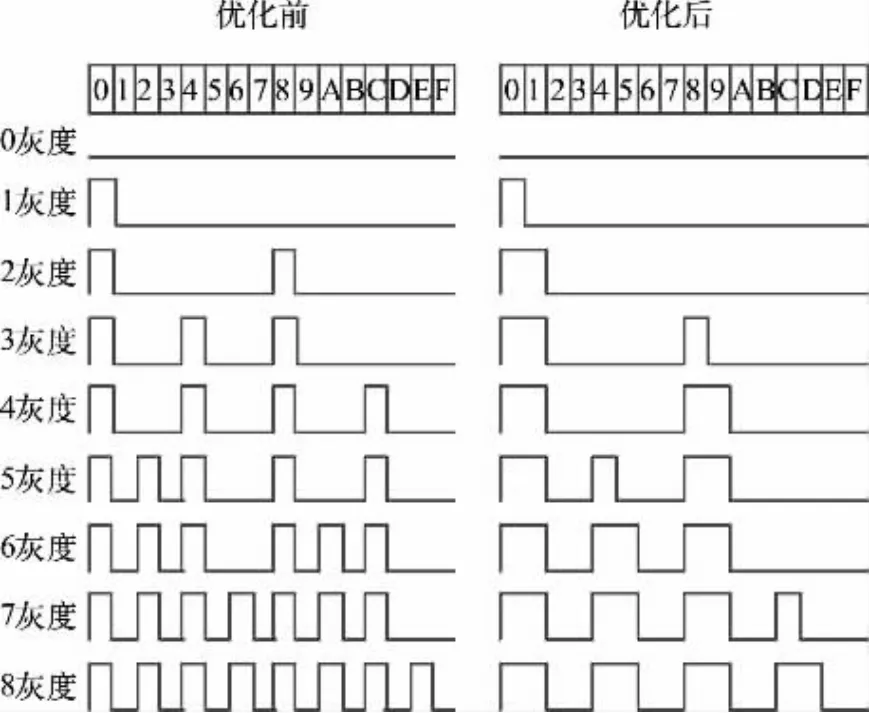

低灰优化电路在低灰度时,可通过将PWM打散之后的几个不同周期的数据合并到一个周期显示,以提升低灰显示效果。低灰优化时序如图8所示,设定低灰优化时钟个数为2,当每个子周期的打开通道个数小于2时进行合并显示,每个子周期显示2个时钟周期的PWM;当超过2个时钟时,在下一个子周期继续显示。以灰度7为例,在优化之前,依次在第0、2、4、6、8、A、C、E组打开一个时钟周期的PWM;在优化之后,依次在第0~1、4~5、8~9组打开2个时钟周期的PWM,在第C组打开1个时钟周期的PWM。经过低灰优化之后,可以提升低灰显示效果。最后将打散优化后的RGB的PWM信号输送到驱动电路,实现LED的亮暗。

图8 低灰优化时序

2.7 低功耗设计

为降低功耗,芯片增加低功耗设计,通过控制位选中是否为使能低功耗模式,当为使能低功耗模式时,检测到R/G/B/灰度数据全部为0时,芯片进入低功耗模式,此时仅有振荡器、电流偏置、译码电路和控制电路工作,其余电路全部处于standby模式,整体电流不超过0.5 mA。在实际应用中,极大地降低了整个系统的功耗,延长使用寿命。

3 结果及分析

3.1 验证平台

为模拟实际芯片的使用环境,采用图5的拓扑结构,设计3颗芯片级联的仿真验证平台(见图9)。第一颗级联芯片内部运行时钟为32 MHz,第二颗级联芯片内部运行时钟为38.4 MHz,第三颗级联芯片内部运行时钟为25.6 MHz。基于Linux系统,搭建LED驱动芯片仿真平台,采用标准验证方法,覆盖所有模块及系统的前仿、后仿和数模混仿,所有覆盖率均达到99.99%。

图9 级联仿真验证平台

3.2 仿真结果分析

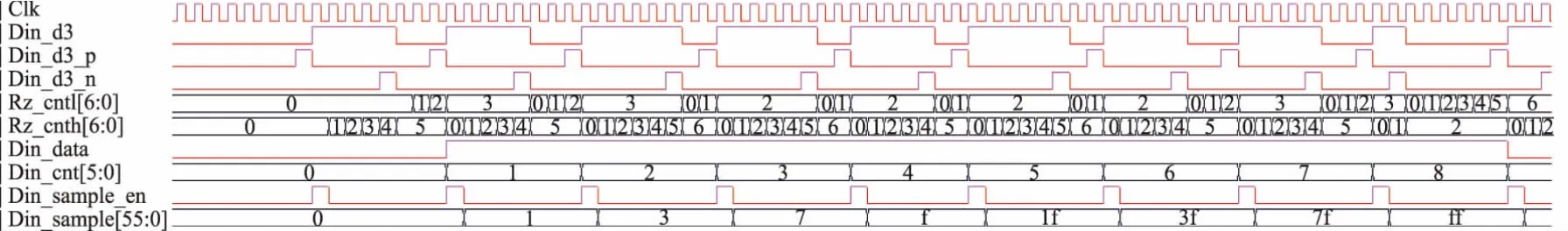

图10为指令译码仿真时序图,Clk为译码时钟;Din_d3为经同步处理和坏点检测之后的RZ码输入信号;Din_d3_p为Din_d3的上升沿触发信号,用于控制高电平计数器Rz_cnth;Din_d3_n为Din的下降沿触发信号,用于控制低电平计数器Rz_cntl;Din_data为RZ码译码之后的0/1信号;Data_cnt为译码信号的计数器;Data_sample_en为移位寄存器Data_sample的使能信号。图10中,将高低电平各不相同的8位串行数据译码成8’hFF。

图10 指令译码前仿时序

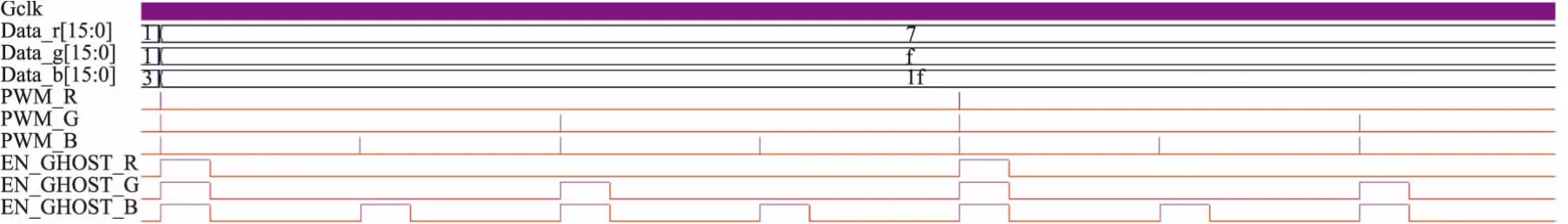

图11为PWM刷新显示后仿时序,GCLK为分频之后的时钟信号;DATA_r/g/b分别为写入的灰度数据;PWM_R/G/B为PWM输出显示信号;EN_GHOST_R/G/B为消隐使能信号。依次写入的R/G/B数据为16’h7、16’hF、16’h1F,由优化打散算法可知,PWM_R在开始和1/2周期处打开;PWM_G在最开始、1/4、1/2、3/4周期处打开;PWM_B在最开始、1/8、1/4、3/8、1/2、5/8、3/4、7/8周期处打开。消隐使能信号在PWM信号拉低之后拉高,在下一个PWM周期打开之前拉低。

图11 PWM刷新显示后仿时序

3.3 实测结果分析

本文设计芯片主要的实测技术参数与市面现有产品参数对比如表2所示。芯片在功能和性能方面都优于市面现有主流产品WS2812。

表2 技术参数对比表

4 总结

针对日益火爆的显示驱动市场,设计了一款专用于柔性透明屏的LED显示驱动芯片,该芯片由时钟复位电路、控制电路和PWM电路3个部分组成。针对市面上柔性透明屏驱动存在的功能单一、级联个数低、电流无法调节、灰度等级低等问题,该芯片新增断点续传和全彩显示功能;采用RZ译码方式,具有端口少、体积小、最大级联1024颗芯片等优点;设计了支持全局电流和R/G/B单色电流调节模式,调节范围广;采用SPWM算法技术,最高灰度等级达到16 bit;与此同时,进行了低功耗设计,功耗降低75%,静态电流最低0.5 mA。仿真和实验测试结果均证明了设计的正确性、合理性及优越性。