基于TMS320C6678的雷达导引头OCOG测高算法的并行实现

2021-07-21刘静寒

刘静寒 胡 虹

(中国电子科技集团公司第三十八研究所 合肥 230088)

0 引言

合成孔径雷达[1](synthetic aperture radar,SAR)成像技术,具有全天候、全天时的工作能力,作用距离远,抗干扰能力强,使其在军事目标探测和识别方面发挥着巨大的作用。SAR和惯导的组合即可用于导弹的末段制导,也可为导弹的中段导引控制提供信息。SAR成像过程中,雷达平台与成像区域的相对高度是影响斜地几何校正精度的重要参数,高度误差会引起明显的几何形变并影响景象匹配过程[2]。弹载雷达测得高度值来确定导弹的空间高度,结合景象匹配提供的导弹平面二维坐标,来进行弹目位置定位完成对惯导数据的修正。因此导引头系统相对地面目标的精确高度获取对导弹中末段制导精度有着重要意义。弹载雷达受到空间和重量等因素的限制,对雷达设备量的限制极为苛刻,高集成度的雷达信号处理系统显得极为重要。实际工作中,对于大带宽、高精度及高实时性的信号处理系统的需求,基于单核DSP器件已不能满足其系统性能要求,多核DSP已经成为数字信号处理发展的必然选择。基于美国德州仪器(Texas Instrument)推出的TMS320C6678八核DSP平台,在其KeyStone[3-5]架构下,分析和研究了弹下点OCOG测高算法及其实现方法,然后对测高回波数据在多核DSP上进行算法实现以验证算法并行实现的可行性,最后对该方法的准确性和实时性进行了验证,结果表明能够满足系统指标的要求。

1 弹下点测高原理分析

弹下点测高几何关系如图1所示。

图1 弹下点测高几何关系

导弹沿AC方向飞行,AC方向即合速度方向V方向,天线波束中心指向AO方向,波束中心指向和合速度的夹角为θ。

弹下点测高采用线性调频信号能够提高测高精度并且保证作用距离,发射信号模型为

(1)

其中t为快时间,Tp为脉冲宽度,Kr>0为调频率,“rect[·]”为矩形窗函数

(2)

雷达接收到弹下点所在距离单元回波之后,将其进行混频和正交相干检波成为正交双通道信号,其回波信号为

(3)

其中,A为与天线增益、地面垂直散射系数和距离分辨单元面积有关的常数,c为自由空间中的电磁波传播速度,R(ta)为ta时刻雷达到该点目标的高度信息。

雷达以一定脉冲重复频率发射线性调频信号,收到回波后处理流程如图2所示。

图2 测高算法处理流程

1)距离向匹配滤波:距离向参考匹配滤波函数H(t)为

(4)

2)方位匹配滤波:方位匹配滤波在时域表达式为

(5)

其中fdc=2vcosθ/λ为该距离单元对应的多普勒中心频率,Ka=-2v2sinθ/(λR)为多普勒调频率,R为距离单元,fdc,Ka可以从惯导参数和几何关系中进行估计。

3)OCOG法估计回波半功率点:

方位向匹配滤波后提取零频附近的回波,即图中O点对应多普勒的回波进行前沿估计;其中OCOG回波前沿[6]提取方法为:计算波束中心点方位波束宽度覆盖范围内斜距差对应距离窗宽,在重心基础上向前取该窗宽一半的位置用于计算实际斜距。重心计算公式为

(6)

(7)

其中,G为回波重心,n为采样点序号,pn为回波信号幅度,W为等效矩形脉冲宽度;回波前沿半功率点为ΔN=G-W/2,H为估计高度,Rτ为距离单元长度,ΔN为回波半功率点,Rmin为距离波门。

H=(Rmin+ΔN·Rτ)

(8)

2 测高算法在TMS320C6678设计与实现

随着作用距离、分辨率等系统指标要求越来越高,系统运算量也越来越大,同时弹上系统受到体积和重量的限制,传统信号处理器ADSPTS201已经不能满足系统实时性要求,该测高算法主要采用TI公司提供的多核DSP芯片TMS320C6678实现。该DSP芯片拥有八核处理器,运算能力非常强。

1)一片C6678拥有8个CPU核,每个核内部有32KB L1D、32KB L1P、512KB L2RAM,共享4MB L3SRAM,每块板卡外挂4GB DDR3 SDRAM。

2)C6678单片处理能力:内核主频1.25GHz,浮点运算能力达到160GFlops。

3)C6678具有丰富的外设接口,支持1×、2×、4×模式的SRIO接口,2×模式的PCIe接口,芯片之间通过HyperLink接口互联,支持千兆以太网GbE等接口,具备大带宽数据传输能力[7]。

2.1 高速并行处理硬件架构设计

针对OCOG测高算法,硬件单板设计如图3所示,该板卡由两片TMS320C6678和一片XCVX7690T组成的运算处理核心,DSP和FPGA之间通过高速SRIO实现高速互联。

图3 硬件平台架构

2.2 任务分配

导弹在飞行过程中速度非常快,要求沿航向每25m网格出一次测高结果,因此对系统的实时性要求非常高。本系统采用两块板卡,四块DSP 的架构,每片DSP处理一个CPI的回波数据,四片DSP乒乓操作,处理不同CPI的回波数据。在一个CPI内方位处理脉冲数为Azmlength,每片DSP八个核按照方位脉冲处理数分配任务,每个核都处理1/8Azmlength的回波数据。

2.3 内存分配

实时回波数据本身比较大,先存放在DDR3上,再通过EDMA把回波数据从DDR3搬到L3上,其他计算变量和缓冲都放在片内的RAM上。

L3有4MB,待处理的回波和一些共用的变量存放在L3地址上,内存分配如表1所示。

表1 L3内存分配

L2有512KB,主要存储处理过程中的缓存数据,由于L2是每个核独有的,每个L2可以处理一个方位脉冲的回波数据,内存分配如表2所示。

2.4 OCOG测高算法并行实现

在本设计中,将内部的L1存储器作为Cache使用,用以加速程序执行效率,程序和内部数据缓冲区放置在每个核的L2存储器中,将接收到的回波数据按矩阵格式放置在外部存储器DDR3中。具体处理流程如图4所示。

图4 OCOG测高算法在C6678上处理流程

1)0核通过SRIO接收到一帧回波,进行系统参数解析;

2)0核每次通过EDMA将FPGA通过SRIO发送过来的回波搬移到DDR3上进行存储,同时进行惯导参数的解析;

3)0核在L3地址上构造匹配滤波函数,并通过FFT将匹配滤波函数从时域转换到频域;

4)0核再通过EDMA将DDR3上的回波数据搬移到L3地址上,通过将回波数据格式转换浮点数形式的函数可以将回波从L3地址搬移到L2地址上,此时八核可以同时进行距离向匹配滤波处理,即每个核处理一条方位脉冲的回波,回波通过FFT从时域转到频域,然后跟匹配函数相乘再通过IFFT转到时域,完成匹配滤波;滤波处理完成以后,八核之间进行同步操作,八条距离线数据通过存储方案存储在DDR3矩阵里面;

5)0核在L3地址上构造方位向匹配滤波函数,0核从DDR3矩阵中一次读出八条方位线数据,八核同时进行解交织操作将方位线数据存在L2地址上,然后进行方位向匹配滤波;

6)方位向数据匹配滤波结束以后,0核抽取零频附近的脉冲数据进行回波前沿估计;

7)0核利用OCOG法估回波的半功率点,进行高度的解算。

3 实验结果及分析

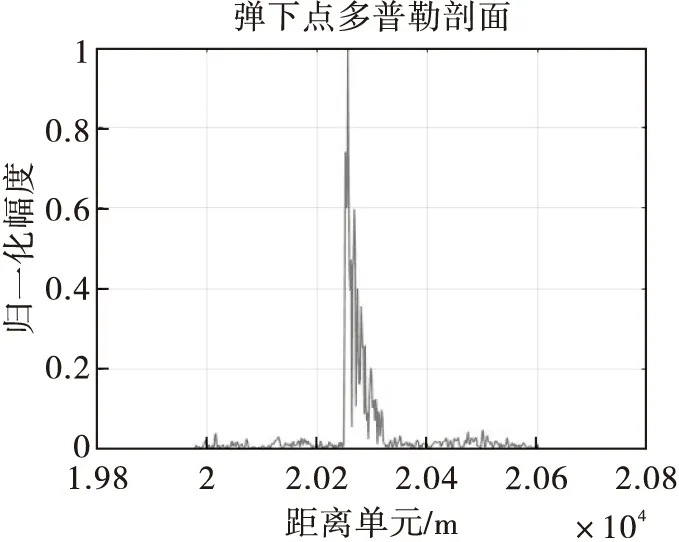

利用某型号的实测数据进行分析,输入的距离向点数为4096点,方位向点数为128点;完成方位向匹配滤波后的结果如图5所示,零频的数据如图6所示,测高结果的误差如图7所示;八核并行处理的情况下,TMS320C6678运行频率为1.25GHz,收数和距离向脉冲压缩消耗18447777个时钟周期,测高模块消耗1145452个时钟周期,则整个测高处理时间为10.67ms,传统的ADSPT201处理同样大小的回波数据则需要45.6ms,对于测高模式,系统要求每个CPI处理流程应小于20ms,因此本文提出的八核并行处理方法能够大大节约时间满足实时性要求,并且测高结果与实际高度一致。

图5 实测数据斜距多普勒图

图6 零通道的剖面图

图7 测高结果和实际高度的差值

4 结束语

本文首先介绍OCOG测高算法和C6678的基本特征,接着分析OCOG测高算法的任务规划和具体实现过程,并给出了DSP处理的流程图,最后通过实测数据处理说明,本文提出的OCOG测高算法并行处理方案的并行处理效率符合期望,能够满足系统的指标要求。