雷达自适应副瓣对消的FPGA工程实现

2021-07-02王佳鑫

王佳鑫

(中国电子科技集团公司 第二十研究所,陕西 西安 710068)

0 引 言

随着雷达干扰手段的不断增强,抗干扰能力已经成为重要的雷达技术指标,根据不同雷达分机(天线、发射机、接收机或信号处理等)可采取不同的抗干扰策略[1]。与天线有关的抗干扰技术可分为两类,一类是尽量避免或减少干扰进入接收机,另一类则是通过对干扰信号的特性进行对应的处理。通常一部分雷达会应用多种抗干扰技术,如使用低副瓣天线降低干扰信号进入,同时通过副瓣消隐(Sidelobe Blanking,SLB)、副瓣对消(Sidelobe cancellation,SLC)、脉冲压缩以及频率捷变等去除干扰信号,提取目标。自适应旁瓣对消是通过设计辅助天线阵列采集干扰信号,并与主阵面信号进行计算来实现干扰抑制[2]。

工程实现中,雷达信号处理需要大量的复数和浮点运算,传统硬件多采用数字信号处理器(Digital Signal Processing,DSP)作为主要处理单元,FPGA作为数据缓存和传输接口单元。随着FPGA性能大幅提升,很多信号处理功能都可由FPGA单独完成,节省了芯片间数据传输的时间,特别在雷达周期小的应用场景中其稳定的时效性具有明显的优势。

本文介绍了自适应副瓣对消原理,并根据FPGA计算和IP核特点对公式进行推演,提高处理效率。同时在某型相控阵雷达中进行测试,对比不同测试条件下副瓣对消的结果,给出具体应用的建议。

1 副瓣对消原理

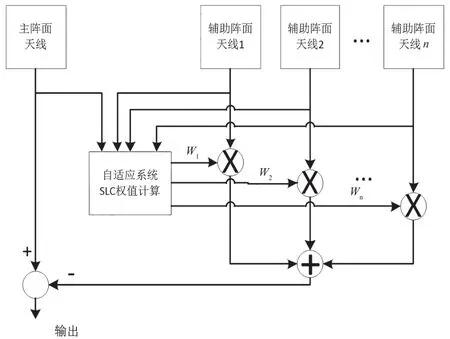

自适应副瓣对消的基本原理是通过辅助天线阵列接收干扰信号,自适应计算干扰的方向和功率,随后调整天线接收方向图,将零点置于干扰方向上[2]。辅助阵列可以是独立的接收天线,也可以是主天线的部分接收单元,但要求辅助阵的方向图主瓣尽可能宽,幅度应该略大于主天线的第一副瓣,从而获得更好的干扰抑制效果。图1是典型的自适应副瓣对消系统原理框图。

图1 副瓣对消工作原理框图

n为辅助天线个数,辅助天线接收到干扰信号和主天线的信号线性组合进行对消,问题是需要寻找到一组合适的权值Wn=[W1,W2,…,WN]来最大限度的对消干扰。由于干扰信号的随机性以及假设信号为线性组合,采用随机过程线性预测理论进行分析[1,2]。辅助天线阵列可以用N维矢量Xn=[X1,X2,…,XN]表示。那么干扰信号样本组可由协方差矩阵M=E[Xn*XnT]表示,主天线信号X与Xn的关系通过协方差矢量S=E[XXn*]表示。最优权值W应使得均方预测误差为最小的准则确定,即:

式中,Z是系统输出,使PZ最小时可得到:

式中,μ是任意常量。最终SLC的输出为:

2 FPGA算法实现

副瓣对消的难点在于求解式(2)的权值时需要实时计算N阶矩阵M和S,包含了大量的复数乘法和矩阵转置求逆等计算,且辅助阵列数N和采样点数K越大,计算复杂度越高,耗时越长。本文提出的FPGA解决方案在某型有源相控阵雷达中得到了测试和验证。此雷达主天线有128个T/R组件,通过馈电网络合成主天线波束。主天线上方设置有3个辅助天线,用于副瓣对消。

2.1 SLC工作流程

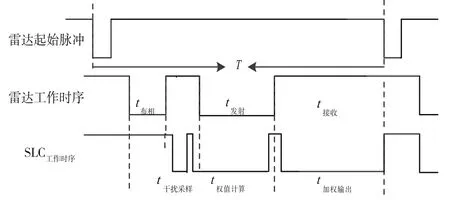

副瓣对消的工作流程可分为干扰采样、计算权值以及加权输出3个阶段。为了获得稳定天线指向的干扰信号,并尽可能减少自身雷达发射信号产生的强回波对权值计算的影响,干扰采样时间应该在天线阵面完成布相之后和发射期开始之前。干扰采样接收完成后立即启动权值计算,并且在接收期开始前完成,以确保实时地对回波信号加权输出副瓣对消结果。SLC工作时序如图2所示。

图2 SLC工作时序图

在一个相控阵雷达工作周期T内,天线布相完成,主阵面和辅助阵列的指向稳定后,打开接收机,AD采样模块开始对干扰信号进行采样,经下变频和抽取得到4路各100点的干扰信号,送入SLC模块进行权值计算。利用雷达发射期计算权值,并且在接收期到来之前完成计算,随后在接收期回波采样时通过式(3)实时加权输出对消结果。

根据雷达时序设计的不同,留给权值计算的时间可能很短,在设备硬件条件允许的情况下,副瓣对消可直接在接收机的FPGA中进行,AD采样和下变频完成后直接进行计算,减少板间数据传输时间,提高效率。本文方案由于主阵与辅阵的AD采样不在同一硬件模块,故通过高速串口发送给信号预处理模块进行权值计算和加权输出。

2.2 SLC权值计算

在FPGA中计算式(2)实现矩阵运算较为复杂,那么辅助天线通道的协方差矩阵M可写为:

主天线通道与辅助天线通道的互相关矩阵记为:

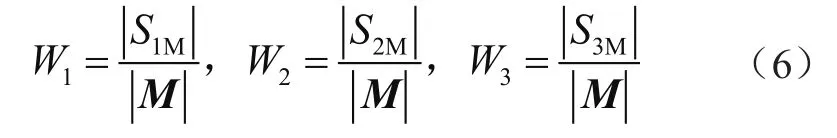

矩阵求逆最终可转化为行列式求解问题,且不同行列式是由多个基础协方差以不同的排列组合构成的,所以只需要运用复数乘法器和累加运算,再通过逻辑时序实现行列式计算得到权值。

第一步,接收干扰信号,存入双口RAM,接收完成后启动多个复数乘法器同时计算SiMij(i,j=1、2、3)。

第二步,利用行列式计算公式,复用上一步的复数乘法器计算行列式结果,即得到|S1M|、|S2M|、|S3M|以及|M|的数值,结果为复数。

第三步,将式(6)中的复数除法转换为复数乘法得到权值W。在雷达接收期,使用3个复数乘法器对回波信号进行流处理,实时输出副瓣对消结果Z=X-W1X1-W2X2-W3X3。

需要注意的是在副瓣对消时,主瓣回波也会同时对消,为了不减少主瓣增益以保留小目标信号,可以进行主瓣保护。本文利用主天线和辅助天线的方向图特性做了简单的主瓣保护,利用干扰采样数据计算主天线和辅助天线的回波功率,若主天线功率大于辅助天线说明此时天线指向的干扰从天线主瓣进入,不进行对消。反之干扰从天线副瓣进入,进行对消。

根据分析,FPGA性能需求主要在复数运算和逻辑时序控制上,存储空间需求不大。本文采用Xilinx Kintex系列FPGA,型号为XC7K420T、Logic Cells 416960、DSP Slices 1680以及Block RAM Blocks 30060kb。使用复数乘法器IP核(Complex Multiplier 6.0),选择Mults构建方式,通过DSP Slices(一个乘法器占用3~4个Slices)实现更高工作频率下的复数乘法,输出延时4~6 h。实现3个辅助阵面的副瓣对消运算只需要5%~10%的DSP Slices资源。本文计算方法在FPGA全部使用整型计算,复数乘法之后会有溢出现象。因此在每级的复数乘法器后扩大输出寄存器位数,并在最终权值计算完成后进行截位,以获得更高的精度[3]。

3 试验结果

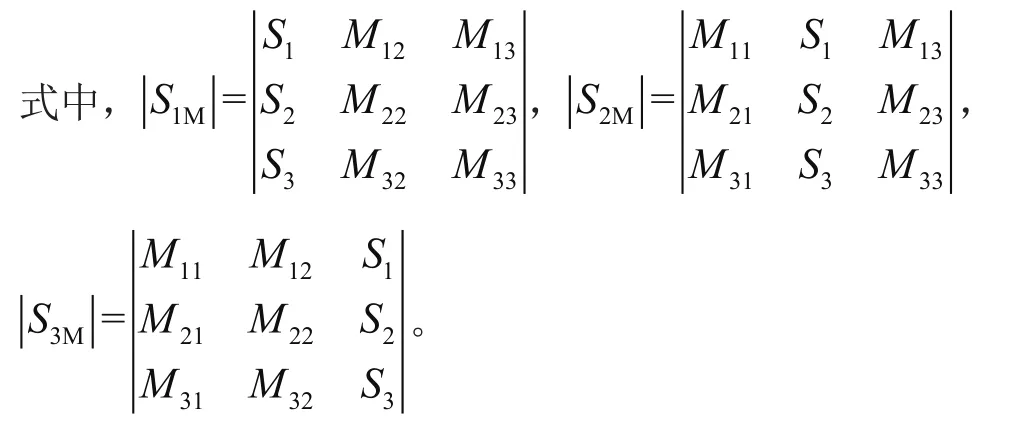

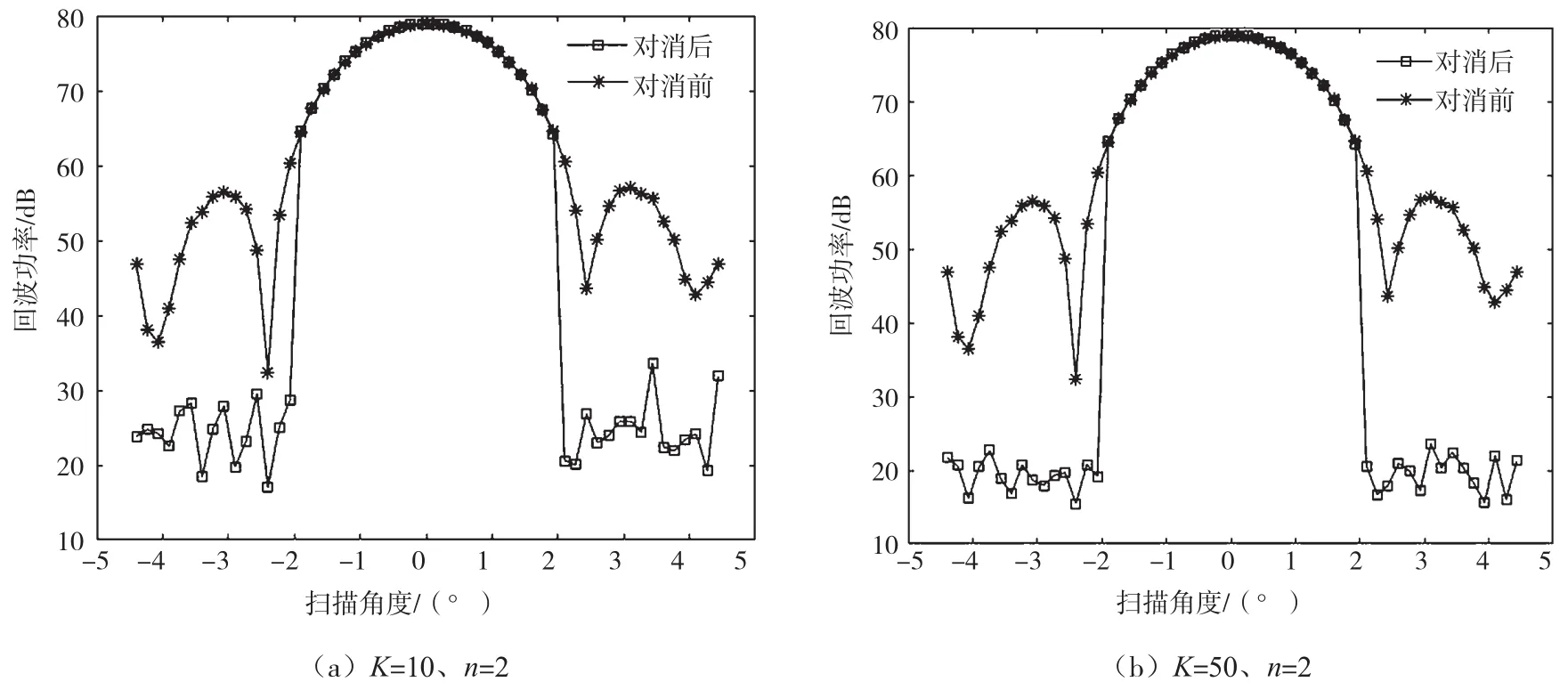

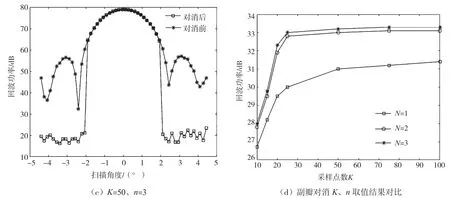

影响副瓣对消效果的因素包括干扰源数R、辅助阵列数n、干扰采样数K以及通道相位一致性等,但根据仿真分析整体系统副瓣对消改善因子应不小于25 dB。在某型相控阵雷达的试验中,使用远场测试天线方向图的方法进行测试,在天线法相方位1 km外架设信号源辐射喇叭,天线伺服角度不变,操控天线进行方位电扫,使信号源辐射进入天线主副瓣。经过AD采样,下变频,抽取后求得各指向角度上的平均功率而获得一个“等效方向图”[4]。试验使用1个干扰源(R=1),分别对辅助阵列数(n=1,2,3)和干扰采样点数(K∈[10,100])的对消效果比对,如图3所示。

图3 不同K、N值下副瓣对消结果

从图3可以看出对消增益随着采样点数的增多而增大,但在大于20点的增幅有限,对消增益基本可以保证在30 dB以上。小于20点的对消增益下降较多,并且对消后方向图不平滑,起伏较大。同时,当辅助阵列数等于干扰数时,对消增益不如阵列数大于干扰数的结果。并且阵列数越大,对消增益越大,方向图越平滑。副瓣对消计算量对比如图4所示。

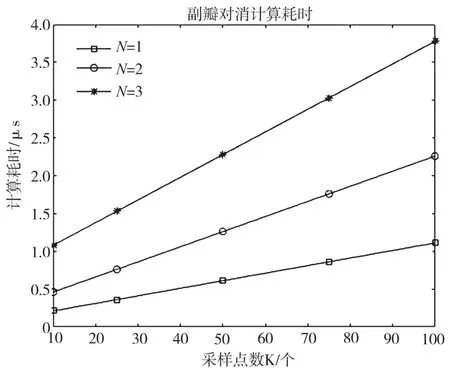

图4 副瓣对消计算量对比

权值计算耗时主要与采样点数和辅助阵数量有关,在100 MHz的FPGA工作时钟下,计算3个阵面100点干扰采样需要大约3.75 μs,可以满足高重频下的副瓣对消。根据测试结果,对于干扰源较少,在选择干扰点数大于等于20,辅助阵数大于等于2时,副瓣对消的效果基本满足,再增加点数和阵列对结果增益帮助不大。若干扰源较多,可通过增加辅助阵列来提高对消效果,但同时也增加了计算时间。

4 结 论

介绍自适应副瓣对消的原理以及在FPGA中的实现方法,通过试验验证了此方法的可靠性和实时性,比较了在不同辅助阵面数和干扰采样数的副瓣对消结果,均满足雷达抗干扰要求,同时给出了在FPGA中实现算法的建议。