数字锁相环的相位噪声分析

2021-06-09张占荣王云飞屈美霞赵丽

张占荣,王云飞,屈美霞,赵丽

(1.鄂尔多斯生态环境职业学院机电工程系,内蒙古 鄂尔多斯 017010;2.鄂尔多斯生态环境职业学院基础部,内蒙古 鄂尔多斯 017010;3.山西大学软件学院,山西 太原 030013)

现代频率源一般是由直接频率合成、间接频率合成和直接数字频率合成这三种合成技术实现的[1]。其中,最早出现的是直接合成频率源,原理简单,工作稳定,但体积大,成本高。间接合成频率源与直接合成技术相比,电路结构稍显复杂,但拥有集成度高、频谱纯净、相位噪声低、输出信号稳定、易调控等优点。而直接数字频率合成器的频率切换快,分辨率高,但是电路更复杂,输出信号的上限频率不高。因此,兼顾上述优点的数字锁相环(digital phase-locked loop,DPLL)在电气、雷达和自动化等领域中被广泛应用。

相位噪声描述的是频率信号的短期稳定性,常被用来鉴别DPLL性能的好坏。在通信系统中,信号源后级的压缩放大器和倍频会导致相位噪声的固有衰减。因此,噪声的主要形式是相位噪声,相位噪声越小,对信号传输的影响越小。当信号源作为本振时,相位噪声会与信号一同出现在解调端,恶化信噪比,进而降低系统的分辨能力,增加误码率[2]。

因此,研究低相噪、高可靠性的数字频率合成器是当代锁相技术发展的必然趋势。研究相位噪声的影响因素可以为优化DPLL的相位噪声提供可靠依据。

1 锁相环基本理论

1.1 锁相环的电路结构

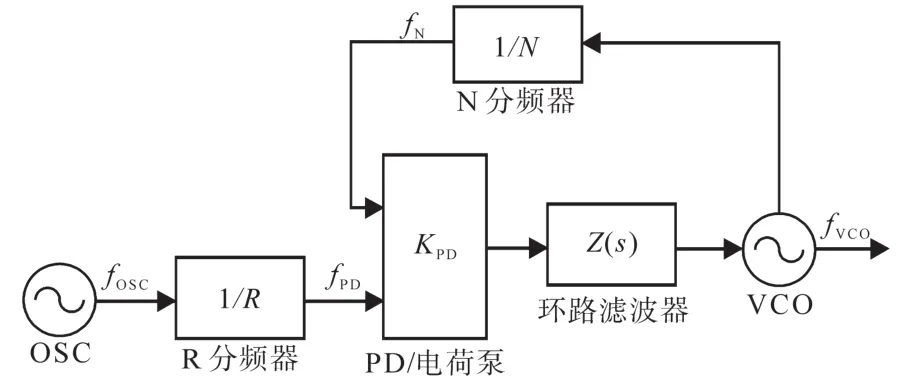

图1给出了DPLL电路的基本结构。晶体振荡器(oscillator crystal,OSC)作为参考信号经过R分频器输入鉴相器(phase detector,PD),PD比较参考信号与压控振荡器(voltage controlled oscilla⁃tor,VCO)输出信号的相位,得到电压信号,与二者的相位差成线性关系。环路滤波器将信号中的高频分量和噪声滤除后,送入VCO,输出一个与其相对应的频率信号,反馈给PD,再次与OSC分频后的相位进行比较,直到二者相位差为零,进入锁定状态,此时DPLL输出一个频率稳定的单频信号。

图1 锁相环电路结构图Fig.1 Circuit structure diagram of PLL

图1中,KPD为鉴相增益即电荷泵增益,可以理解为电荷泵所提供的电流大小;Z(s)为环路滤波器阻抗;fOSC,fPD,fN和fVCO分别为参考信号频率、鉴相频率、反馈频率和输出频率,其中fVCO=N fOSC/R。电路的开环传输函数为

式中:KVCO为VCO增益。

考虑整个闭环回路响应可以得到对应闭环传输函数为

1.2 相位噪声定义

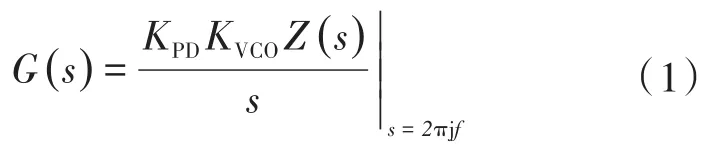

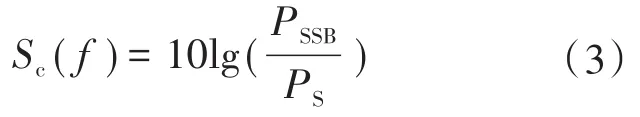

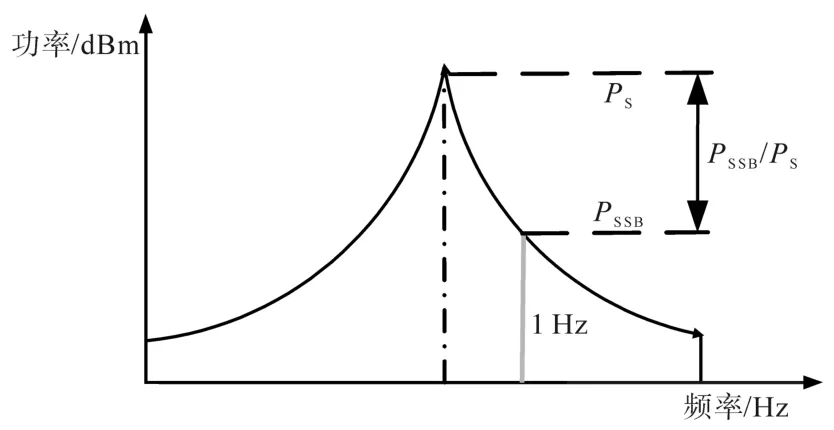

相位噪声Sc(f)的定义如图2所示,即在某一频率处,1 Hz带宽内的单边带噪声功率PSSB与总功率PS的比率,单位dBc/Hz,计算公式如下:

图2 相位噪声定义Fig.2 Definition of phase noise

2 振荡器的相噪分析

锁相环的输入参考晶振和VCO均属于振荡器。振荡器的相位噪声会随着偏离载体频率值的增大而升高,可以将其建模为[3]

式中:F为有源器件的噪声系数;k为玻尔兹曼常数;T为温度,K;P为有源器件的输入功率;QL为电感的有载品质因数。

由式(4)看出,输入功率越高、温度越低、噪声系数越小,VCO的相位噪声越小。若其他参数为定值,那么相位噪声会随着fVCO按20lg fVCO规律变化。QL被定义为工作频率下电感的电抗与等效电阻实际比值,即QL=XL/RL。电感中的等效电阻会抑制回路的振荡,因此为得到最佳相位噪声,QL越大越好。

3 电荷泵的相噪分析

DPLL结合电荷泵与鉴频鉴相器展现了优于传统锁相环的线性范围和捕获时间。并且,电荷泵的前端器件所引入的噪声均可看作在电荷泵输出端产生的噪声。

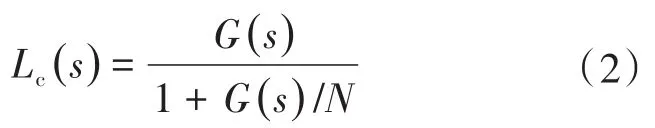

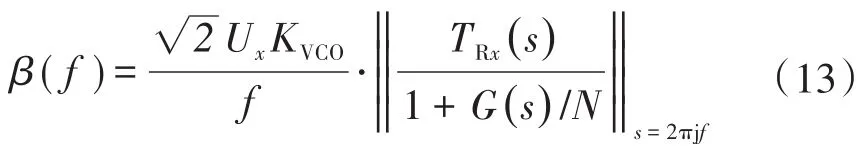

图3是以LMX2541芯片组成的DPLL电路为例,对比仿真计算与实测的DPLL相噪特性曲线。

图3 仿真计算与实测的DPLL噪声曲线Fig.3 Curves of modeled DPLL noise and measurement

可以看出,DPLL综合相位噪声基本由闪烁噪声(即1/f噪声)和白噪声组成,1 kHz频偏内的相噪则需要考虑参考信号噪声的影响。对于早期的整数锁相环和较低的鉴相频率处,可以认为白噪声是锁相环噪声的主要来源。而在较高的鉴相频率处,则需要考虑闪烁噪声和白噪声的组合。

3.1 闪烁噪声特性

在测量过程中,通常采用高鉴相频率、宽环路带宽和固定频率的低噪晶体振荡器来测量1/f噪声。其特性可以概况为以下几点:

1)随着频偏的增大,噪声会以10 dB/10倍频程的速率恶化。利用这一特性可以区分1/f噪声与20 dB/10倍频程速率变化的参考信号噪声。

2)不随鉴相频率变化。假设在fVCO保持不变的情况下,fPD增加M倍,相位噪声随之改善20lgM。然而,由于电荷泵输出的脉冲数也变为原来的M倍,相关噪声随之恶化20lgM,与之抵消。因此,1/f噪声的净影响与fPD无关。

3)随着fVCO的升高,噪声会增加20lg fVCO。在分频值N不变的情况下,当fVCO随着fPD的提高而增加时,鉴相器的基底噪声PDfloor也会增加,导致1/f噪声恶化。当fPD不变时,1/f噪声会随着N的增大而升高。因此,不管以哪种方式增大fVCO,均会引起1/f噪声的恶化。

4)低于1 Hz频偏处的噪声几乎没有变化,可以忽略不计。

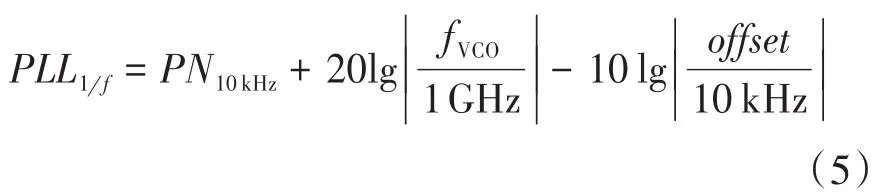

结合上述1/f噪声的特性,可以采用下式中10 kHz归一化频偏(offset)和1 GHz归一化fVCO来表征DPLL的闪烁噪声。

式中:PN10kHz为10 kHz归一化的DPLL噪声基底。

3.2 白噪声特性

DPLL的白噪声特性有以下几点:

2)随着分频值N的增加,白噪声以10lgN的速率增加。尽管分频值N增加K倍,会使噪声增加20lgK,但为保持fVCO不变,fPD会随之减小K倍,导致噪声升高10lgK,因此增加分频值N对白噪声的净影响为10lgN。

3)与闪烁噪声不同,DPLL的白噪声会随着鉴相频率同步变化。

根据上述分析的噪声特性,可以将DPLL的白噪声建模为

式中:PN1Hz为1 Hz标准化DPLL底噪,是不随鉴相频率等参数变化的指标。

3.3 闪烁噪声与白噪声的影响因素

3.3.1 电荷泵增益

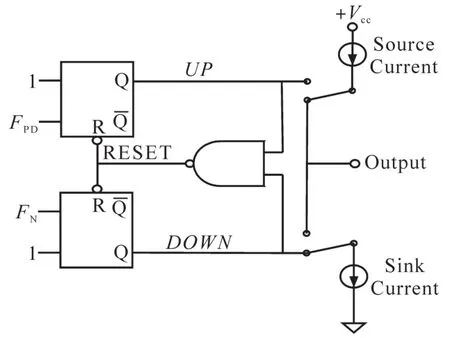

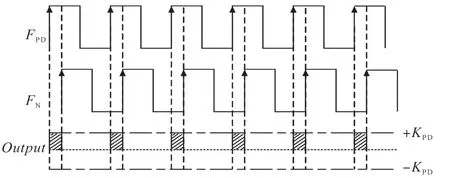

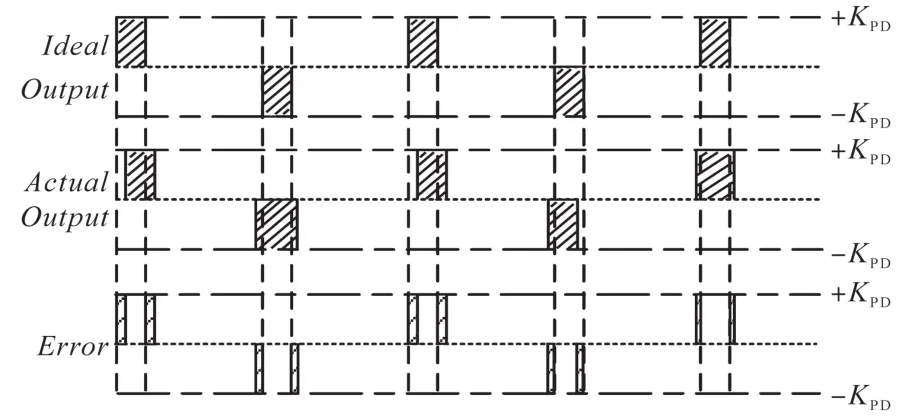

经典电荷泵鉴相器的电路结构如图4所示。电路包含三种工作状态:当UP=1时,只启用正向电流源;当DOWN=1时,只启用反向电流源;当UP=0,DOWN=0时,关闭电流源。该电路的输出脉冲如图5所示。

图4 传统电荷泵鉴相器结构图Fig.4 Structure diagram of traditional charge pump phase detector

图5 电荷泵鉴相器的输出Fig.5 Output of charge pump phase detector

图5为电荷泵鉴相器的理想输出结果。在实际工程中,电荷泵存在开启延时、回路间串扰以及关闭瞬间的泄露等问题[4],会导致VCO调谐线上出现交流调制,使得理想输出与实际输出相位之间出现误差,如图6所示。该误差会成为毛刺脉冲,对控制信号产生干扰。因此,电荷泵引入的噪声是1/f噪声的主要来源。

图6 电荷泵鉴相器输出相位误差Fig.6 Output phase error of charge pump phase detector

若是利用简单的乘法器提高KPD,那么电荷泵的噪声也会被抬高同样的倍数;若是利用并联电流源的方式提高增益,电荷泵噪声是不相关的,理论上每增加1倍的电荷泵增益,相位噪声就会改善3 dB/10倍频程。因此,电荷泵增益KPD对DPLL的相噪影响较大,采取适当的措施,即可获得理想的相位噪声。

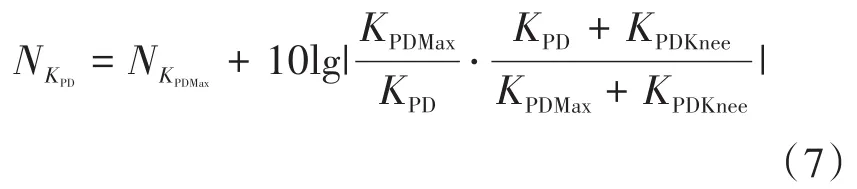

一般来说,当环路滤波电路中的电容过大,导致快速锁定或补偿VCO增益差异时,需要更高的电流,或者相位噪声开始恶化,最好使用最高的电荷泵增益来获得最佳相位噪声,可以将此时的增益称为KPDKnee[5]。如果电荷泵电流对相位噪声没有影响,则该项为零。由于最高电荷泵电流(KPDMax)基本上对应最佳DPLL相位噪声,所以在其他电荷泵电流下的噪声可以建模为

3.3.2 输入参考信号转换率

输入信号转换率越高,对传输路径上的杂散以及R分频器噪声的抗干扰能力就越强,可以有效改善DPLL的相位噪声,一般转换率每提高1倍,闪烁噪声可以改善6 dB。低频或者低相位信号的转换率比较小,就会导致相位噪声恶化[6]。

3.3.3 频谱仪的校正系数

频谱分析仪会定义一个校正因子,以补偿噪声带宽和3 dB带宽之间的差异而导致的微小误差[7],在相噪的建模过程中需将该系数考虑在内。

4 环路滤波器的相噪分析

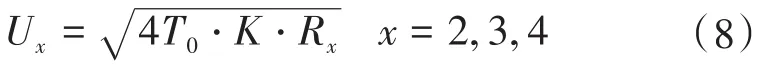

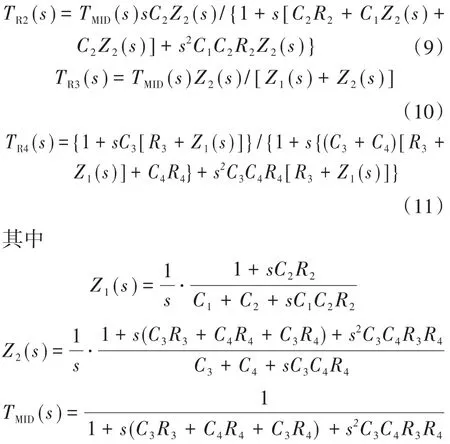

环路滤波器一般采用三阶无源低通滤波器,其中电阻产生的热噪声是恶化DPLL相噪的主要来源。图7给出滤波器的电路结构,将电路如图分为三个部分来计算环路滤波器的相位噪声模型。

图7 环路滤波器电路结构Fig.7 Loop filter circuit structure

电路中各个电阻的电压为

式中:T0为环境温度,T0=300 K;Rx为电阻值。

电阻R2~R4的热噪声为[8]

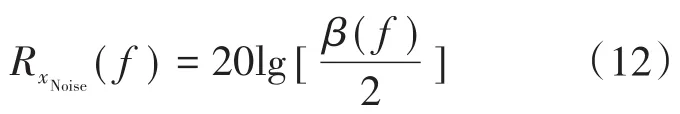

由文献[3]提出的理论可知,泄漏的参考噪声与信号的调制指数有关,利用该指数即可导出各电阻Rx所引入的相位噪声为

式(12)中调制指数β(f)定义如下:

5 相位噪声仿真与验证

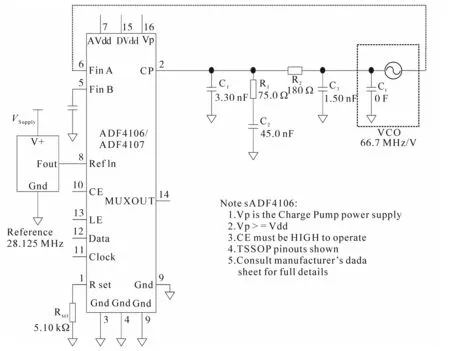

为验证锁相环相位噪声的影响因素,系统选用相噪基底为-166 dBc/Hz的鉴频鉴相器ADF4106以及压控灵敏度为66.7 MHz/V的VCO模块,结合ADIsimPLL仿真软件来搭建输出频率为8.2 GHz的锁相环,电路原理如图8所示。环路的元件值设置为R1=75 Ω,R2=180 Ω,C1=3.3 nF,C2=45 nF,C3=1.5 nF。将电荷泵增益减小40 V/rad、环路滤波电路的电阻值变为R1=100 Ω,R2=430 Ω,设计两组对比实验,定性分析电荷泵增益与电阻热噪声对PLL相噪的影响,最终得到图9所示的仿真结果。图9中,点线为VCO的相位噪声,划线则表示环路滤波电路的相位噪声,点划线为鉴相器PD的相位噪声,实线描述了整个电路总的相位噪声。可以看出,对于带内噪声而言,环路相当于低通滤波器,而对于VCO引入的噪声,环路则相当于高通滤波器。

图8 数字锁相环电路原理图Fig.8 Circuit diagram of DPLL

图9a电路的相噪均在-112 dBc/Hz以下,噪声性能最佳;而图9b中鉴相器的相噪随着电荷泵增益减小而恶化,进而导致电路的相噪性能降低;图9c描述了增加环路中电阻值引入更多的相位噪声,导致整个电路相噪恶化的过程。

图9 锁相环相位噪声仿真曲线Fig.9 Phase noise simulation curves of PLL

综合上述实验可看出:在其他参数不变的情况下,选择合适的环路参数,结合高电荷泵增益,就可以获得最佳相位噪声。

6 结论

DPLL相位噪声的来源主要是环路内振荡器、电荷泵鉴相器和环路滤波器引入的噪声。利用数学建模给出了上述模块的相位噪声计算公式,概述并定性分析了相噪的几种影响因素,设计仿真进行理论验证,为优化DPLL的相位噪声提供了参考依据。