抑制SiC MOSFET瞬态电压尖峰的改进驱动电路设计

2021-06-07王文月牛萍娟

王文月,牛萍娟

(1.天津工业大学 电气工程与自动化学院,天津300000;2.天津工业大学 电子与信息工程学院,天津300000)

近些年,随着电力电子技术的发展,航空、电动汽车、新能源发电及石油钻井等领域对电力电子变换器提出更高的要求,即实现高压、高频、高功率密度[1]。因此以SiC MOSFET为代表的宽禁带半导体器件因其高开关速度、高开关频率及高热导率等[2-5],受到人们广泛关注。然而随着SiC MOSFET开关频率及速度提高,电力电子变换器受电路中寄生参数影响加剧,关断瞬态电压尖峰更为严重。瞬态电压的尖峰不仅危及开关管的安全,也会降低电力电子变换器的功率密度,加剧电力电子变换器电磁干扰[6-8]。目前现有抑制电压尖峰方法大多牺牲了开关速度,从而影响SiC MOSFET开关损耗及变换器效率等。因此,本文在分析电压尖峰产生原理基础上,在注入栅极电流抑制电压尖峰前提下,提出了一种在栅源极增加有源箝位电路的改进驱动方法,改进后的驱动电路具有抑制尖峰效果好、开关损耗较小、控制方法简单特点。本文首先分析瞬态电压尖峰产生原理,其次分析了改进驱动电路工作原理,最后在双脉冲测试平台验证了该改进驱动电路的实用性。

1 SiC MOSFET瞬态电压尖峰产生原理

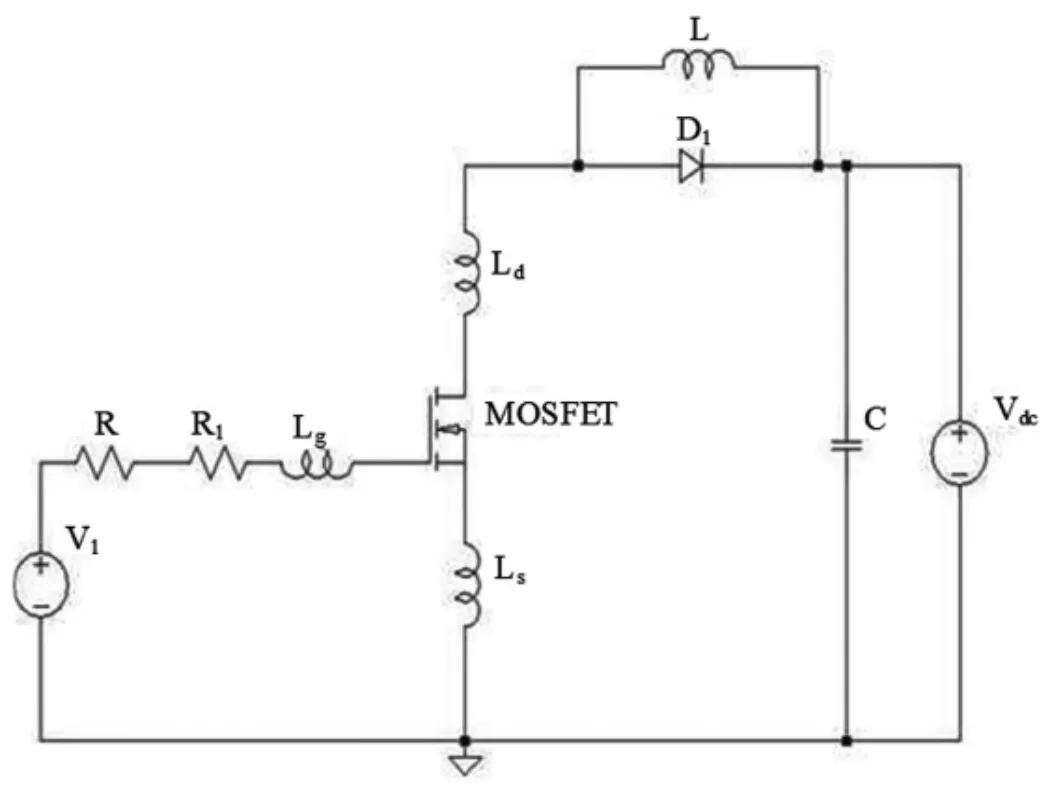

为了分析SiC MOSFET瞬态电压尖峰产生原理,采用如图1所示测试电路,图中:Vdc直流母线电压,R驱动电阻,C支撑电容,L负载电感,SiC MOSFET及SiC二极管D1,考虑SiC MOSFET关键寄生参数为:栅极驱动电阻R1,栅极引脚封装电感Lg,源极引脚封装电感Ls,漏极引脚封装电感Ld。为了方便分析,Lg、Ls与Ld分别为SiC MOSFET各引脚封装电感与相连接引线电感之和。与此同时,根据SiC MOSFET关断特性,将关断过程分为4个阶段[9],图2为关断过程示意图。

图1 测试电路

图2 SiC MOSFET关断过程

SiC MOSFET关断过程,[t0,t1]阶段,驱动电压为低电平,输入电容通过驱动电阻R和源极电感Ls放电,此过程漏极电流id和漏源极电压Vds基本不变,栅源极电压Vgs下降。

[t1,t2]阶段,漏极电流id与栅源极电压Vgs基本保持不变,漏源极电压Vds一直上升至母线电压Vdc。

[t2,t3]阶段,漏极电流id下降,续流二极管D1开始正向导通,负载电流从SiC MOSFET向续流二极管转移,栅源极电压Vgs开始下降至开启电压Vth,SiC MOSFET开始关断,漏极电流id降为0,在此阶段由于电流变化率快,在回路寄生电感Ls与Ld上产生压降,这部分压降加在SiC MOSFET漏源极两端,产生电压尖峰。基于基尔霍夫电压定律可知,Vds(t)+(Ls+Ld)did(t)/dt=Vdc+VD1(t)。忽略二极管正向导通电压,得出:Vds(t)-Vdc=-(Ls+Ld)did(t)/dt,因此电压尖峰Vp=-(Ls+Ld)did(t)/dt,其中did(t)/dt可以用式子did(t)/dt≈iggfs/Cgs表示[10]。

[t3,t4]阶段,栅源极电压Vgs降至低电平,SiC MOSFET完全关断。

2 改进驱动电路工作原理

由分析可知,抑制瞬态电压尖峰问题最传统的抑制方法是增加驱动电阻、增加缓冲电路[11-12]和优化器件封装结构及功率回路寄生参数[13]。增加驱动电阻,能够抑制SiC MOSFET尖峰问题,但同时会增加开关过程损耗。增加缓冲电路对关断电压尖峰有好的抑制效果,但由于缓冲电路存在无源器件会带来额外损耗。优化器件封装结构成本较高且一般耗时比较长,PCB布局优化则需要考虑大量的因素。另一类主要是采用新型的驱动电路进行电压尖峰抑制,该方法往往成本较高、控制复杂、实现难度大[14]。

图3 改进驱动电路原理

综上所述,为了尽可能不影响SiC MOSFET开关速度、增大器件开关损耗。本文基于有源箝位电路与注入栅极电流抑制电压尖峰[10]方法,提出一种在栅源极通过控制三极管开通与关断的辅助之路,注入栅极电流方法对瞬态电压进行了抑制。

该改进的驱动电路工作原理如图3所示:经过第1节的分析可知,在SiC MOSFET关断过程([t2,t3]阶段),可以通过减小ig进而改变did(t)/dt来抑制开关过程电压的尖峰。因此可将注入栅极电流抑制电压尖峰与有源箝位电路结合,在SiC MOSFET器件关断电压尖峰产生的阶段对其进行抑制。首先有源箝位电路中分压检测电路根据栅源极获取的电压信号控制三极管Q1开通与关断,Q1开通时,外接电源对电容充电,三极管Q2开通之前控制时间由电容充电时间决定;Q2开通,外接电源对栅极电流进行注入,进而减小ig,减小did(t)/dt进而抑制电压尖峰。Q1关断时,Q1控制Q2也随之关断。此改进驱动方法无需产生单独控制脉冲,降低了电路控制复杂度。

3 实验分析

为了对抑制瞬态电压尖峰的改进驱动电路有效性及实用性进行验证,搭建了双脉冲测试平台,其电路具体原理如图1所示,选用科瑞C2M0080120D型号SiC MOSFET和C4D20120型号SiC二极管。测试电路具体参数为:直流母线电压Vdc=400V、驱动电阻R=10Ω、负载电感L=500uH、开关频率100kHz。改进驱动电路如图3所示,具体设计参为:R2=3kΩ,R3=10kΩ,C=1nF,R4=1Ω,R5=84.5kΩ,Vcc=12V,R6=6.3Ω。

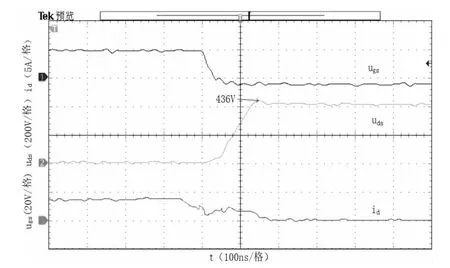

图4-图6,分别给出了传统采用RCD抑制电压尖峰波形、典型设计驱动电路抑制电压尖峰波形及本文所提出的改进驱动电路抑制电压尖峰波形。从实验结果分析可知,本文提出的改进驱动电路与传统及典型的抑制电压尖峰方法相比,关断过程电压尖峰的抑制效果相当。但是采用RCD吸收电路会使器件开关过程产生额外损耗,导致关断损耗增大。典型驱动电路通过控制MOSFET开通与关断的辅助之路完成栅极电流注入进而抑制了电压尖峰,该方法由于采用MOSFET控制元件,需单独控制信号。因此基于以上所述,本文通过对驱动电路改进,如表1所示,实现了对电压尖峰有效抑制,且采用改进控制三极管的辅助支路结构相对简单。

图4 传统抑制电压尖峰方法波形

4 结束语

本文所提出的改进驱动电路设计,将有源箝位电路与注入栅极电流抑制电压尖峰方法进行结合,通过箝位电路中分压检测电路检测栅源极电压信号控制三极管导通与关断,进而将电流注入到栅极,在牺牲较少损耗、无需产生单独控制信号的情况下,对电压尖峰进行有效抑制,最后,通过实验验证了该改进驱动电路的有效性。

图5 典型抑制电压尖峰方法波形

图6 改进驱动电路抑制电压尖峰方法波形

表1 不同抑制电压尖峰方法对比