Si/SiC 混并联结构主动温度控制

2021-06-05何志志李宗鉴

尹 庚,何志志,李宗鉴

(1.湖南大学信息科学与工程学院,长沙 410082;2.湖南大学电气与信息工程学院,长沙 410082)

碳化硅SiC(silicon carbide)作为一种新型的宽禁带半导体材料,相比于传统的Si 半导体材料,具有禁带宽度大、击穿电场高和导热率大等特点,被认为是制备高温、高频、大功率器件的理想材料之一。但是SiC 材料的生产工艺不成熟以及生产成本高[1],阻碍了SiC 半导体器件的大规模应用。文献[2]提出了SiC JFET 和Si IGBT 的并联结构,该结构结合了SiC JFET、Si IGBT 的优点,相对单独的Si IGBT,开关损耗降低了70%,而成本并未大幅度增加;文献[3-6]详细分析了Si IGBT/SiC MOSFET 并联结构内部电流分配关系和动态开关过程;文献[7-9]关注Si IGBT/SiC MOSFET 并联结构损耗和成本优化问题,均未考虑Si/SiC 并联结构中两种器件之间的温度平衡问题。然而,功率半导体器件内部不同材料的热膨胀系数不同,其工作过程中产生的热量会导致器件老化甚至损坏[10-12],因此有必要控制功率半导体器件温度,以提高功率变换器的可靠性。到目前为止,大部分文献提出的温度控制方法都是适用于独立的Si 功率器件或者SiC 功率器件,还没有适用于Si/SiC 混并联结构的温度控制方法。但在Si/SiC 混并联结构损耗优化过程中,小电流SiC MOSFET 容易出现温度过高的现象,因此需要一种Si/SiC 混并联结构主动温度控制方法来有效解决小电流SiC MOSFET 温度过高的问题。

因此,本文提出一种适用于Si IGBT/SiC MOSFET 混并联结构的主动结温控制方法。首先分析了混并联结构的工作原理及驱动时序,然后建立混并联结构的损耗计算模型,分析关断延时Toff_delay对混并联结构内部器件功率损耗分配的影响,基于损耗计算模型实现混并联结构温度平衡。设计了开关频率为20 kHz、功率为9 kW 的DC-DC Buck 变换器,进行了实验验证。

1 Si/SiC 混并联结构工作原理

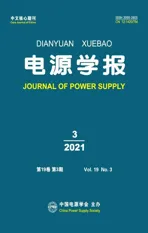

Si/SiC 混并联拓扑结构如图1 所示。其中,以大电流Si IGBT 为主器件、小电流SiC MOSFET 为辅助器件,组成Si IGBT/SiC MOSFET 混并联结构。混并联结构结合了两种器件的优点,在低电流等级时SiC MOSFET 导通大部分电流,而在高电流等级时Si IGBT 导通大部分电流,从而降低了器件的导通损耗。

图1 混并联结构拓扑Fig.1 Topology of hybrid pair

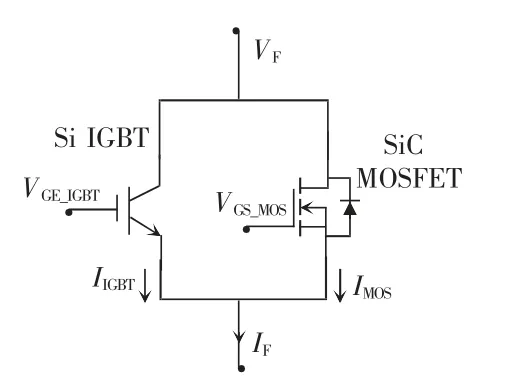

双极性Si IGBT 正向通流能力强,导通损耗小,但由于漂移区电导调制效应,Si IGBT 在关断过程中会产生拖尾电流,因而产生较大的关断损耗。而属于单极性器件的SiC MOSFET 具有开关速度快、无拖尾电流和开关损耗小的优点,因此在混并联结构关断时,可以采用特殊门极驱动时序,使IGBT ZVS 关断而SiC MOSFET 硬关断,从而减小器件总的开关损耗。混并联结构门极驱动时序如图2 所示,Si IGBT 先关断,而SiC MOSFET 延时一段时间后再关断,从而实现Si IGBT 的ZVS 关断,减小器件损耗。

图2 混并联器件驱动时序Fig.2 Drive time-sequence of hybrid pair device

为详细讨论混并联结构的特殊关断模式对关断损耗的影响,根据文献[13],本文采用1 200 V/25 A Si IGBT(IGW25N120H3)作为主器件、1 200 V/12.5 A SiC MOSFET(C2M0160120)作为辅助器件组成Si IGBT/SiC MOSFET 混并联结构。图3 为混合器件在关断延时时间Toff_delay=0.8 μs、母线电压为600 V、关断电流为15 A 条件下的双脉冲测试关断波形,其中:SiC MOSFET 的门极驱动电压为VGS_MOS、漏极电压为VDS、电流为IMOS,Si IGBT 的电流为IIGBT、门极驱动电压为VGS_IGBT。

由图3 可以看到,在主器件Si IGBT 提前关断后,由于SiC MOSFET 仍然导通,在感性负载下,由Si IGBT 导通的电流被强迫换流至SiC MOSFET,从而使IGBT 两端电压在关断过程中被箝位于SiC MOSFET 的导通压降。由于SiC MOSFET 导通损耗小,Si IGBT 近似于ZVS 关断。而SiC MOSFET 在延时过程中导通了所有电流、并在延时结束后硬关断。

图3 混并联结构关断过程Fig.3 Turn-off process of hybrid pair

2 混并联结构损耗模型

Si IGBT/SiC MOSFET 混并联结构关断模式的特殊性,使得混并联结构中的两个器件损耗分配变得很复杂,给混并联结构损耗的计算带来了很大阻碍。功率器件Si IGBT/SiC MOSFET 官方数据手册中一般会列出主要参数,利用这些参数可以计算出每一个器件在一个开关周期内的开关损耗和导通损耗。但在混并联结构中,由于其特殊开关模式的存在,传统的功率半导体器件损耗计算方法不再适用,需要对混并联结构损耗进行相应的计算以及定义混并联结构损耗分布。

Si IGBT 的总损耗Etotal_IGBT分配为

式中:Eon_IGBT为开通损耗;Econd_IGBT为导通损耗;Eoff_IGBT为关断损耗。

SiC MOSFET 的总损耗分配为

式中:Eon_MOS为开通损耗;Econd_MOS为导通损耗;Eoff_MOS为关断损耗。

通过分析Si IGBT/SiC MOSFET 混并联结构开关特性发现,由于SiC MOSFET 开通速度极快,在本文驱动模式下,Si IGBT 处于零电压开通的工作状态,因此混并联结构开通损耗只与SiC MOSFET有关。然而,在某一功率等级下,Si IGBT/SiC MOSFET 混并联结构关断损耗以及导通损耗随着关断延时Toff_delay的变化而改变,因此本文着重分析不同的关断延时Toff_delay下,混并联结构的关断损耗和导通损耗。

2.1 关断损耗

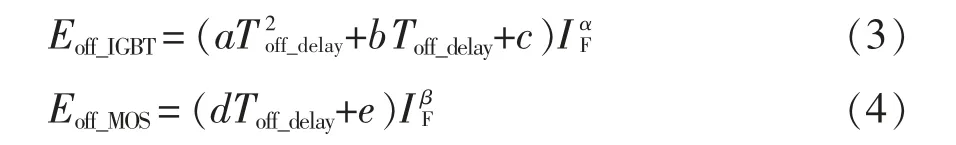

由于Si IGBT 关断过程存在拖尾电流,混并联结构关断过程不是独立器件关断过程。通过分析,混并联结构关断总损耗只与Toff_delay相关,且分为SiC MOSFET 关断损耗Eoff_MOS和IGBT 关断损耗Eoff_IGBT两部分。通过官方数据手册给出的数据结合双脉冲实验数据得到Eoff_IGBT与Toff_delay近似为二次函数关系,Eoff_MOS与Toff_delay近似为一次函数关系,分别表示为

式中:IF为混并联结构正向电流;a、b、c、d、e、α、β 为双脉冲实验提取参数。

2.2 导通损耗

混并联结构导通后,因为两种器件导通特性存在一定的差异,Si IGBT 和SiC MOSFET 按照一定的分配关系导通不同的电流,因此Si IGBT 和SiC MOSFET 的导通损耗也不相同。Si IGBT、SiC MOSFET 导通损耗分别表示为

式中:iIGBT为Si IGBT 的导通电流;VCE为Si IGBT 的导通压降;VCE0为Si IGBT 的阈值电压;K 为比例系数;iMOS为SiC MOSFET 的导通电流;Rds_on_MOS为SiC MOSFET 的导通电阻;iDS为混并联结构在关断延时时间段通过SiC MOSFET 的正向电流。因此,混并联结构的总损耗可以表示为

式中:D 为占空比;fsw为开关频率。

2.3 仿真分析

从损耗模型可以看出,混并联结构内部的功率损耗分配与Toff_delay有关。通过调节Toff_delay,混并联结构内部损耗分配随之改变,如图4 所示,图中,Ploss_IGBT_c和Ploss_MOS_c分别是基于损耗模型计算的Si IGBT 和SiC MOSFET 的功率损耗。

图4 损耗模型计算功率损耗Fig.4 Calculated power loss based on the power loss model

当混并联结构的栅极关断延时较小时,Si IGBT 的计算功率损耗较大,这是由于Si IGBT 的拖尾电流造成了大量损耗;当混并联结构的栅极关断延迟时间较大时,SiC MOSFET 的计算功率损耗高于Si IGBT,这是由于SiC MOSFET 在栅极关断延迟时间内存在较大的额外单独导通损耗。Si IGBT 的计算功率损耗随栅极关断延迟时间呈指数递减,而SiC MOSFET 的功率损耗随栅极关断延迟时间呈线性递增。因此,通过调节Toff_delay,能够有效实现混并联结构内部的损耗分配。

3 混并联结构主动温度控制

混合器件在特殊的门极驱动时序下能够实现IGBT 的ZVS 关断,从而减小IGBT 的关断损耗,然而,由于在图2 所示的驱动时序下,SiC MOSFET 不但需要承担大电流下的硬关断损耗,还需要在延时Toff_delay下短时间内导通器件全部电流,这有可能使SiC MOSFET 在大电流下承担过多损耗从而使芯片面积小而热阻大的SiC MOSFET 过热。在稳态下,器件结温、壳温和器件损耗的关系为

式中:Tj为器件结温;Tc为器件壳温;Ploss为器件的平均损耗;Rθjc为热阻。显然,器件结温与器件损耗、热阻以及壳温相关,在器件损耗增大的情况下器件结温增加。因此在混并联结构中,当辅助器件SiC MOSFET 损耗增加时,由于其芯片面积小、热阻大,可能导致SiC MOSFET 结温过高并影响到混并联结构的可靠性。为此,有必要对Si IGBT/SiC MOSFET混并联结构进行温度控制,即Si IGBT 和SiC MOSFET 二者温度平衡,以提高混并联结构的可靠性。

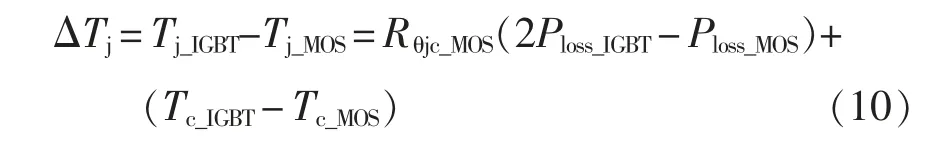

分析混并联器件损耗可知,调节Toff_delay可以控制混并联结构的损耗分配,实现混并联结构的温度平衡,达到减小混并联结构的结温波动、提高混并联结构可靠性的目的。基于混并联结构的损耗模型,本文提出一种适用于Si/SiC 混并联结构的主动温度控制方法。混并联结构中,Si IGBT 与SiC MOSFET 结温差值ΔTj定义为

式中:Tj_IGBT为Si IGBT 结温;Tj_MOS为SiC MOSFET结 温;Rθjc_IGBT为Si IGBT结到壳的热阻;Rθjc_MOS为SiC MOSFET结到壳的热阻;Tc_IGBT为Si IGBT 壳温;Tc_MOS为SiC MOSFET 壳温。设混并联结构中Si IGBT 和SiC MOSFET 二者壳温相等,那么ΔTj可表示为

为实现混并联结构内部两器件的壳温平衡,设计如图5 所示主动温度控制框图,其中反馈控制器采用PI 控制器,相应算法在DSP TMS320F28335数字控制器上实现。将检测到的Toff_delay、iDS、Tc_IGBT和Tc_MOS送入混并联结构损耗模型,得到Si IGBT 与SiC MOSFET 温度差值ΔTc和混并联结构的损耗Ploss;将ΔTc与其参考值ΔTc_ref对比得到误差Tc_error;再与Ploss一并送入控制器,并输出新的Toff_delay,对混并联结构损耗进行重新分配。保证混并联结构中Si IGBT 和SiC MOSFET 温度差值稳定在目标值,提高混并联结构可靠性。

图5 主动温度控制框图Fig.5 Block diagram of active temperature control

4 实验验证

本文采用1 200 V/25 A Si IGBT(型号为IGW25N 120H3)作为主器件、1 200 V/12.5 A SiC MOSFET(型号为C2M0160120 作为辅助器件组成Si IGBT/SiC MOSFET 混并联结构,在DC-DC Buck 电路中进行实验验证。用以实验测试的DC-DC Buck 电路如图6 所示,开关频率为20 kHz,输入和输出电压分别为600 V 和300 V。

图6 混并联结构Buck 电路Fig.6 Buck circuit based on hybrid pair

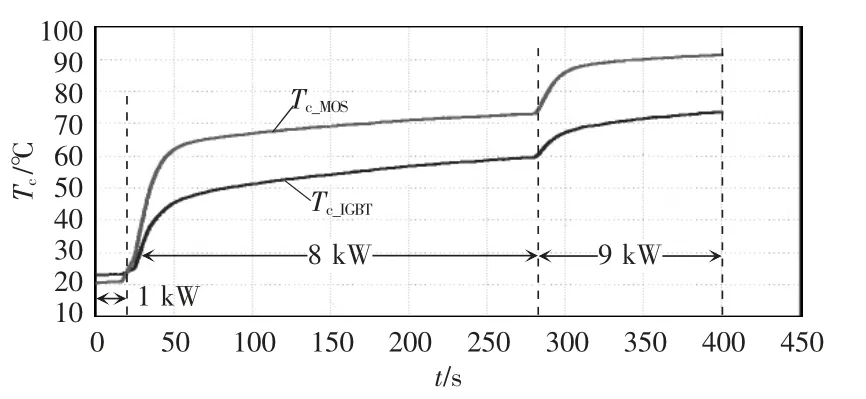

关断延时时间设置为固定值Toff_delay=2.2 μs。主动温度控制前实验结果如图7 所示。从实验结果可以看出,当功率等级提升时,混并联结构中Si IGBT和SiC MOSFET 壳温上升趋势相同;在9 kW 时,SiC MOSFET 壳温达到90 ℃,Si IGBT 壳温在73 ℃左右,二者壳温相差约17 ℃,估测结温差值接近40 ℃。在重载情况下,结温相差过大,极易使混并联结构达到其极限结温,加速器件老化,严重降低了混并联结构的稳定性与可靠性。

图7 主动温度控制前的实验结果Fig.7 Experimental results without active temperature control

在同样的测试条件下,增加主动温度控制,使关断延时时间Toff_delay动态变化,从而改变混并联结构中两个器件的损耗分配,实验结果如图8 所示。

由图8 可见,通过主动温度控制,在负载变化时,两器件壳温始终相近;在9 kW 时,两器件的最高壳温比关断延时为固定值Toff_delay=2.2 μs 时的低10℃;采用主动温度控制后,两器件结温差值约为6 ℃(±3 ℃),比采用固定延时的降低了约34 ℃(±3 ℃),极大地减小了混并联结构由于内部两器件结温差异大带来的器件过温风险,提升了器件运行可靠性。

图8 主动温度控制后的实验结果Fig.8 Experimental results with active temperature control

5 结语

本文提出基于损耗模型的混并联结构主动温度控制,旨在解决混并联结构内部两器件运行中结偏差过大,容易造成内部器件大负载电流下过温风险,提高混并联结构的可靠性。该方法只改变混并联结构中Si IGBT 和SiC MOSFET 之间的关断延时时间,使得两种器件之间的损耗分配动态变化,从而实现Si IGBT 和SiC MOSFET 温度的主动控制。实验结果表明,采用主动温度控制后,两器件结温差值降低了34 ℃左右,极大地减小了混并联结构由于内部两器件结温差异大带来的器件过温风险,提升了器件运行可靠性。