漏压对P-GaN HEMT导通电阻和阈值电压的影响

2021-06-01叶星宁

刘 熙,叶星宁

(电子科技大学 电子科学与工程学院,四川 成都 610000)

在过去的十几年里,GaN器件已经成为半导体技术领域的研究热点之一,具有很高的研究和应用价值[1]。与传统硅器件相比,GaN器件具有高击穿电压、低导通电阻(Ron)和快速开关速度的优势,但AlGaN/GaN HEMT(High Electron Mobility Transistor)会不可避免地受到电子陷阱的困扰[2-3]。陷阱引起的载流子俘获和去俘获过程会导致动态导通电阻[3]和阈值电压(VTH)变化[4],从而导致额外的传导或开关损耗,甚至引起故障。因此,陷阱引起的稳定性问题对于P-GaN HEMT尤为重要。过去的研究内容[5-7]表明P-GaN HEMT阈值电压VTH和导通电阻Ron存在不稳定现象,但是关态下漏压大小和施压时间对阈值电压和导通电阻的影响鲜有文献报道。

本文选取两种常用的GaN商用器件,首先对其结构和原理进行分析和介绍,然后给出阈值电压VTH和导通电阻Ron的测试方法,对两种器件的阈值电压VTH和导通电阻Ron进行测试和分析。结果表明,无P-GaN漏极结构的器件只有导通电阻受漏极电压和加压时间影响较大;有P-GaN漏极结构器件的阈值电压受漏极电压和加压时间影响较大。

1 测试器件

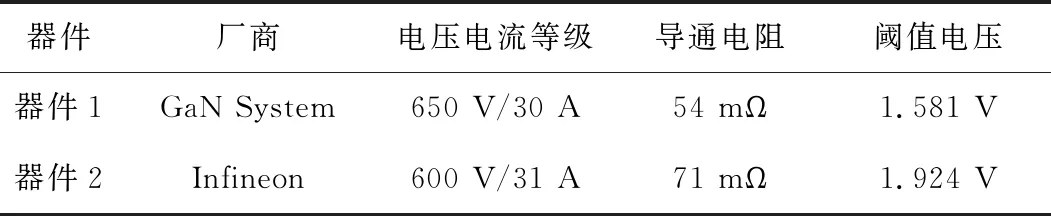

由于异质结特性,常规的Al-GaN/GaN HEMT为耗尽型器件,负压关断使得栅极驱动变得复杂,损耗也更大。GaN基场效应管的阈值电压调控一直是GaN领域的研究重点。以往实现器件增强型更多的是使用Cascode级联技术[8],也就是将耗尽型的GaN HEMT器件与增强型的Si器件级联。目前,增强型GaN器件凭借结构简单、封装体积小、寄生电感小等优势,正逐步取代Cascode型器件。本文选择了两种来自不同厂商的、常用的、较新推出的、不同结构的E-mode GaN器件作为被测器件[9-10]。其室温下关键参数如表1所示。

表1 测试器件参数

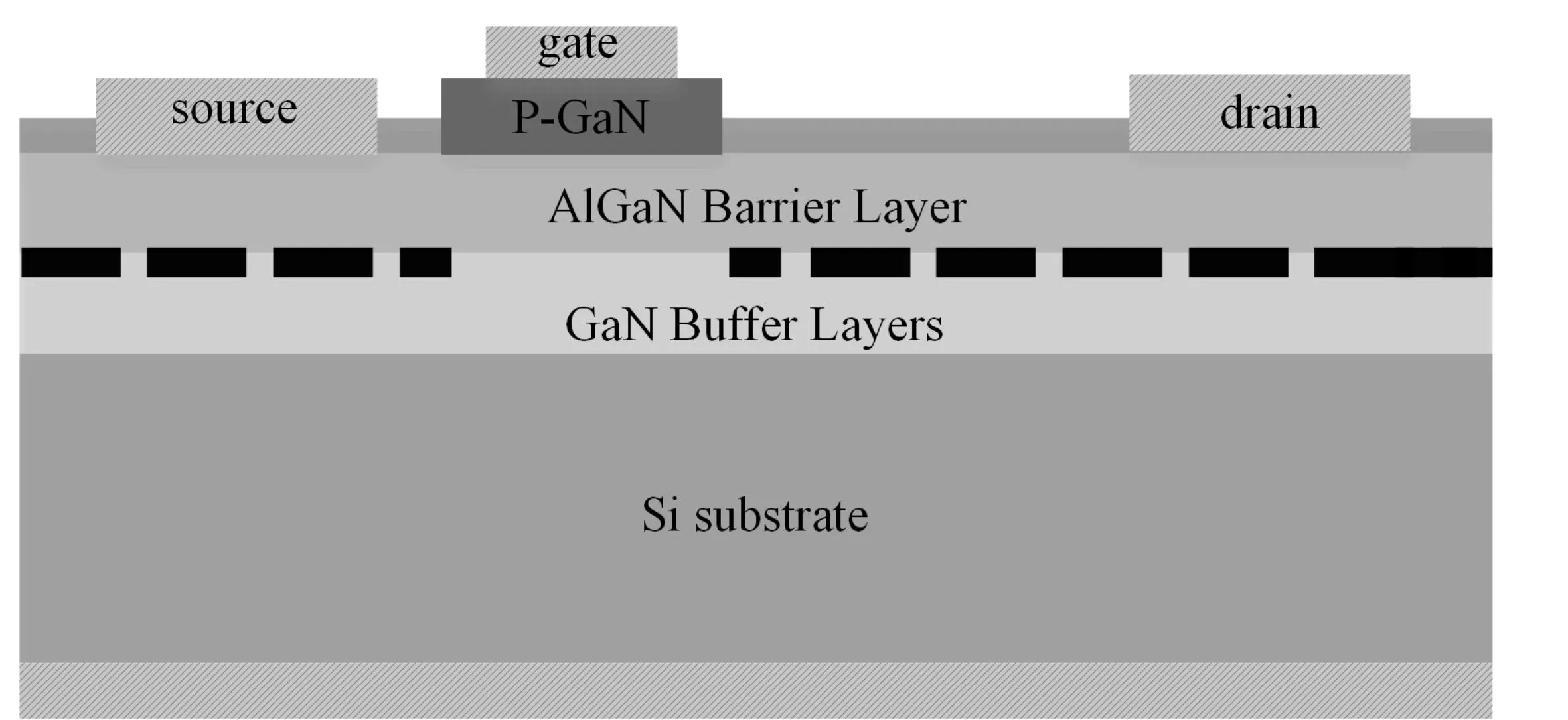

器件1和器件2的结构如图1所示。这两款器件均为使用P-(Al)GaN Gate技术实现的增强型器件。测试器件在栅下区域的 AlGaN层表面和栅极金属之间插入一层P-(Al)GaN层,插入的P-(Al)GaN层与其下方的AlGaN势垒层形成PN结,内建电场方向由势垒层指向P-GaN层,抬高栅极下方的AlGaN势垒层和GaN缓冲层能带,耗尽该区域的二维电子气,从而形成增强型器件[11-12]。

(a)

(b)图1 两款器件结构图(a)器件1结构图 (b)器件2结构图Figure 1. Structure of two devices(a)Structure diagram of device 1 (b) Structure diagram of device 2

器件1和器件2的区别在于器件1采用传统漏极结构而器件2漏极采用了P-GaN漏极结构[13]。由于从栅极隧穿的电子被AlGaN势垒层表面缺陷俘获或者施加高VDS时沟道电子加速被表面缺陷俘获导致电流崩塌,漏极结构在施加较高漏压时,可向器件注入空穴释放被陷阱束缚的电子从而减小表面缺陷。

GaN器件中存在大量陷阱,陷阱中心的能级位于禁带内,通过发射和俘获电子与导带和价带交换电荷。陷阱分为施主陷阱和受主陷阱:施主陷阱既可以呈阳性也可以呈中性。其在空状态时呈阳性,可以俘获电子或发射空穴,被电子填充后呈中性,可以发射电子或俘获空穴;受主陷阱既可以呈阴性也可以呈中性。其在空状态时呈电中性,可以俘获电子或发射空穴,在被电子填充后呈阴性,可以发射电子或俘获空穴[14]。电子和空穴的俘获过程会对器件的导通电阻和阈值电压产生影响。

导通电阻和阈值电压是器件的两大重要指标。导通电阻变化可能导致器件功耗增大从而增大电路损耗,阈值电压变化则可能导致器件容易击穿,损坏器件进而影响电路使用。因此为了研究P-GaN器件的可靠性,下面将对两种P-GaN商用器件在不同偏置条件下的导通电阻和阈值电压进行测试分析。

2 测试原理

高场应力下, 器件特性会随高场应力偏置电压的增加和偏置时间的累积变化[15]。本次测试通过改变高场应力偏置电压和偏置时间,对P-GaN商用器件的导通电阻及阈值电压进行测试和分析。

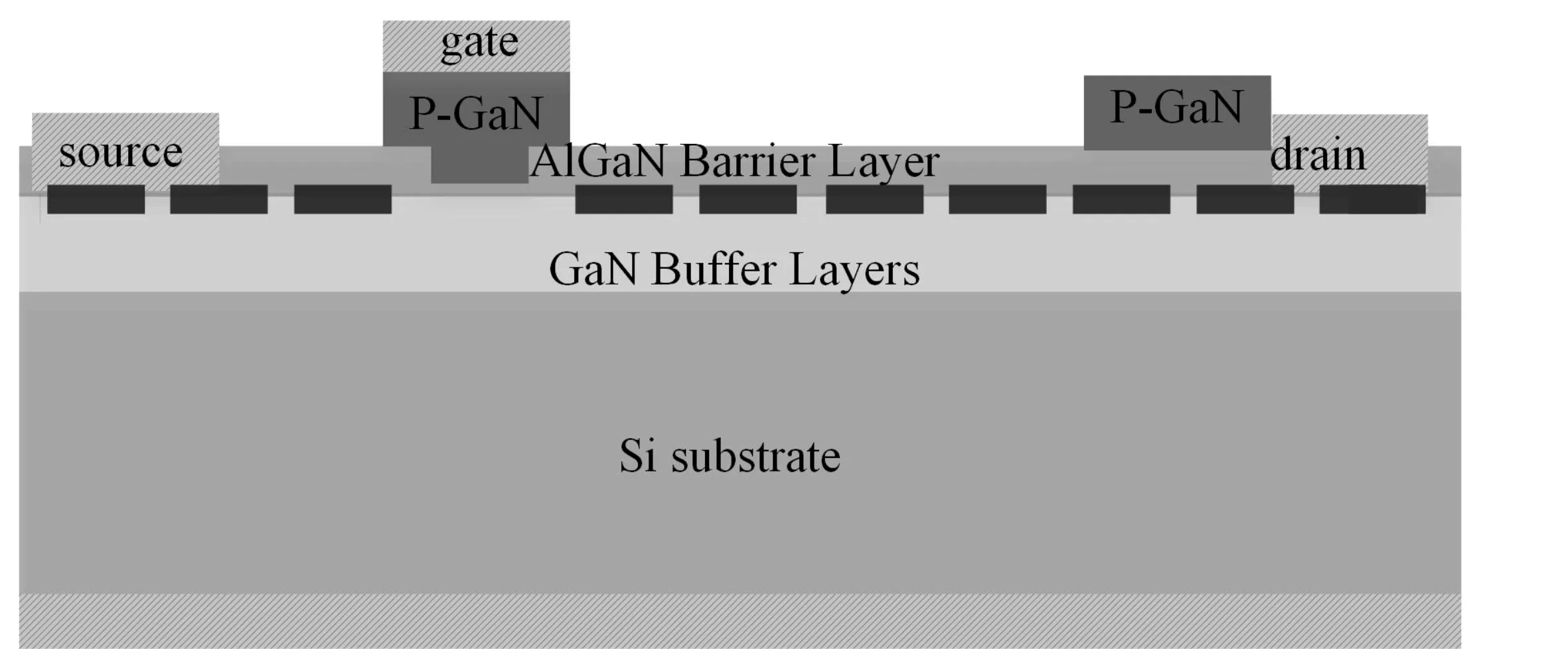

图2 测试过程波形示意图Figure 2. Waveform diagram of test process

本文测试使用DTS1000进行测试,测试过程如图2所示。为了测试器件漏极电压和偏置时间对导通电阻和阈值电压的影响,选择漏极电压的变化范围从10~600 V,步长10 V,施压时间从1~9 s,步长1 s,每组测试选择一个电压值和施压时间进行测试。每组测试过程都包括以下阶段:第一阶段,测试器件处于关态,在测试器件漏端施加电压VDS;第二阶段,器件处于导通状态,此阶段进行导通电阻Ron测试,测试时间为5 μs,此阶段对器件施加一个固定的导通电流IDS1和栅极电压VGS。VGS和IDS1数值来自器件的数据手册;测试电路如图3(a)所示;Ron由测得的电压VDS除电流IDS1所得;第三阶段,进行阈值电压VTH测试,测试时间为2.5 ms。此阶段对器件施加固定的导通电流IDS2,测试电路如图3(b)所示,栅端和漏端进行短接。具体测试参数VGS、IDS1、IDS2如表2所示。

表2 测试具体参数

3 测试结果分析

3.1 器件1测试结果分析

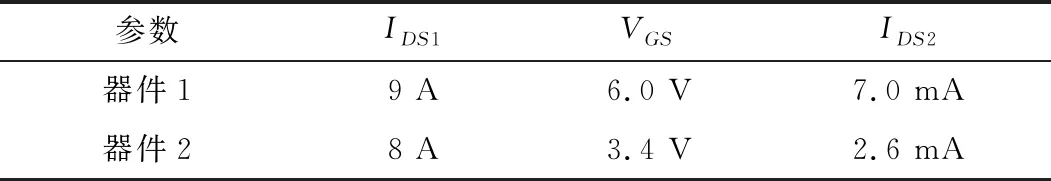

3.1.1Ron测试结果分析

按照上述测试方法对器件1进行测试,观察导通电阻和阈值电压的变化,导通电阻测试结果如图4所示。由图4可以看出,相比于室温下器件1的导通电阻值54 mΩ,在不同漏压下,器件1的导通电阻增长幅值从4~13 mΩ变化。对于一定的加压时间,随着电压增大,器件的导通电阻呈现先增大后减小的变化趋势,并且在300 V附近出现峰值。当VDS<300 V时,器件尚未开启,工作在高压阻断状态,器件中的电子在栅漏之间的强场中获得能量从而被激发,接着被AlGaN势垒层表面的陷阱所俘获。被俘获的电子会在栅漏极之间的区域内形成负电荷积累,部分耗尽了这一部分下方的二维电子气,导通电阻增加[16]。当VDS>300 V时,电压足够大,器件中的施主陷阱和受主陷阱都被填满,开始进行空穴的俘获过程,沟道中二维电子气的浓度增加,导通电阻减小。随着加压时间的增加,电阻逐渐增大。这是因为当加压时间增加时,陷阱俘获更多电子,沟道中二维电子气浓度降低,导通电阻增大。300 V之后随时间的变化减小,因为俘获空穴的过程较慢。

图4 器件1的Ron测试结果Figure 4. Ron test results of device 1

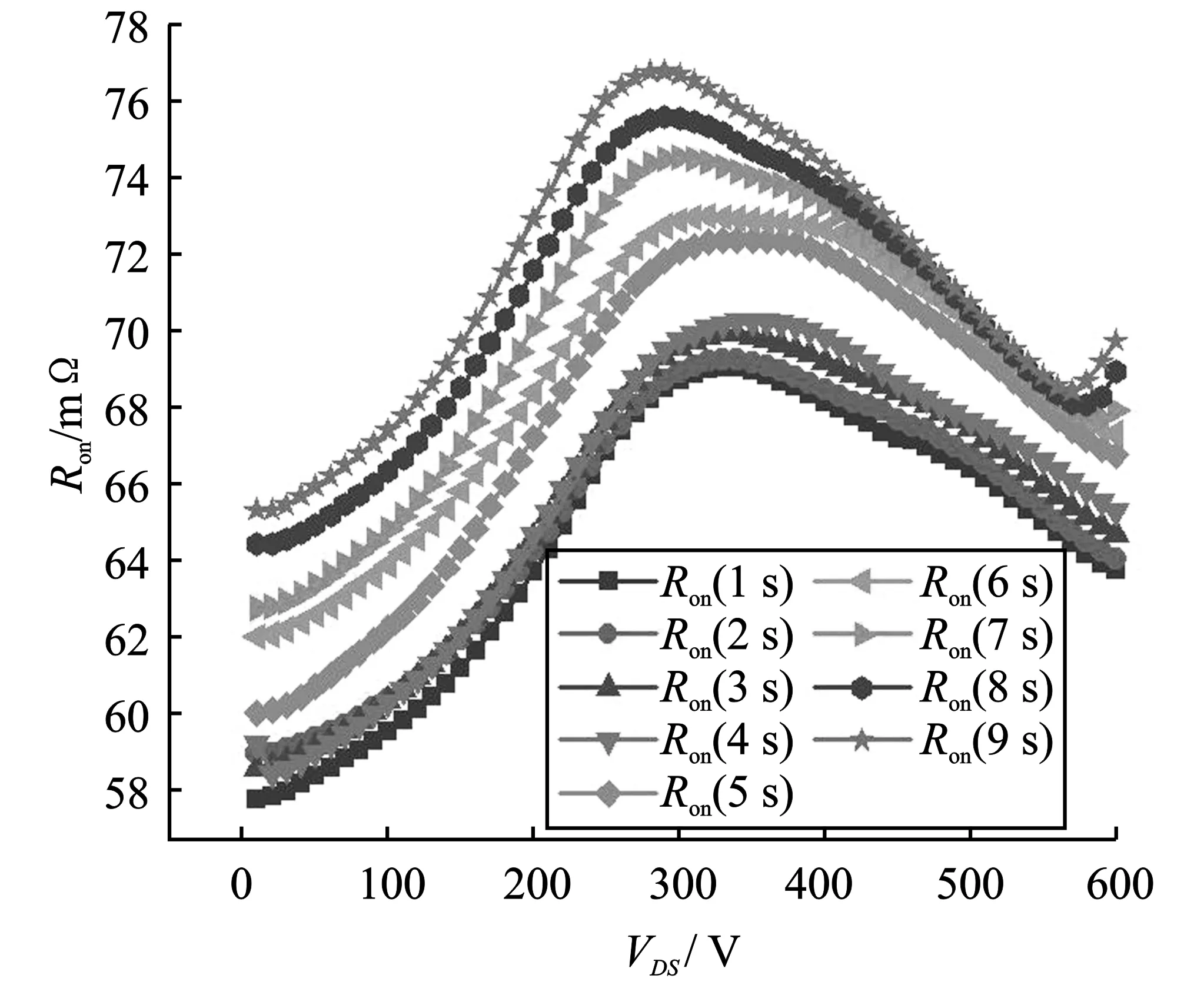

3.1.2VTH测试结果分析

器件1的阈值电压测试结果如图5所示。由图5可以看出,与室温下不加压的阈值电压相比,器件1的阈值电压稍有增加,但器件的阈值电压随漏极电压大小变化和加压时间增加无明显变化。该结果表明增高电压和增大加压时间对栅极的影响很小,变化发生在AlGaN势垒层表面,栅极下方只有少量电荷积累。

图5 器件1的VTH测试结果Figure 5. VTH test results of device 1

3.2 器件2测试结果分析

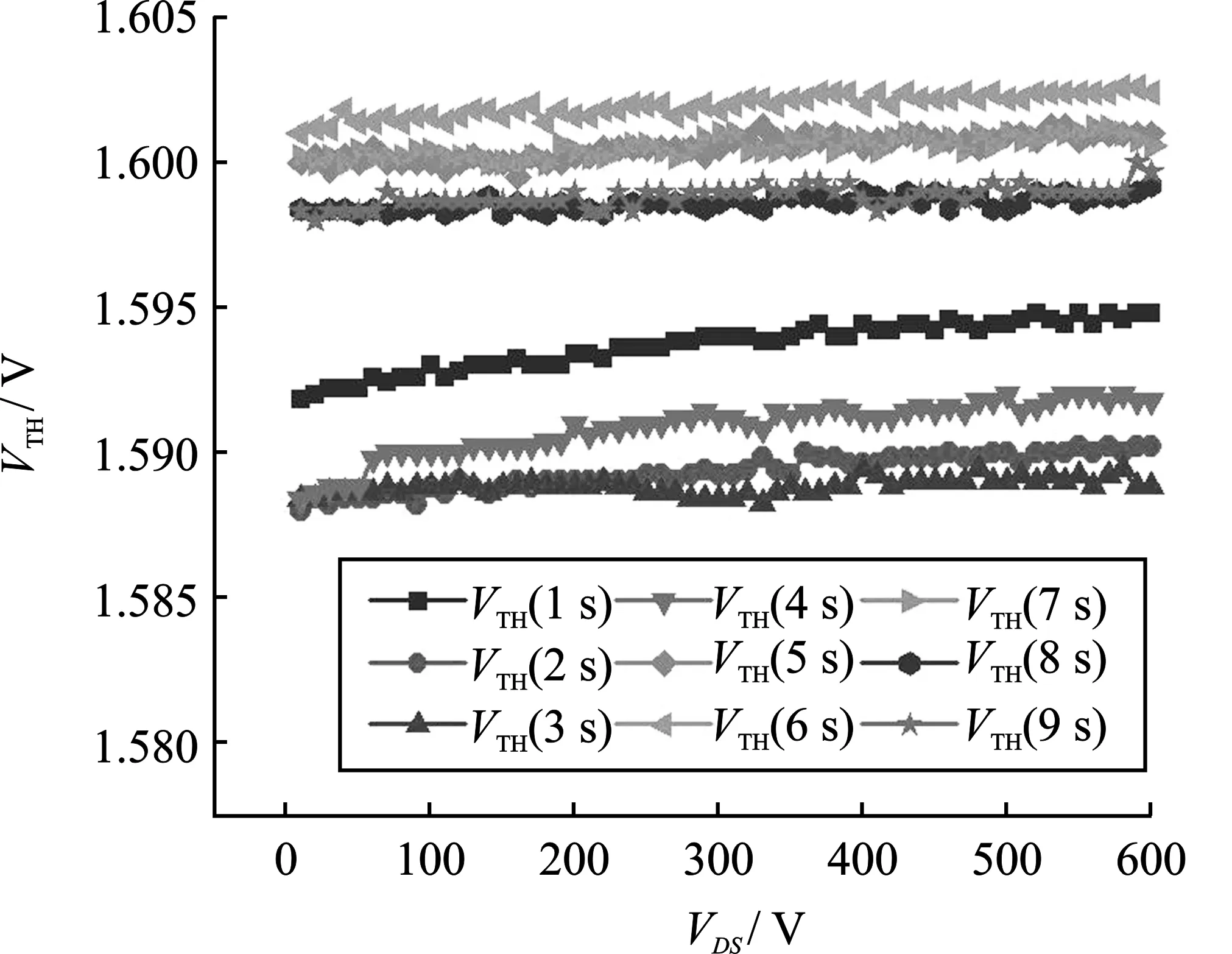

3.2.1Ron测试结果分析

器件2的导通电阻测试结果如图6所示,器件2导通电阻的变化幅值不超过2 mΩ,与器件1相比变化幅值小。随着电压增大,器件2的导通电阻呈现先减小后增大的趋势,谷底出现在150 V。器件2采用P-GaN漏极结构,减小了表面陷阱,当VDS<70 V时,器件尚未开启,工作在高压阻断状态,P-GaN漏极结构填满了器件中的施主陷阱和受主陷阱。漏压增加时,器件进行空穴的俘获过程,导通电阻降低。当70 V

图6 器件2的Ron测试结果Figure 6. Ron test results of device 2

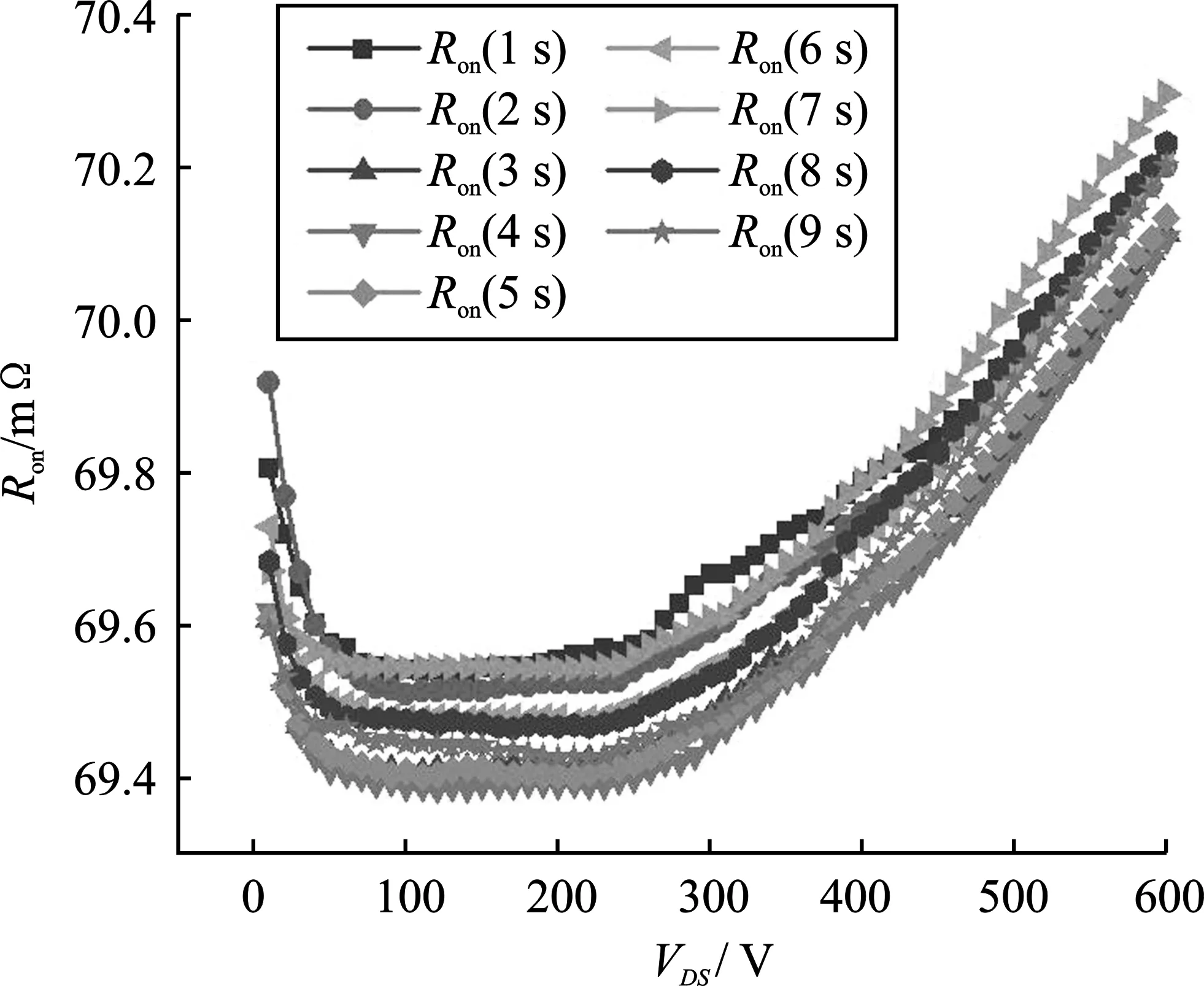

3.2.2VTH测试结果分析

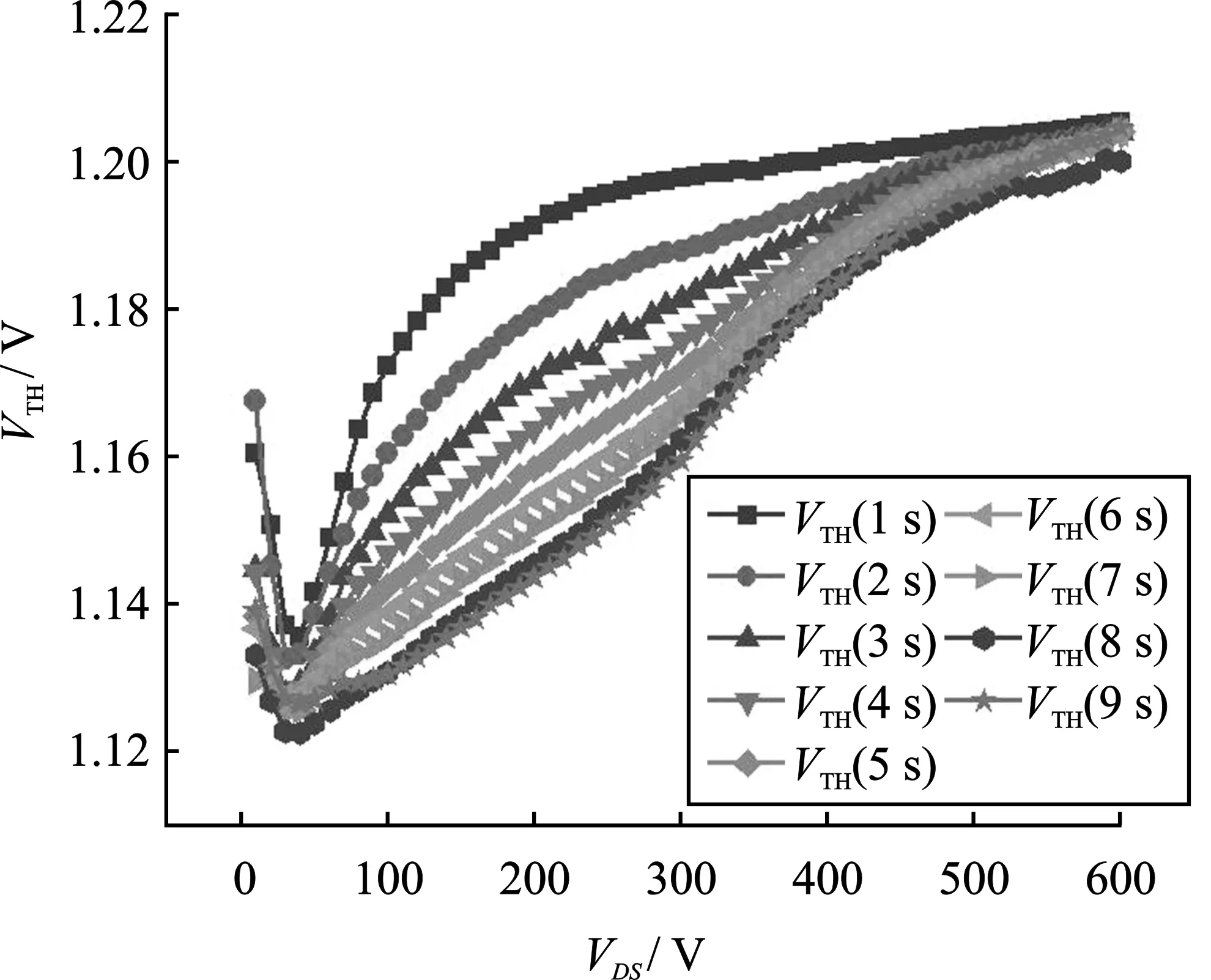

图7 器件2的VTH测试结果Figure 7. VTH test results of device 2

器件2的阈值电压测试结果如图7所示,由图7可以看出,随着电压增加,器件2的阈值电压变化幅度约为0.08 V,室温下器件2的阈值电压为1.924 V,漏压的施加使器件的阈值电压减小,对于一定的加压时间,随着电压增大,器件的阈值电压呈现先减小后增加的变化趋势。当VDS<50 V时,器件尚未开启,工作在高压阻断状态,器件此时进行空穴的俘获工作,栅极也进行空穴的俘获,阈值电压减小。当VDS>50 V时,高的漏极电压引起了更深能级的缺陷,电子被深能级的缺陷俘获,阈值电压VTH增加。漏极加压时间越短,陷阱俘获的空穴越少,阈值电压越大。

3.3 其他测试

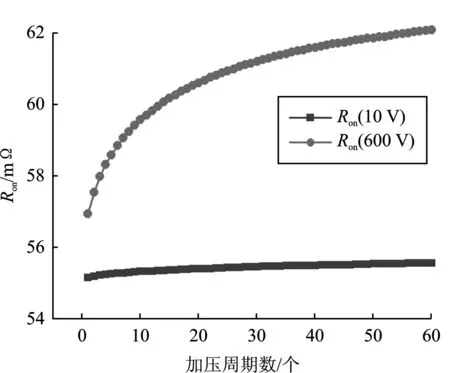

随着测试反复循环,器件承受电压的时间也在增加,为了排除测试周期数增加的影响,对于同一电压下导通电阻随着加压时间的变化进行分析,对器件1额外进行了两组对比测试,一组VDS加固定电压10 V,另一组VDS加固定电压600 V,测试导通电阻随着测试周期数变化,测试结果如图8所示。

图8 固定漏极电压下器件1的Ron测试结果Figure 8. Ron test results of device 1 at a fixed drain voltage

由图中可以看出,漏压不变时,随着测试过程的进行,导通电阻增大,与电压变化时导通电阻先增大后减小的趋势不一致。固定电压为600 V时,导通电阻增加了5 mΩ;固定电压为10 V时,导通电阻增加0.4 mΩ。变化过程中时间的影响最多为5 mΩ,在测试中主要影响结果的还是加压时间和漏压。因此测试过程首尾不一致可能是由测试测试周期数增加导致的。

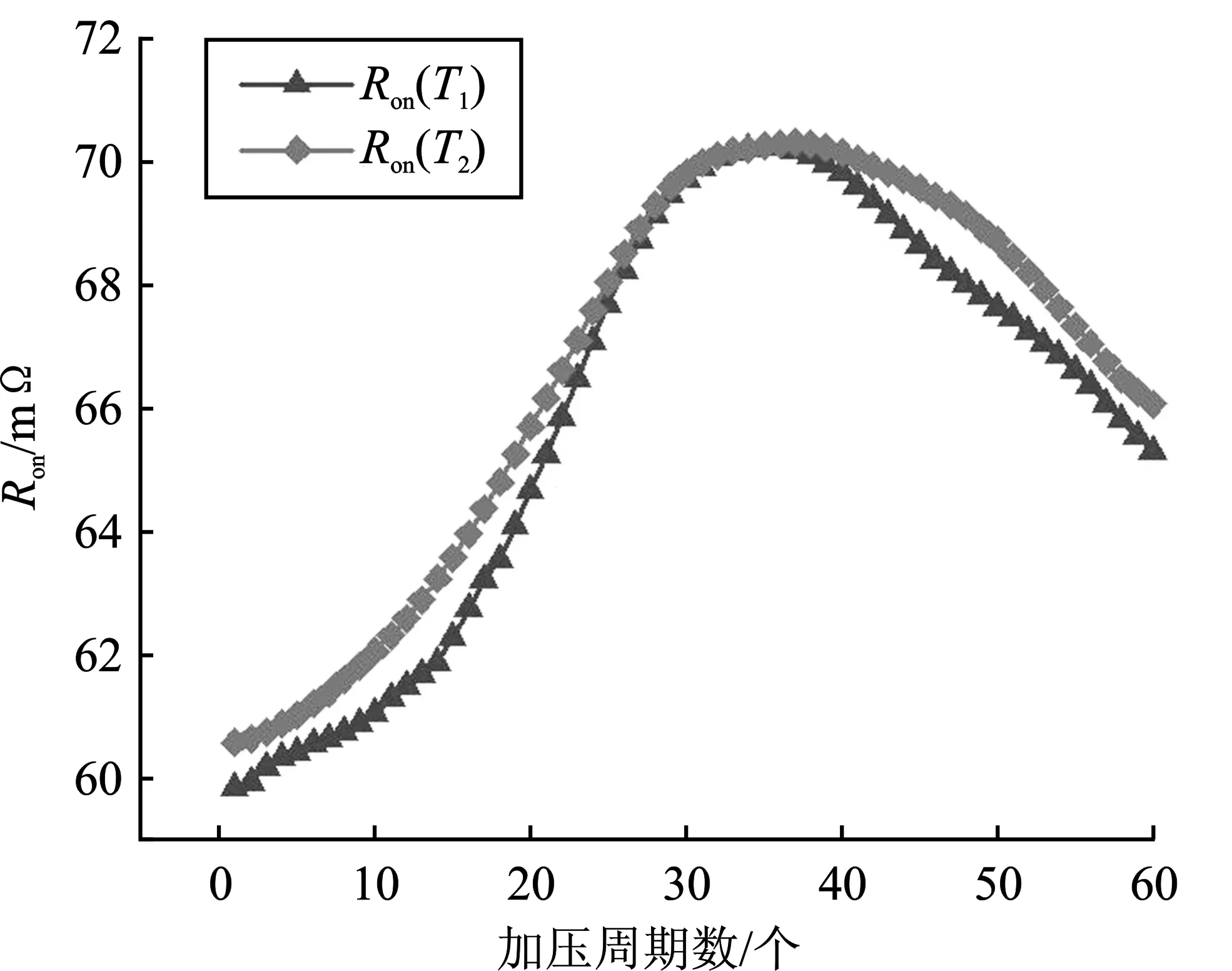

在本实验中,除了漏压,器件开关过程中产生的热电子也可能是影响导通电阻的原因之一。为了排除热电子的影响,进行如下测试:器件1每次测试结束后静置10 s。10 s后热电子造成的影响基本恢复,结果如图9中的曲线Ron(T2)。曲线与未静置时的器件1导通电阻曲线Ron(T1)变化趋势相似,热电子效应在本实验中造成的影响可忽略,造成器件导通变化的主要原因是漏极电压。

图9 不同静置条件下器件1导通电阻Ron测试结果Figure 9. Ron test results of device 1 under different static conditions

4 结束语

在实际应用中,器件处于关闭状态(栅极尚未开启)时,高漏极偏压是导致器件退化的主要原因之一。本文通过关态下漏压偏压应力时间和电压值进行改变,分析漏极偏压对器件的影响。测试结果表明,对于无P-GaN漏极结构的器件来说,高漏压使器件导通电阻变大,性能退化。在漏压300 V左右,器件导通电阻退化最为严重,且随着加压时间增加,器件的导通电阻一直增大,长时间工作使得器件可靠性下降。对于有P-GaN漏极结构来说,高漏压使器件阈值电压降低,且随着漏压增加阈值电压增大逐渐逼近室温下的阈值电压。在漏压50 V左右,器件的阈值电压退化最为严重。因此,应该根据应用条件选择合适器件,并且尽量使器件在合适的电压条件下工作。