基于System Generator的干扰模块设计

2021-04-15任丽莉陈伟衡刘广君

任丽莉,陈伟衡,刘广君,2

(1.中国空空导弹研究院,河南 洛阳 471009;2.航空制导武器航空科技重点实验室,河南 洛阳 471009)

0 引 言

干扰机是电子战组成中的重要一环[1]。随着新体制雷达的不断出现,干扰算法和策略相应革新[2]。如何快速实现干扰算法和产生干扰信号成为了干扰机设计过程中重要的工程问题[3-4]。当前现场可编程门阵列(FPGA)设计方式多采用ISE和Isim等基于硬件描述语言的电路设计和验证软件,对干扰算法进行实现和测试,Xillinx公司发布的系统级建模工具System Generator扩展了Simulink平台的功能[5-8]。在可视化设计环境下,该工具加速简化了FPGA的开发流程,无需使用硬件描述语言即可在其开发环境内实现软/硬仿真、执行和验证,当前国内众多领域已经采用System Generator作为主要开发工具[9-12]。

借鉴System Generator的开发思想,提出了基于System Generator的干扰模块设计方法,使得干扰样式的产生电路具有易复用、易生成和易修改的优势,能够用于实现数字干扰合成(DJS)、欺骗和压制类干扰设计。本文详细阐述了基于System Generator的干扰模块设计思路和方法,并以干扰中具有代表性的射频噪声干扰为例,通过本文方法进行FPGA硬件实现,实验结果证明了本文方法的有效性。

1 基于System Generator的干扰算法开发方法

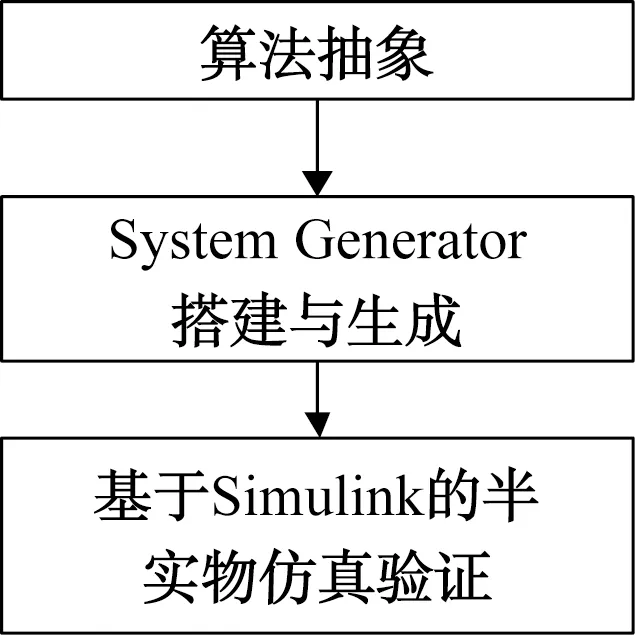

基于System Generator的干扰算法开发流程如图1所示。

图1 基于System Generator的干扰算法开发流程

基于System Generator的干扰算法开发流程为:首先,对干扰公式进行抽象设计,在System Generator自带模块库中找出对应的运算模块进行自顶向下的搭建。然后,通过与Simulink结合,调用Simulink中提供的可视化测试模块对干扰模块设计进行验证。最后,通过半实物仿真的方法,将Simlink产生的数据通过加载到FPGA上进行电路测试,并将数据导出进行分析验证。

该开发方法可以在完全可视化的操作界面下完成算法的设计验证、修改和测试,降低了开发难度,提高了设计和测试速度,直接从Simulink和System Generator现有库中粘贴复制现有工程模块即可在设计中直接使用,提高了算法实现速度和仿真结构搭建速度。

2 射频噪声干扰的System Generator实现

为了进一步说明设计的基于System Generator的设计方法,本节实现射频噪声干扰。射频噪声干扰信号为窄带高斯过程[13]:

J(t)=U(t)cos[ωt+φ(t)]

(1)

式中:U(t)包络函数服从高斯分布;φ(t)服从[0,2π]均匀分布,并且与U(t)相互独立。

载频为常数,且远大于干扰信号的谱宽。

通过对数学原理的分析可知,可以将其自顶向下地切分为3个部分[14]:

第1部分需要产生高斯分布的包络函数。由随机信号理论可知,在(0,1)上服从均匀分布的随机数经过box_muller变换,可以产生服从N(0,1)的白色高斯随机数[10]。其中box_muller变换算法如下:设x和y是2个互相独立并在(0,1)上均匀分布的随机数,做如下变换:

(2)

可以得到2个相互独立的正态N(0,1)随机数m,n。

第2部分由于射频噪声干扰是一个窄带过程,所以载频要远大于带宽。根据数字信号处理理论,包络函数产生的频率就是其带宽,所以通过控制其产生频率,即可控制其带宽。

第3部分,通过频谱搬移的方法将其搬移到指定频域。

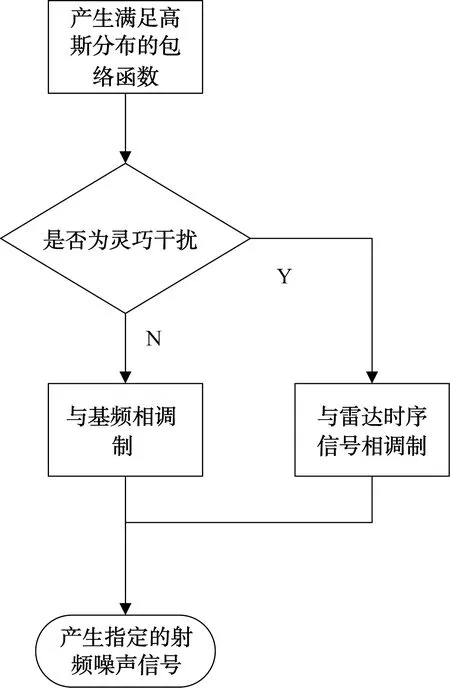

通过上述分析可以得到射频噪声干扰的System Generator实现的流程,如图2所示。

图2 射频噪声产生流程图

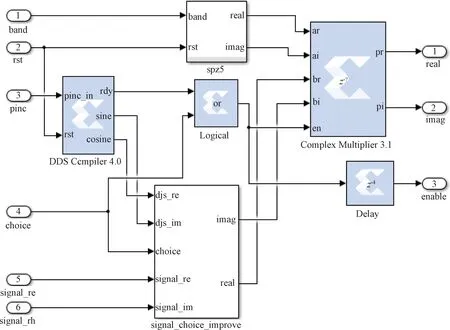

根据上述理论分析以及实践流程可以实现硬件搭建,电路结构如图3所示。

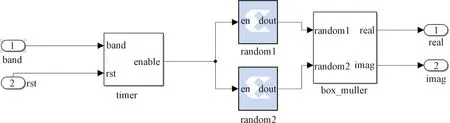

电路设计思路为通过射频噪声产生模块产生2路符合带宽要求、相互独立的正态随机分布序列,然后控制choice管脚、signal_choice_improve模块和Complex_Multipiler 3.1,选择通过DDS Complier 4.0进行频谱搬移,或者将噪声信号直接叠加到雷达信号上,实现灵巧射频噪声(signal_re和signal_im)。其中射频噪声模块的搭建方式如4所示。

首先,根据数字信号处理理论,产生满足高斯分布的包络函数,首先需要产生随机序列,使用Xilinx Linear Feedback Shift Register,为了获得良好的随机性,一共并行输出27位,其中的低10位作为只读存储器(ROM)的片选地址,通过线性反馈移位寄存器(LFSR)产生均匀分布的伪随机数。包络函数产频率就是其带宽,所以通过控制其产生频率,即可控制其带宽。故采用分频器设计,当计数时间达到band,产生enable标志位,从而控制随机数产生的速度。

图3 射频噪声电路实现

图4 射频噪声模块电路实现

然后,运用线性反馈移位寄存器 (LFSR)产生2路满足均匀分布的随机数。

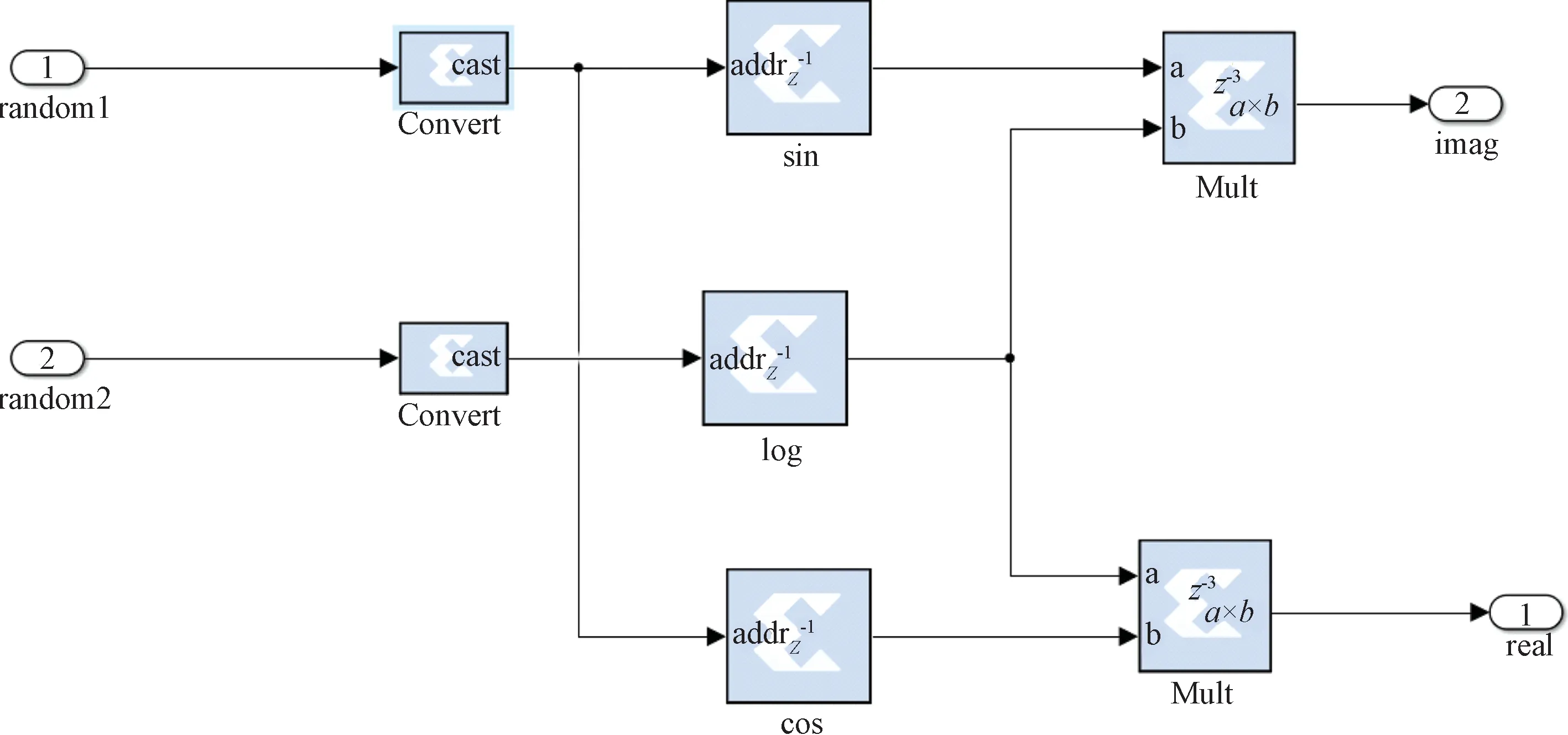

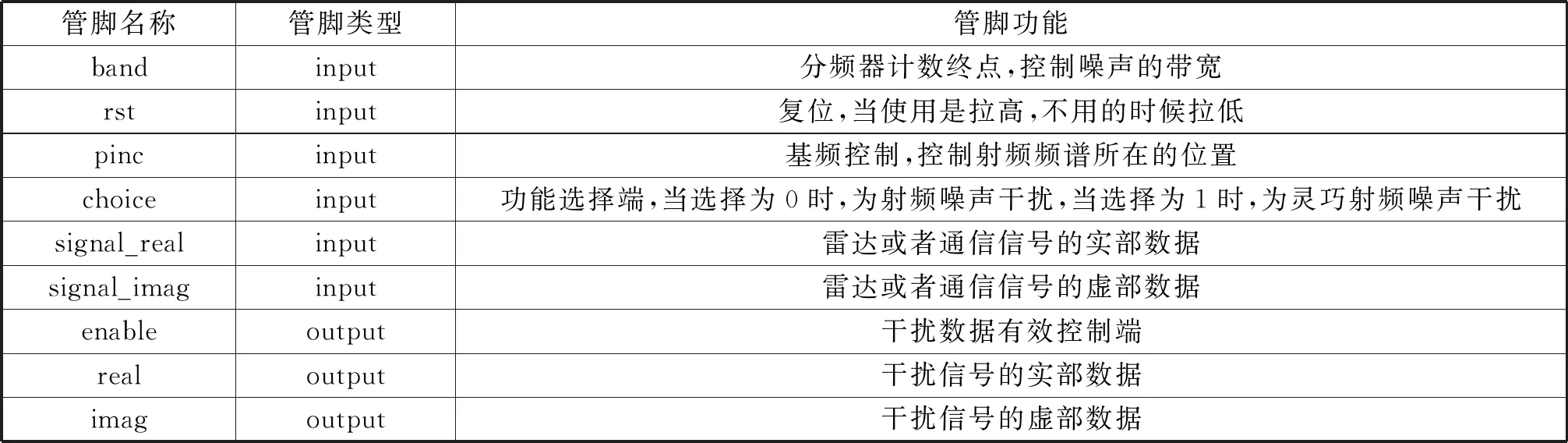

之后,如图5所示实现box_muller算法[15],由于计算十分复杂、结构繁杂并且运算速度低,直接将对数加权表、正弦函数表和余弦函数表均存储在内部ROM中,通过将随机数当成地址的方式直接通过寻址找到得数。通过查表法搭建box_muller算法,降低FPGA运算量。其中sin、log和cos模块都是通过内部随机存储器(RAM)搭建形成,预先将数据存入,然后根据随机数进行寻址,避免了大运算量。算法实现结构如图5所示,关键输入输出端口如表1所示。

图5 box_muller算法的实现

表1 射频噪声干扰模块接口说明

最后,使用直接数字式频率合成器(DDS)和复数乘法器,通过频谱搬移的方式将高斯噪声搬移到指定频率。例如本文采用350 MHz的时钟频率,时钟周期为2.857 142 86 ns。当前DDS使用的相位精度为10 bit数据,频率分辨率为:

(3)

噪声的产生速度等于带宽,故通过分频器控制噪声产生的速度,分频器中的计数器为27位,通过外部管脚控制计数终止位置:

(4)

3 仿真验证

3.1 射频噪声干扰模块验证

通过采用System Generator和Simulink的半实物仿真测试、基于ChipScope的板级测试和基于Matlab的信号特征测试的3种测试方法,共同对生成的射频噪声干扰硬件电路模块进行测试,证明本文提出的设计方法能够有效设计和生成噪声压制。

3.2 基于System Generator和Simulink的半实物仿真测试

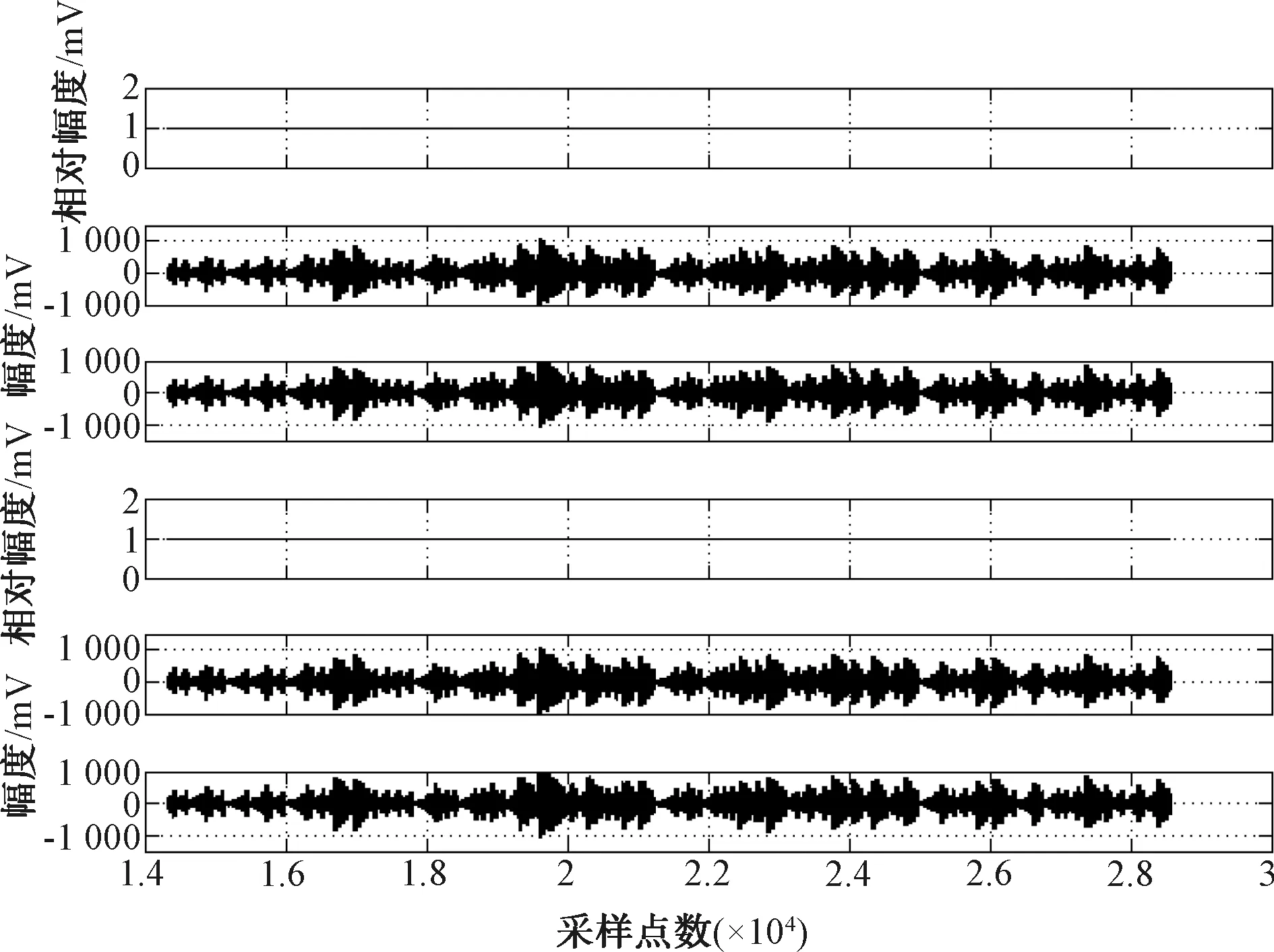

基频为75 MHz,射频噪声带宽为17 MHz,使用时钟为350 MHz。本节主要体现硬件设计中延迟时钟和信号频谱质量,满足设计要求。如图6所示组建基于Simulink的半实物测试平台。将硬件产生数据读出Simulink,对比硬件产生的数据和电路设计仿真结果之间的关系,验证硬件产生的数据与电路设计仿真一致。图7为硬件产生数据和仿真数据之间的对比,表明硬件数据与仿真数据相符,证明硬件电路满足设计要求。图8为硬件产生数据的频谱分析,证明与设置符合,其中主要干扰带宽集中在-8.5 MHz和8.5 MHz之间,满足干扰设计要求。

图6 射频噪声半实物仿真测试结构

图7 仿真数据和FPGA生成数据对比

图8 FPGA生成数据频谱质量

3.3 基于ChipScope的板级测试

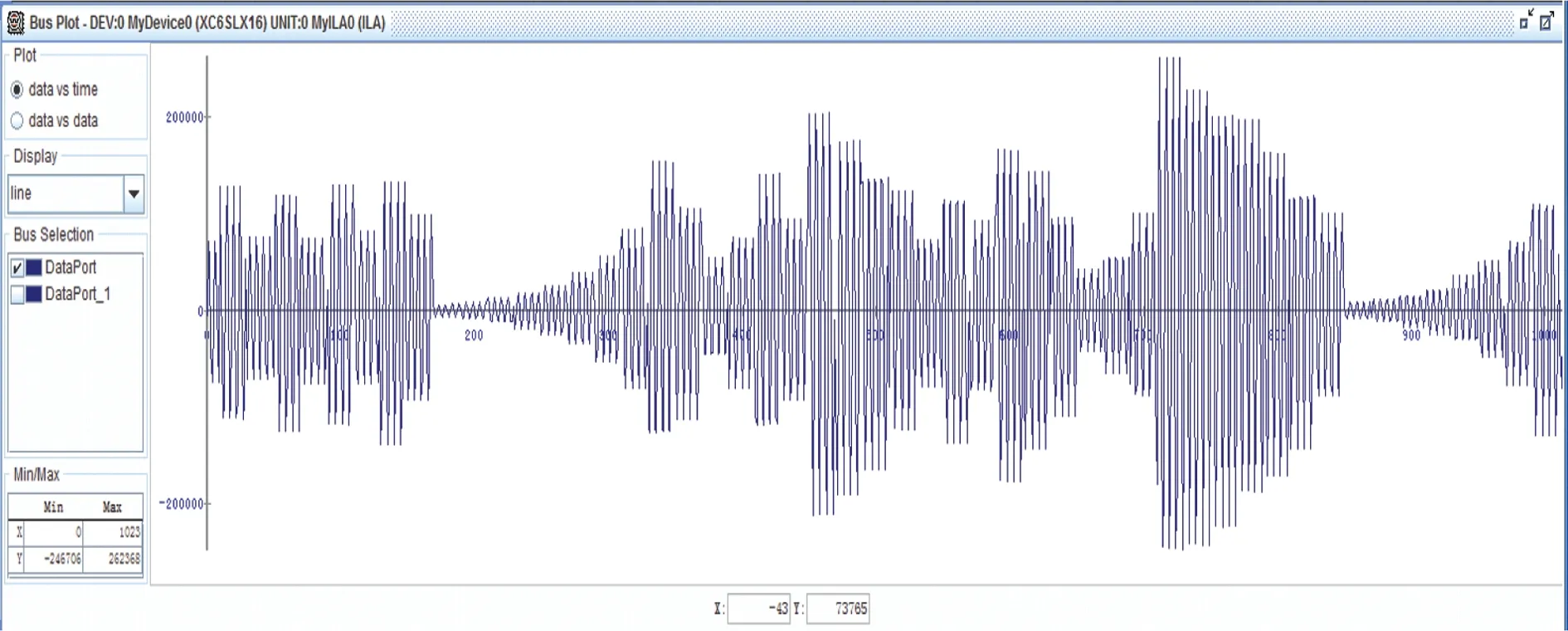

对实际硬件产生数据进行抓取并导出数据,进行基于Matlab的信号特征测试。抓取数据效果图如图9所示。

图9 chipscope抓取干扰数据

3.4 基于Matlab的信号特征测试

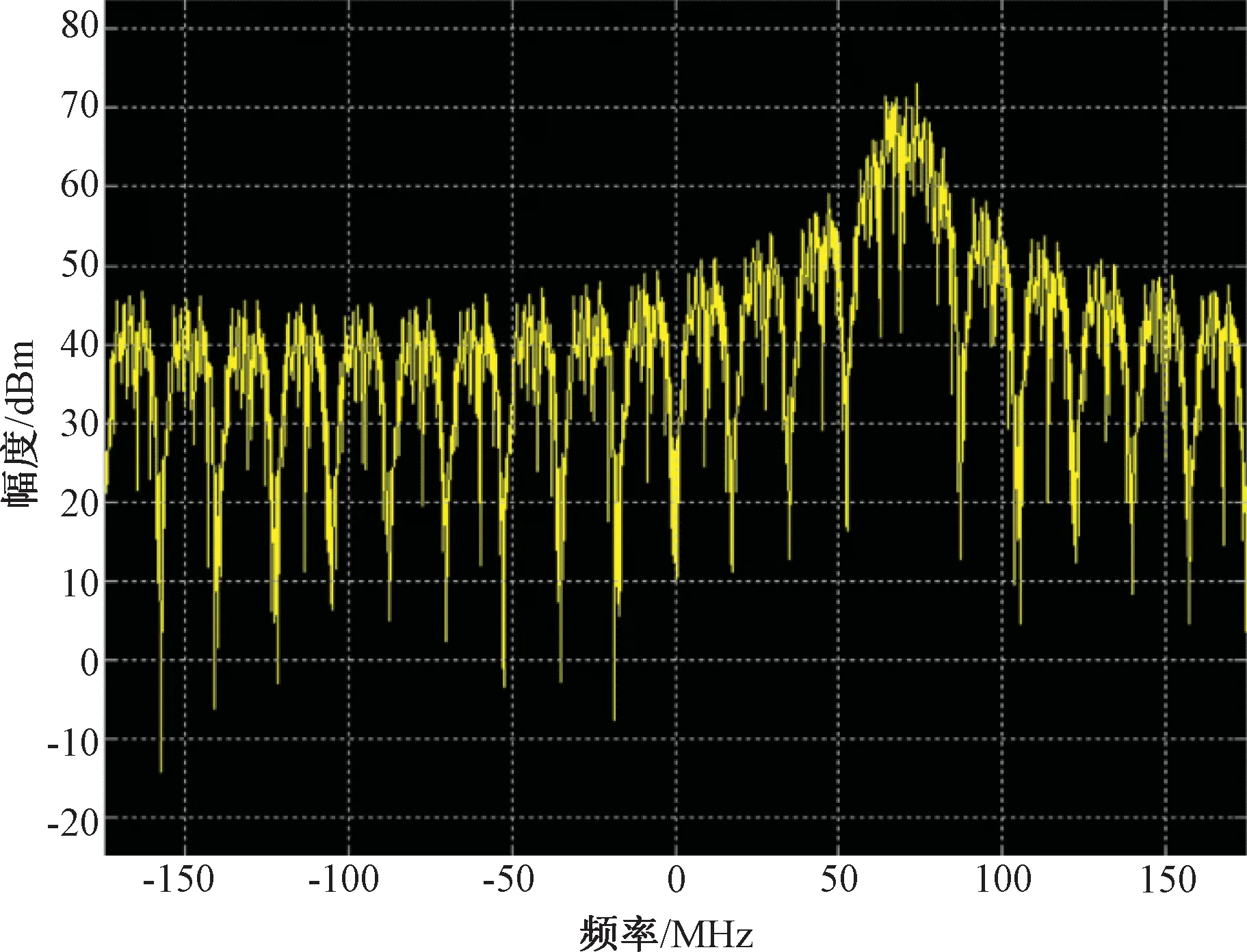

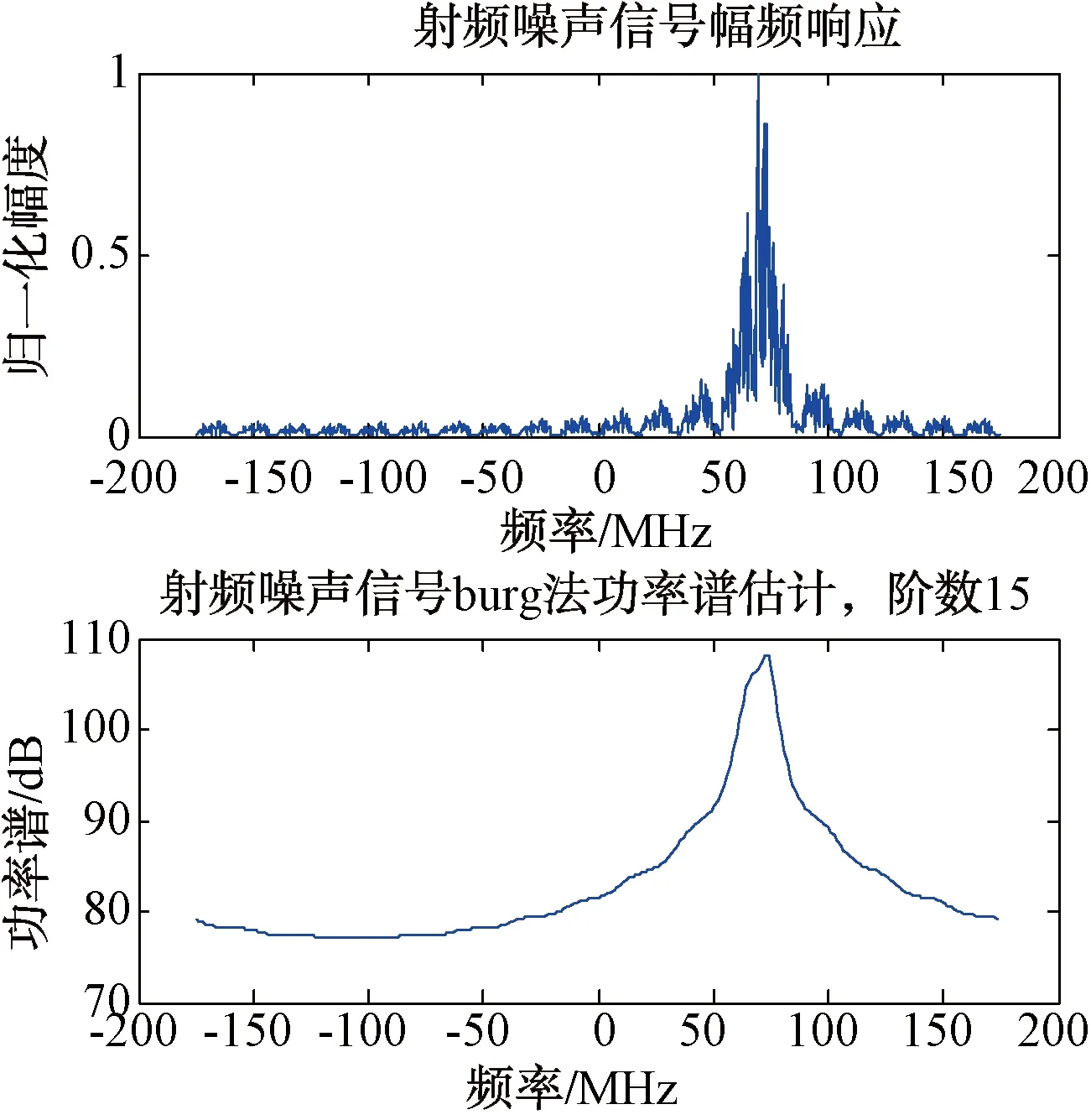

对抓取的数据进行功率谱分析,结果如图10所示。可以看出主要信号能量集中在所设置的17 MHz内,与硬件设置值一致,证明射频噪声干扰电路有效。

图10 抓取到的信号特征分析

4 结 论

本文提出了基于System Generator的干扰模块设计方法。将Simulink和System Generator结合,在FPGA上实现干扰算法。文中详述了System Generator的开发流程,为工程实践提供了理论依据。以具有代表性的射频噪声干扰为例,采用本文提出的设计方法进行了电路实现和半实物仿真验证。电路实现过程和实验结果证明该方法能够快速有效地生成干扰模块,具有易复用、易生成和易修改的优势。