基于FPGA无人机影像快速低功耗高精度三维重建

2021-04-13李杰李一轩吴天生王昊榕梁敏

李杰,李一轩,吴天生,王昊榕,梁敏

(山西财经大学 信息学院,太原030006)

嵌入式计算机视觉系统是光学影像三维重建的重要应用领域之一,通过三维重建可获得相应场景的深度信息,其类似于人眼的基本机制,在诸如机器人 导 航[1]、文 物 保 护[2]、航 空 摄 影[3-4]、太空探索[5-7]等领域都有重要的潜在应用价值。无人机(Unmanned Aerial Vehicle,UAV)作为一种方便的地形观测设备,通常应用于航空摄影。假设D为无人机左右摄像机光心之间的距离,H为机载摄像机相对地面的高度。一般而言,无人机连续拍摄间隔距离D值很小,其飞行高度H值很大,即航拍影像的基高比相对很低。另外,使用无人机进行地形拍摄时,非常容易出现低纹理、动态纹理区域,尤其在多山地地区进行低空对地观测时,图像中常会包含高山、阴影、河流等区域,然而传统基于FPGA的三维重建方法通常不适用于这一情形。

基于光学影像的三维重建系统通常包含大规模视差计算步骤,然而传统计算机因固有的指令周期延迟使得大规模视差计算的运行效率非常低。针对该类问题,研究人员开始尝试使用不同的硬件平台来提高三维重建方法的时效性,包括采 用FPGA[5-6]、GPU[8]、DSP[9]、ASIC[10]等。然而,对于部分资源有限的硬件平台,如FPGA、ASIC等,不能像对待CPU、GPU或DSP的应用程序那样,直接通过简单地添加内存或增加磁盘空间的方法允许相同算法处理更大图像或更大视差范围的问题。其主要原因是:就基于FPGA的应用程序而言,可用逻辑资源数量有限,当逻辑单元耗尽时,唯一的解决方案是添加另一个设备或更改相应算法[11]。这就导致许多本质上是高度迭代性的先进算法因FPGA资源受限难以有效实施。因此,在硬件编程复杂、资源受限的双重压力下,设计一套快速低功耗高精度三维重建方法是极具挑战意义的问题。

针对上述问题,本文基于有限资源FPGA平台,提出改进相位相关立体匹配算法来克服传统FPGA方法易受光照变化、遮挡、阴影及小旋转等因素影响,进而实现从包含低纹理区域、动态纹理区域及大视差范围等干扰因素的真实山地无人机影像中提取高可靠视差信息,大大提高基于FPGA的无人机航拍影像三维重建方法的鲁棒性、准确性及综合能耗等。与已有的研究成果相比,本文的主要贡献如下:

1)基于多尺度深度图融合思想提出一种改进相位相关立体匹配算法,并利用FPGA平台构建低功耗快速实现硬件架构。

2)基于有限资源FPGA平台,结合高并行指令优化策略和高性能软硬件协同优化方法,提出一种层级迭代、同层并行的高吞吐量硬件优化架构。

3)本文方法充分利用FPGA芯片实现对外设影像和三维重建结果的自动处理和存储。此外,从时间、功耗、鲁棒性等方面对相关先进方法,如CPU[3]、GPU[8]等,进行充分的实验对比。

综上所述,本文方法不仅实现了基于无人机航拍影像的快速低功耗高精度三维重建,而且为各立体视觉应用领域提供快速低功耗高精度的三维重建解决方案。因此,本文极具理论意义和现实意义。

1 相关工作

1.1 图像匹配算法

图像匹配作为三维重建流程中的关键步骤之一,可以用于检测目标图像与参考图像之间各像素点的平移距离。在三维重建中,通常采用图像匹配算法实现立体图像对的密集视差图提取。目前,基于图像匹配的视差估计算法大致可分为3类:基于灰度的算法[12-13]、基于特征的算法[14-15]和基于频域的算法[16-17]。

基于灰度的视差估计算法假设目标点与其对应点的图像强度在立体图像对中保持不变,通过找到具有最小灰度值统计距离对应像素块,可计算出这2个图像块之间的位移关系。但在实际应用中,图像容易受到噪声、照明变化和阴影等因素的干扰。因此,基于灰度的视差估计算法的结果在很大程度上取决于图像质量。

基于特征的立体匹配算法主要通过提取图像中的特征描述(如边缘或直线段)来进行图像立体匹配。因此,对于纹理较少、信噪比(SNR)低且前景目标区域较大的图像(即特征描述不稳定且容易混淆的图像),匹配精度会大大降低。除此之外,为了追求更稳定的特征,特征提取过程通常具有很大的计算复杂度。

在基于频域的图像配准算法中,最典型的是基于相位相关的匹配算法[18-20]。该算法主要利用傅里叶变换平移特性来估计2个图像之间的运动矢量。其中,平移特性是指空间域中的位移与频域中的线性相位变化之间的对应关系。基于相关函数的匹配算法不仅具有亚像素精度,还在图像对比度和图像强度方面不受全局线性照明变化的影响[21]。因此,相位相关对噪声具有很高的鲁棒性,适用于噪声较大的场景。与传统的特征提取算法[22]相比,该算法不依赖于特征提取,具有更快的更新速度。

1.2 基于FPGA的相位相关算法

Darabiha等[23]在包含4个Xilinx Virtex2000E FPGA的Transmogrifier-3A(TM-3A)开发板上实现在256×360分辨率图像上以视频速率(30帧/s)生成8-bit亚像素级密集视差图。该系统使用局部加权相位相关算法,最多搜索20个像素范围的视差值。在Darabiha等[23]的研究基础上,Masrani和Maclean[11]使用更先进的硬件平台,包含4个Altera Stratix S80 FPGA的Transmogrifier-4开发板进一步实现以相同速率(30帧/s)处理更大视差范围的更大分辨率(480×640)图像。由于Transmogrifier-4开发板具有更加强大的硬件资源,Masrani和Maclean[11]对局部加权相位相关算法进行了改进。采用2个可移动窗口取代了Darabiha等[23]固定窗口方法进行相位相关计算。虽然多伦多大学团队的2项研究都以30帧/s速率实现三维重建,但很大程度上依赖于包含更大硬件资源的先进设备实现,并且不适用于大分辨率图像。除此之外,Masrani和Maclean[11]提到,理论上最多可以实现128视差范围的搜索,但是大视差范围重建的时间消耗将重新估计。

据调研,截至目前为止,现有通过FPGA平台实现基于相位相关算法的光学影像三维重建研究相对较少,大多研究基本是基于空间域特征实现图像立体配准。Bhatia等[6]在RTAX2000S FPGA上提出了一种利用相位相关算法精确计算月球着陆器水平速度的新方法,在测试实验中,该系统以2帧/s速率运行,但并没有给出所处理图像的分辨率值。Bhatia等[24]在其另一项研究中详细描述了该算法的优点,通过设计一种梯度滤波器,使改进相位相关算法适用于不同强度和对比度的图像序列,进而提高图像匹配精度。

Matsuo等[25]综述了基于多种硬件平台的相位相关算法及其实现,并就相关评价属性对其进行了详细实验比较。其中,硬件平台包括GPU、ASIC和FPGA。最终结果表明,基于GPU的POC算法实现比基于FPGA实现要快近1倍的时间,如果仅考虑二维快速傅里叶变换(2D FFT)运算,则基于GPU实现比基于FPGA快15.5倍左右。虽然从速度上来看,基于GPU平台方法表现更好,但其存在需求性限制问题,如功耗较高。虽然FPGA不需在功耗方面考虑更多,但其硬件资源非常有限,这在无形之中给算法设计及程序实现带来了极高困难。此外,如果使用片外存储器(如SD卡)进行数据传输,更会进一步导致整个系统处理效率下降。因此,设计合理的FPGA硬件架构显得至关重要。

综上所述,目前基于FPGA的相位相关算法在三维重建方面的研究相对较少,依旧处于探索阶段,且大多研究集中在图像匹配领域,在应用层次方面鲜有涉及三维重建技术。基于此,本文在有限资源FPGA平台下,构建多尺度深度图融合算法架构,并结合指令优化策略和软硬件协同优化方法,提出一种基于FPGA高吞吐量硬件优化架构的无人机航拍影像快速低功耗高精度三维重建方法,满足了无人机航拍影像低功耗高时效三维重建的需求,克服了无人机航拍影像三维重建中对高山、阴影和河流等区域视差估计的不可信问题。

2 基于FPGA的无人机航拍影像三维重建方法

近年来,无人机已广泛用于工业检查、遥感、制图和测量等应用领域。但在低空影像三维重建方面,现有无人机航拍影像三维重建方法在功耗、时效等方面无法满足移动终端对低功耗、高时效的需求。因此,越来越多的研究人员将注意力聚焦于低功耗FPGA平台上。尽管在FPGA平台上已经成功部署了许多立体视觉算法,但许多本质上高度迭代或者依赖于不规律内存访问的先进算法,很难在有限资源FPGA平台上实现其高能效性。为了解决上述问题,本文基于Xilinx ZCU104 FPGA评估板,结合高并行指令优化策略和高性能软硬件协同优化方法,提出一种层级迭代、同层并行的高吞吐量硬件优化架构。

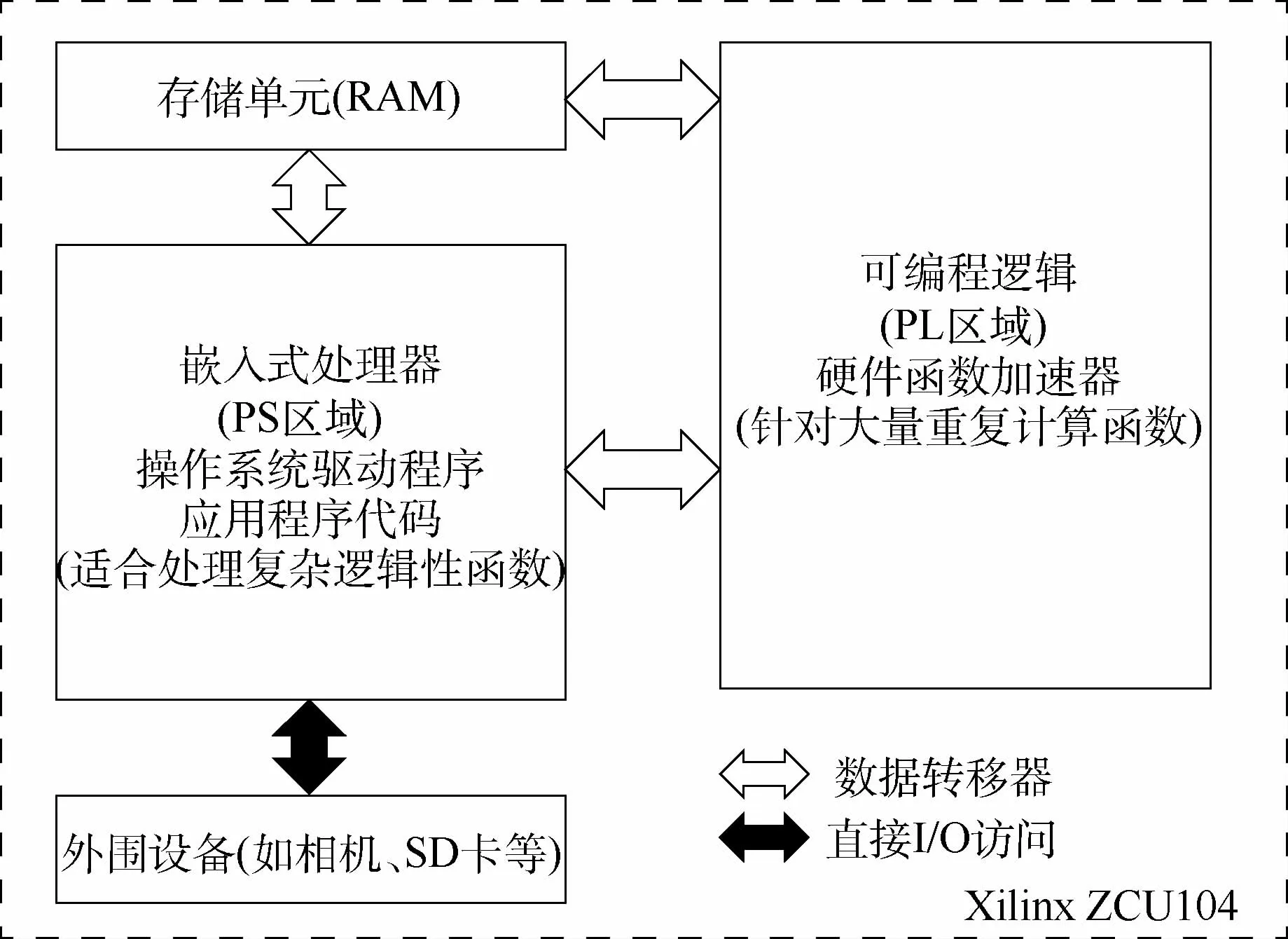

Xilinx ZCU104 FPGA评估板集成了嵌入式处理器(见图1中PS区域)与可编程逻辑(见图1中PL区域),既拥有ARM 处理器灵活高效的数据运算和事务处理能力,又集成了FPGA的高速并行处理优势。因此,在系统开发时,通常可以利用软硬件协同优化方式将PL区域的硬件函数映射为PS区域一个或多个具有特定功能的外围设备。Xilinx ZCU104 FPGA系统的体系结构如图1所示。一般来说,PS区域主要负责整个系统的算法调度,以及执行具有复杂逻辑操作算法模块,而大量重复性计算通常交由PL区域执行,利用高并行指令硬件加速函数。

本文方法主要包含外围设备、嵌入式处理器(PS区域)、可编程逻辑(PL区域)、存储单元(RAM)4部分。其中,外围设备包括搭载在无人机上的相机或SD卡。主要流程为(见图2):FPGA读取无人机相机捕获到的航拍图像序列,并对其执行预处理对齐操作,再对对齐立体图像对使用改进相位相关立体匹配算法进行视差估计,最终将多层视差图融合结果存储在SD卡中。

图1 基于Xilinx ZCU104 FPGA系统的体系结构Fig.1 System structure based on Xilinx ZCU104 FPGA

图2 基于FPGA快速低功耗高精度三维重建方法流程Fig.2 Flowchart of fast,low-power and high-precision 3D reconstruction method based on FPGA

2.1 改进相位相关立体匹配算法

假设f1(x,y)、f2(x,y)分别表示无人机相机捕捉的2幅图像,满足以下关系:

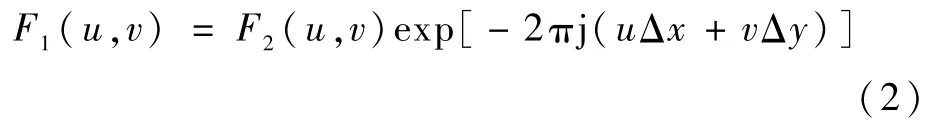

即f1(x,y)平移(Δx,Δy)向量后可以得到f2(x,y),而改进相位相关立体匹配算法的目标是:求解具有亚像素级精度的平移向量(Δx,Δy)。首先,对式(1)进行傅里叶变换得

式中:F1(u,v)、F2(u,v)分别为图像f1(x,y)、f2(x,y)的频域信息。

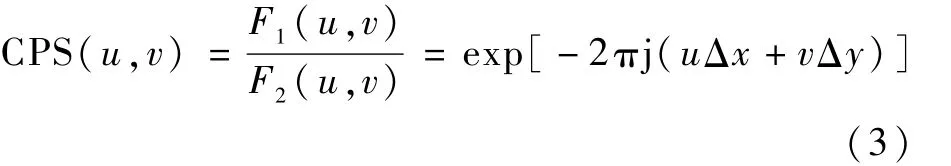

进一步,用2幅图像的归一化互功率谱表示其相位相关性。

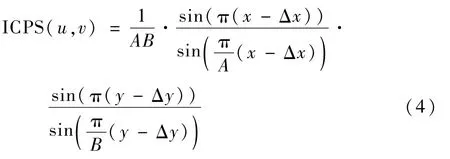

归一化互功率谱的傅里叶逆变换结果是空间域脉冲函数δ(x-Δx,y-Δy),其对应的Dirichlet函数为

式中:A和B分别为图像块的宽和高。

式(4)可使用sin函数进行拟合,近似为

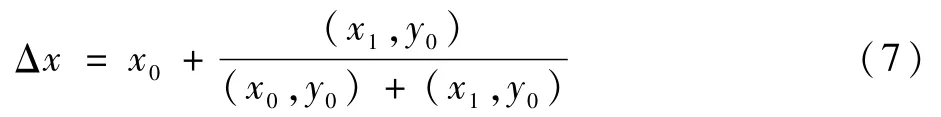

由于二维矩阵中各维度积分计算互不干涉,在下面的证明中只描述一维,这一结论也适用于其他维度。假设(x0,y0)为该维上最高点的坐标,(x1,y0)为与最高点相邻的第二最高点,当满足x1=x0+1时,则

因此,在x方向上最大峰值点的亚像素平移为

2.2 多尺度深度图融合算法

Liu和Hong[26]指出,当使用基于相位相关算法进行三维重建时,其精度依赖于PC窗口的选择。如果窗口太小,不能覆盖足够大范围的像素变化,则无法准确地提取出较大范围的视差信息,在低纹理区域的重建结果也变得不可靠;如果窗口过大,则不仅难以识别局部细节信息,还会造成图像边界溢出。

为了解决上述问题,本文采用多尺度深度图融合思想进行视差优化,与CPU方法[3]和GPU方法[8]类似,利用上一层视差结果引导下一层视差图计算,充分结合不同尺寸窗口下PC计算优势,大大提高三维重建精度。具体的融合操作为:在下一层视差图计算的子像素块提取操作中,使用上一层视差结果作为该点子窗口提取的偏移量,实现在粗粒度视差结果基础上进行细粒度的视差计算,此时,粗粒度视差加上细粒度视差就是该层最终视差结果。

完整的多尺度深度图融合算法流程如图3所示。其中,图片A表示初始窗口下的视差图结果,图片B表示在初始窗口与减小窗口2种尺寸下的视差图融合结果,图片C表示3种不同尺寸窗口的视差图融合结果。从实验结果可以看出,当迭代次数为1时,视差图A中存在较为明显的边缘效应;而当迭代次数为2时,在视差图A引导下通过减小窗口尺寸后视差计算生成更为精细的纹理结构(见视差图B),但仍存在细微的边缘效应;当迭代次数为3时,通过迭代更小窗口的视差结果使视差图C具有非常高的视差精度,几乎不存在肉眼可见的边缘效应。因此,使用多尺度深度图融合算法可以生成高精度的重建结果。

算法1 多尺度深度图融合算法。

输入:无人机航拍影像对(左图f、右图g)。

输出:视差图M。

初始化:深度图迭代3次,窗口尺寸分别为W1、W2、W3,每次窗口移动S1、S2、S3次。

1.BEGIN

2.利用W1窗口,对无人机航拍图像对f、g分别取值,得到W1大小的子图像块f1、g1。

图3 多尺度深度图融合算法流程Fig.3 Multi-scale depth map fusion algorithm flowchart

3.分别对子图f1、g1进行二维快速傅里叶变换(2D FFT)得到F1、G1。

4.利用式(3)求得归一化互功率谱c1。

5.对c1进行二维快速傅里叶逆变换(2D IFFT)求得矩阵C1。

6.搜索C1矩阵中最大值所在位置(x0,y0),以及x方向的次大值(x1,y0),y方向的次大值(x0,y1),利用式(7)求得x方向的亚像素精度平移xm,同理可求得y方向的亚像素精度平移ym,则W1窗口位置的最大视差为(xm,ym)。

7.重复移动W1窗口位置S1次,重复步骤2~步骤5,得到W1窗口下的视差图M1。

8.改变窗口尺寸为W2,将W1视差结果作为W2窗口下子图像块提取的偏移量,对无人机航拍图像对f、g分别取值,得到W2大小的子图像块f2、g2。重复步骤3~步骤6,得到视差图M2。

9.改变窗口尺寸为W3,重复步骤8,得到多尺度深度图融合结果M。

10.END

2.3 基于FPGA平台的三维重建架构

在基于GPU平台实现无人机航拍影像三维重建时,Li和Liu[8]使用单指令多数据流(Single Instruction Multiple Data,SIMD)体系架构和统一计算设备架构的快速傅里叶变换(CUDA Fast Fourier Transform,CUFFT)方法独立计算每个点的视差值,但该方法依赖于大量的硬件资源支持(如2 GB显卡内存),是一种典型的利用大量硬件资源换取高效性能的实现方式。不同于GPU方法,基于有限资源FPGA平台(如38 MB内存Xilinx ZCU104 FPGA评估板),研究人员将更多精力投入到软硬件协同优化方案的选择、高并行指令优化硬件加速模块等方面,通过设计一种层级迭代、同层并行的高吞吐量硬件优化架构,实现基于无人机航拍影像的快速低功耗高精度三维重建。

为将多尺度深度图融合算法在Xilinx ZCU104 FPGA平台上高效运行,结合高并行指令优化策略和高性能软硬件协同优化方法,提出一种层级迭代、同层并行的高吞吐量硬件优化架构。该方法实现的具体步骤如下:

步骤1 在CPU平台上开发出满足算法需求的可移植版本。

步骤2 将CPU版本移植到FPGA的嵌入式处理器(PS区域)。

步骤3 软硬件协同优化设计,根据方法每个模块算法特性,将适用于硬件加速的模块在可编程逻辑(PL区域)实现。

步骤4 对PL区域的硬件加速模块进行高并行指令优化。

步骤5 完成编译并在Xilinx ZCU104 FPGA评估板运行,如果出现硬件资源不足无法编译或者执行效率达不到要求等情况,则返回步骤3调整软硬件协同优化方案,直到选择出满足要求的硬件架构。

2.3.1 2D FFT硬件实现

2D FFT是基于FPGA相位相关三维重建技术中最重要的环节之一。与基于CPU、GPU平台直接调用2D FFT函数不同,Xilinx ZCU104 FPGA评估板仅支持一维快速傅里叶变换(1D FFT)IP core,因此需要自主开发2D FFT模块。在进行2D FFT模块硬件开发时,根据傅里叶变换可分离性质,可以将其转化成2个1D FFT实现。值得注意的是,这里存在一个重要的数据依赖关系,只有当图像块矩阵中所有元素都完成一维行FFT之后,才能进行一维列FFT变换(见图4)。笔者认为,这是相位相关算法难以在FPGA平台上快速实现的主要原因之一。同理,在傅里叶逆变换过程中,2D IFFT模块也是先转换成1D行IFFT变换后再进行1D列IFFT变换。此外,Xilinx官方提供的1D FFT输入输出均为浮点复数形式,因此,还需将输入图像块矩阵转换成浮点复数形式。

图4 2D FFT模块数据依赖关系示例Fig.4 Example of 2D FFT module data dependency

2.3.2 软硬件协同优化

Xilinx公司的Xilinx ZCU104 FPGA评估板提供了一个灵活的原型设计平台,ZU7EV设备集成了四核ARM Cortex-A53处理系统和双核ARM Cortex-r5实时处理器,为应用开发者提供了前所未有的异构多处理能力。为了充分发挥异构平台的灵活性等优势,需要综合考虑每一种可能的软硬件协同优化方案,并对不同方案优缺点进行综合分析,才能选择出最适合的硬件架构。软硬件协同优化具体是指:开发者需要根据嵌入式处理器(PS区域)灵活高效的数据运算和事务处理能力,以及可编程逻辑(PL区域)高速并行处理的性能特点,为其分配相应功能,保证整个系统高效运行。

本文方法的目的是:在有限资源FPGA平台上实现多尺度深度图融合算法高效运行,但由于该算法的复杂性、不规律数据访问及迭代性,如果对每一个模块都按最高性能设计,则必将导致过多资源被占用。换句话说,如果一味追求最佳时效,则FPGA平台的有限硬件资源无法支持整个系统运行。因此,要想在有限资源FPGA平台上实现三维重建系统的所有功能,必须结合各种类型硬件资源使用情况,进行合理高效的软硬件协同优化。

在对无人机航拍影像序列进行子图像块提取时,一般会涉及到取窗口、边缘填充判断、不连续的内存读写及赋值运算等操作。此时,如果直接将无人机航拍影像序列从PS区域转移到PL区域内存中,再进行子图像块提取,则不需要每次都将子图像块从PS区域转移到PL区域,进而降低了时间消耗,提高系统处理速度,但是这种方法势必会消耗PL区域大量的内存资源。而如果考虑在PS区域中完成子图像块提取操作,再将子图像块转移到PL区域进行下一步计算,则会最大程度上节省PL区域内存资源占用,但是由于每次执行子图像块提取操作都需要从PS区域转移到PL区域,会在一定程度上增加时间成本,进而影响系统的整体性能。因此,基于有限资源FPGA平台的三维重建方法设计往往是在硬件资源与时效性之间的一种综合考量。一般而言,只有实现整个系统的基本功能之后,才会进一步考虑如何最大程度利用硬件资源的同时实现系统的最高性能。

本文方法的软硬件协同优化方案如图5所示。该方案具体流程为:FPGA将无人机相机捕获到的航拍图像序列临时存储在RAM 中,再通过数据转移器交由PS区域与PL区域进行协同优化,最终将重建结果永久保存在SD卡中。此时,SD卡中的视差图可直接转换成需要的高程数字模型。其中,包含大量重复性计算功能的相位相关函数在可编程逻辑(PL区域)执行,而嵌入式处理器(PS区域)主要负责无人机航拍影像读取、取窗口、移动窗口、减小窗口、亚像素级视差估计及最终重建结果保存等复杂性逻辑操作。

2.3.3 高并行指令优化

图5 软硬件协同优化流程Fig.5 Hardware-software co-design flowchart

本文方法并行架构设计时,主要利用pipeline(流水线)及dataflow(数据流)高并行指令进行优化。在底层代码中,主要使用pipeline指令对for循环代码进行展开,pipeline指令可以通过允许操作的并发执行来减少一个函数或循环的启动间隔,以此达到提高系统吞吐量的目的。dataflow指令可以支持任务级管道处理,其允许函数和循环在各自的操作中进行重叠,这将增加RTL实现的并发性,进而可以增加设计的总体吞吐量。

为了最大程度降低正向、逆向二维快递傅里叶变换(FFT、IFFT)中数据依赖关系对整个系统性能造成的影响,在设计相位相关计算模块时,本文使用dataflow指令对频域转换、归一化互功率谱计算及2D IFFT三个函数进行并行加速,通过覆盖内存读写的时间消耗,最大程度上增加系统吞吐率。具体的操作为:将频域转换中一维列FFT、互功率谱计算及2D IFFT中一维行IFFT三个操作合并成一个中转模块(见图6),将中转模块、频域转换中一维行FFT模块及2D IFFT中一维列IFFT模块合并成一个硬件函数,并使用dataflow指令对其并行加速。

图6 中转模块设计示意图Fig.6 Schematic diagram of transfer module design

3 实验评价

本文方法在Xilinx ZCU104 FPGA评估板上实现了完整的基于无人机航拍影像的快速低功耗高精度三维重建方法。实验图像采用Liu[26]、Li[3,8]等的无人机航拍影像数据,该组影像数据来源于中国西南山区拍摄的真实无人机图像序列。为了方便进行方法测试,从中选择了2张无人机航拍图像,并存储在SD卡中,用于测试的图像分辨率为1 068×712。

Xilinx ZCU104 FPGA评估板提供了一个灵活的原型设计平台,该平台具有高速DDR4内存接口、FMC扩展端口、每秒千兆串行收发器、各种外围接口和可定制设计的FPGA结构。在Xilinx ZCU FPGA评估板上装有Zynq UltraScale+XCZU7EV-2FFVC1156 MPSoC,其在同一器件中结合了功能强大的嵌入式处理系统(PS区域)和可编程逻辑(PL区域),共具有504 000个系统逻辑单元(LUT)、461 000个CLB触发器(FF)、38 Mb存储器(RAM)。在评估实验中,本文方法使用Xilinx官方提供的新一代SDSoCTM软件开发工具进行系统开发。其中,表1的数据来源于Xilinx官方软件SDx提供的HLS报告;表2及FPGA功耗数据来源于Xilinx官方软件Vivado提供的项目综合报告;CPU方法[3]、GPU方法[8]及本文方法分别基于4 GB RAM内存资源的AMD Athlon II x2 240型号CPU(2.80 GHz)、英伟达GTX760型号GPU(2 GB显存)及Xilinx ZCU104 FPGA(38Mb RAM内存)评估板实现。

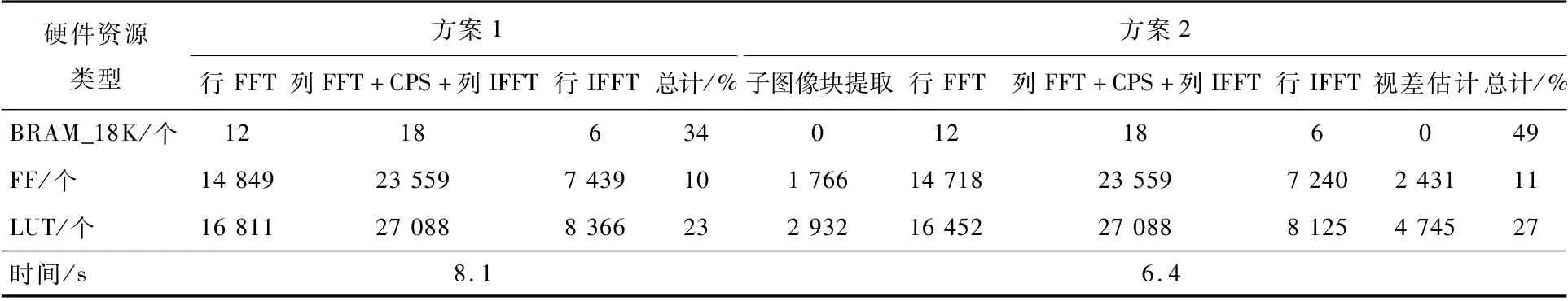

表1 不同软硬件协同优化方案对比Table 1 Comparison of different hardware-software co-design solutions

表2 不同指令优化策略对比Table 2 Comparison of different instruction optimization strategies

3.1 不同软硬件协同优化方案对比

在软硬件协同优化设计方面,有针对性地选择了3个具有代表性的软硬件协同设计方案,为了方便比较,仅考虑在初始窗口下的视差图计算,具体分区方案如图7所示。

软硬件协同优化方案1的具体细节包括:①将测试用的无人机航拍图像对读取到嵌入式处理器(PS区域)中,并进行初始大小窗口的子图像块提取操作,再通过数据转移器DMA传入PL区域。②在PL区域通过2.3.3节描述的高并行相位相关计算模块,即利用dataflow指令对频域转换、归一化互功率谱计算及2D IFFT三个函数进行并行加速,求得空间域脉冲函数。③将脉冲函数转移到PS区域中,再使用sin函数对空间域脉冲函数进行亚像素级视差估计,这是因为峰值拟合时需要进行大量逻辑判断操作,更适用于嵌入式处理器实现。④在PS区域进行移动窗口提取子图像块操作,再重复步骤①~步骤③,直到获得初始窗口下的完整视差图。

软硬件协同优化方案2基于方案1,在方案2中,将无人机航拍图像对转移到PL区域后,再进行子图像块提取、相位相关计算及亚像素级视差估计等操作。而软硬件协同优化方案3是在方案2基础上的一次大胆尝试。为了最大程度地提升系统性能,在方案3中,使用dataflow指令对子图像块提取操作进行并行优化加速。然而,在程序编译时,编译器提示因RAM资源不足导致无法编译。因此,在软硬件协同优化方案对比实验中,主要对方案1和方案2进行详细的实验对比论证。

为了对2种方案进行更深层次的比较研究,本文分别列出了其在FPGA平台实现时所占用的硬件资源情况,具体如表1所示。实验结果证明,虽然方案2比方案1节省了约20%的时间,然而方案2仅初始大小窗口下的视差计算就占用了整个FPGA近一半的BRAM_18K(18Kb Block RAM块随机存储器)资源,最终导致该方案无法实现多尺度深度图融合算法的三维重建。

因此,考虑到FPGA硬件资源有限,本文方法最终选择方案1的软硬件协同优化方案。

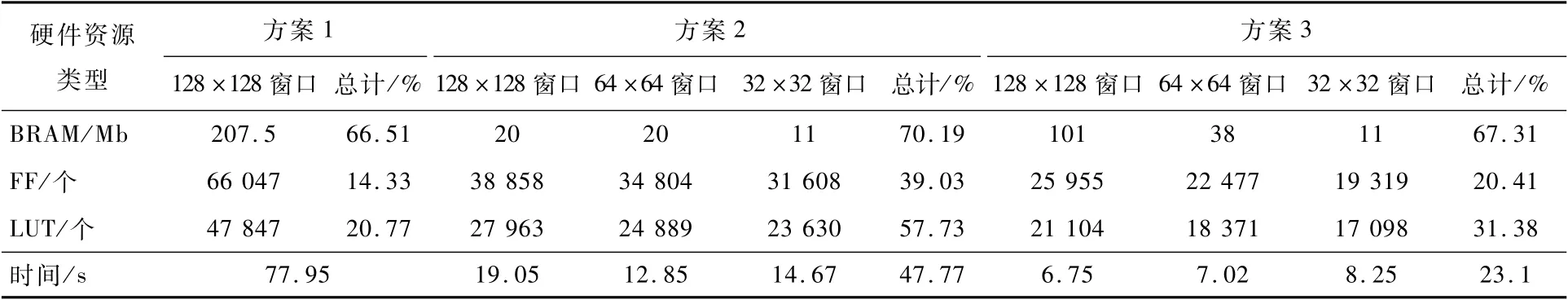

3.2 不同指令优化策略对比

在指令优化策略方面,为了验证本文方法高并行指令优化策略的有效性,列出了3种不同指令优化策略进行比较,具体描述如下:

1)方案1仅使用pipeline指令对相位相关计算模块中取窗口、频域转换、归一化互功率谱计算及2D IFFT等硬件加速函数分别优化。

2)在方案2中,将频域转换中一维列FFT、互功率谱计算及2D IFFT中一维行IFFT三个函数合并为一个中转模块,并与频域转换中一维行FFT模块及2D IFFT中一维列IFFT模块3个硬件函数分别使用dataflow指令优化并行加速。

3)方案3是本文方法所采用的高并行指令优化策略,即将方案2提到的中转模块、频域转换中一维行FFT模块及2D IFFT中一维列IFFT模块合并成一个硬件函数后,使用dataflow指令对其并行加速。

3种不同指令优化策略实验结果如表2所示。其中,包括方案1在128×128分辨率窗口下生成视差图所消耗的硬件资源情况及执行时间,方案2及方案3分别在128×128、64×64、32×32分辨率窗口下生成视差图及实现三层视差图融合三维重建方法所消耗的硬件资源情况、重建时间。表2结果显示,采用方案1指令优化策略,仅128×128分辨率窗口下的视差计算就消耗整个评估板66.51%的BRAM(块内存)硬件资源,甚至无法完成第2层的视差图重建,笔者认为导致方案1性能差的主要原因是:未充分利用不同函数之间的数据依赖关系而进行指令优化。而方案2和方案3虽然都成功实现了三层视差图融合三维重建,但由于方案2未对不同函数模块之间的内存读写等待进行优化,导致硬件函数执行效率不高。

图7 三种软硬件协同优化方案示意Fig.7 Schematic diagram of three hardware-software co-design solutions

因此,本文方法最终采用方案3高并行指令优化策略,相比于其他方法,所消耗资源更少,重建速度更快,具有更高效性能。

3.3 与同领域先进方法的综合性比较

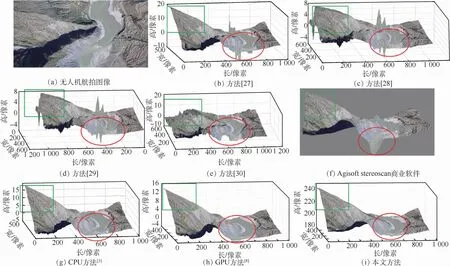

3.3.1 鲁棒性

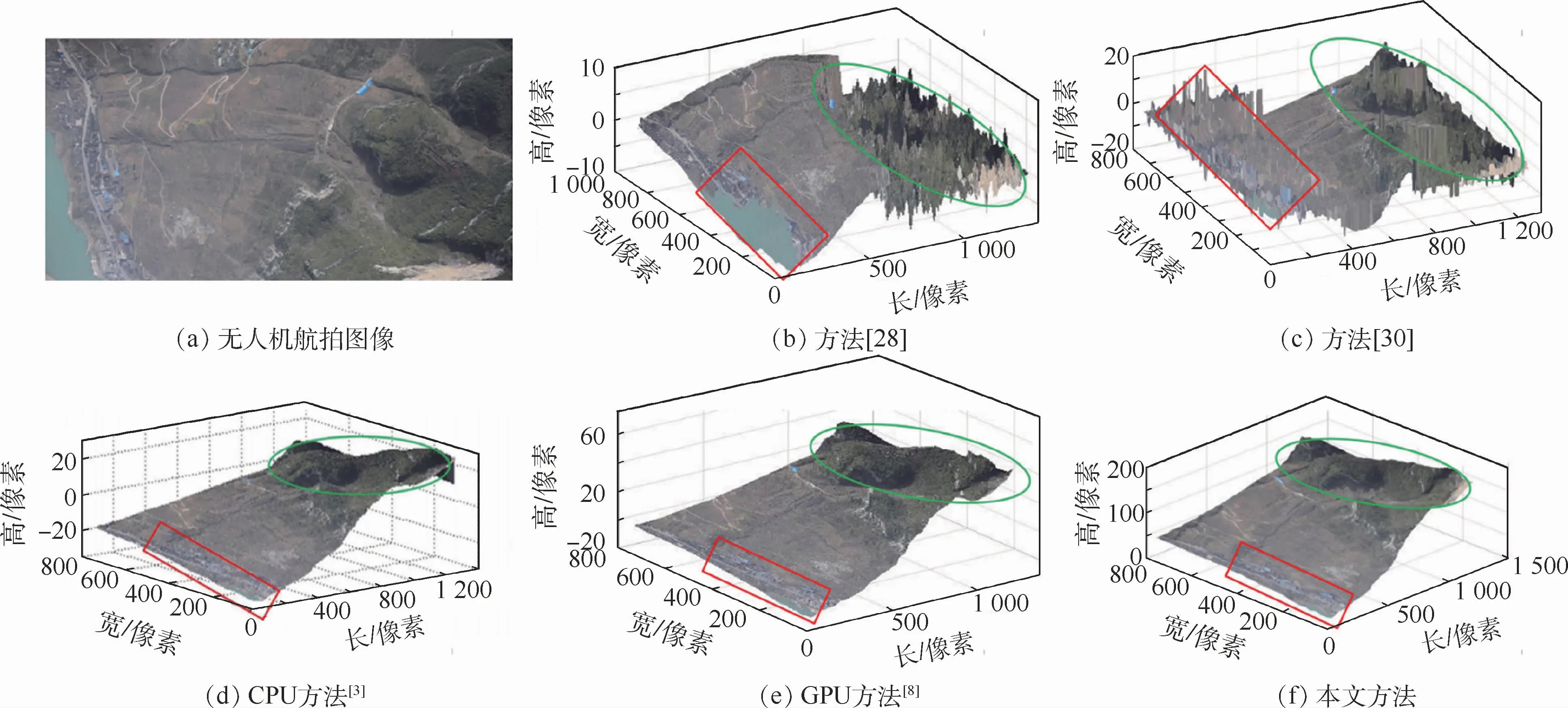

将本文方法与其他7种先进方法(方法[27]、方法[28]、方法[29]、方法[30]、Agisoft stereoscan商业软件方法(http://www.agisoft.com)、CPU方法[3]及GPU方法[8])进行比较研究。其中,初始参数设置如下:层次化方法[27-28]使用32×32初始窗口来估计视差;方法[29-30]使用32×32固定窗口来估计视差;对于Agisoft stereoscan商业软件方法,使用其默认初始参数;CPU方法[3]、GPU方法[8]和本文方法的初始窗口、初始采样间隔和初始运动矩阵的初始参数分别设置为128×128像素、16像素和0。此外,在MATLAB平台上测试 了CPU 方 法[3]、基 于 层 次 的 方 法[27,29-30],并在Visual Studio环境中比较了方法[28]和GPU方法[8]。因此,假设上述方法具有最合适的初始条件和环境。值得注意的是,虽然本文中的视差3D网格模型不是真正的数字高程模型(Digital Elevation Model,DEM),但这不影响系统性能的分析和比较。具体三维重建结果如图8所示,其中矩形和椭圆分别代表重建结果中高山区域和河谷区域。实验结果表明,方法[28]、方法[29]及方法[30]的矩形区域和椭圆区域重建结果严重失真,即受高山区域和河谷区域影响很大,而方法[27]与Agisoft stereoscan商业软件的矩形区域成功恢复出高山地形特征,但是在椭圆区域却无法重建出河流区域的场景结构,只有CPU 方法[3]、GPU方法[8]与本文方法同时恢复出高山区域和河流区域的场景结构。

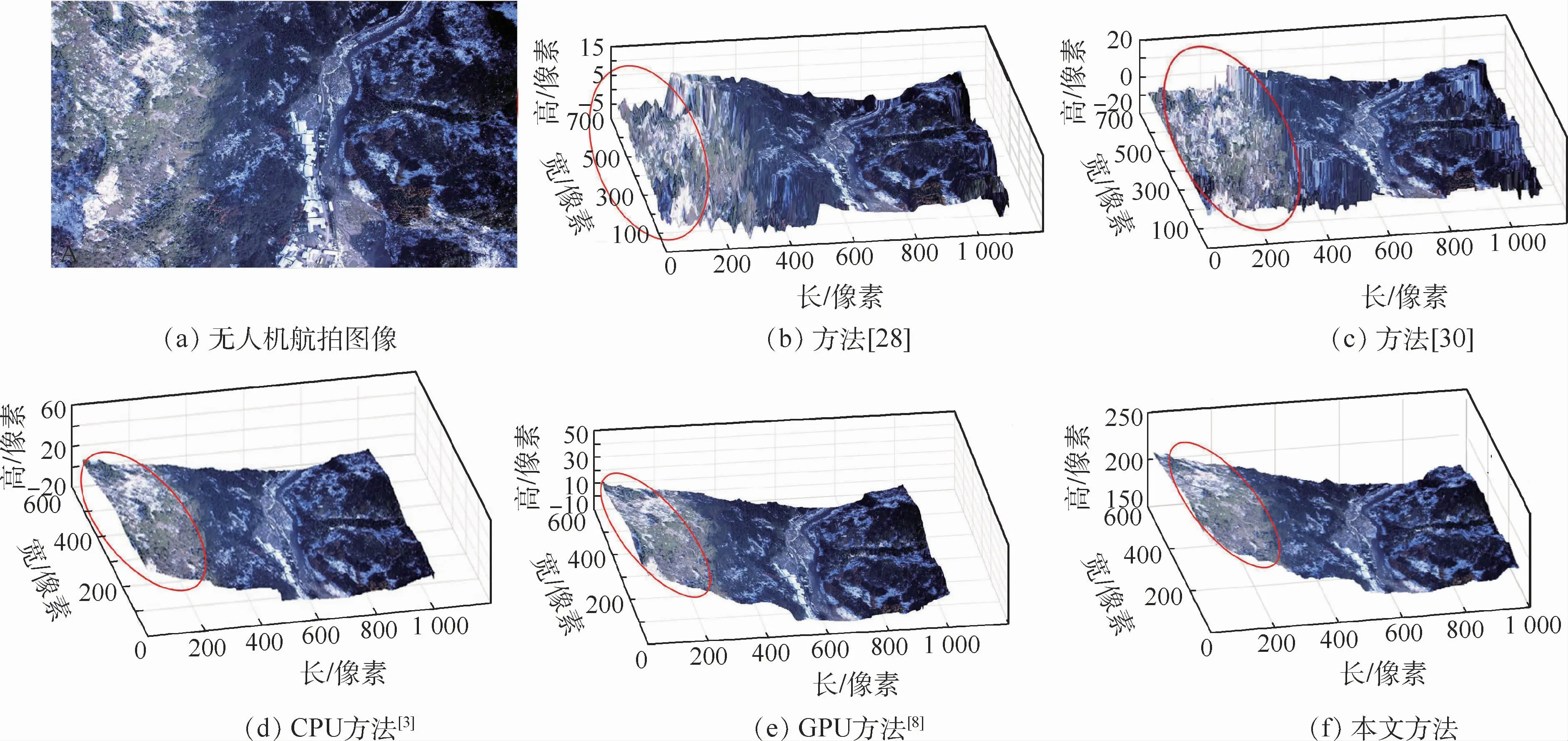

因此,本文方法与CPU方法[3]、GPU方法[8]的重建结果相近,并显著优于现有方法[27-30]及Agisoft stereoscan商业软件的重建结果,表现出很强的鲁棒性。除此之外,为了充分证明本文方法的优越性,进一步提供了2组无人机图像的测试结果,分别如图9和图10所示。在图9中,矩形和椭圆分别代表重建结果中河流区域和高山区域。实验结果表明,方法[28]和方法[30]的矩形和椭圆区域重建结果受高山区域和河流区域影响严重,而CPU方法[3]、GPU方法[8]及本文方法可最大程度地减少高山和河流的影响。另外,在图10中,椭圆代表重建结果中山脉地区。实验结果表明,方法[28]和方法[30]的椭圆区域重建结果受山脉地区影响很大,几乎不能生成有效的重建结果。而CPU方法[3]、GPU方法[8]与本文方法可充分提取高山无人机图像的三维场景结构。因此,本文模型对高山、河流区域及山脉地区的无人机航拍影像具有很强的鲁棒性,并高度适用于多种复杂环境的无人机航拍图像。此外,本文方法在功耗及时效上具有更优异的表现。为了对本文方法的性能进行综合评估,将在3.3.2节从功耗及时效性方面,基于CPU方法[3]及基于GPU方法[8]进行进一步对比分析。

图8 与先进方法重建结果比较Fig.8 Comparison with reconstruction results of state-of-the-art methods

图9 高山、河流区域无人机图像的测试结果Fig.9 Test results of UAV image of mountain and river areas

图10 山区无人机图像的测试结果Fig.10 Test results of UAV images of mountain area

3.3.2 功耗和时效性

图11 基于CPU、GPU、FPGA方法的功耗和时效性比较Fig.11 Comparison on power consumption and time consumption based on CPU,GPU and FPGA methods

对本文方法与基于CPU[3]、GPU[8]平台的三维重建方法,在执行时间、功率损耗两方面进行详细比较。实验结果如图11所示。实验数据显示,基于有限资源FPGA方法,在时间消耗上达到与基于GPU方法相近的结果,并且与基于CPU平台方法相比,其时效性提高了近20倍;另外,在功耗方面,基于FPGA方法的功耗远远低于GPU方法,仅为基于GPU方法的2.12%,与基于CPU方法相比,基于FPGA 方法是基于CPU 方法的7.42%。综上所述,本文方法成功使用有限资源FPGA芯片,实现了无人机航拍影像快速低功耗三维重建。为了进一步展示本文模型的高精度特性,将在3.3.3节从模型精度方面进行进一步分析。

3.3.3 精 度

为了充分展示本文模型的高精度特性,基于一 组 人 工 合 成 图 像 对 FPGA 方 法 和 CPU[3]、GPU[8]平台的三维重建方法,在模型精度方面进行详细比较。首先,设计了一张尺寸为512×512像素的脉冲噪声图像(噪声密度为0.5)。然后,为了模拟精度为1.5的亚像素平移,将上述图像中央的100×100像素正方形区域在x轴上平移1.5个像素之后的结果作为目标图像。最后,分别使用本文方法与CPU[3]、GPU[8]方法对上述立体图像对进行三维重建。值得注意的是,由于FPGA平台生成的视差结果以BMP位图图片格式存储,当利用MATLAB平台读取视差结果并进行三维可视化显示时,视差结果会自动转换为0~255范围的灰度值大小,需将其按比例缩放到相应尺寸显示。重建结果如图12所示。根据图12可视化结果和表3定量评估结果显示,本文方法成功基于有限资源FPGA芯片生成接近于CPU和GPU方法精度的三维重建结果。因此,本文方法具有亚像素级视差精度的三维重构能力。

图12 基于合成图像的三维重建结果可视化Fig.12 Visualization of 3D reconstruction results based on synthetic images

表3 基于CPU、GPU、FPGA平台三维重建方法的定量评估结果Table 3 Quantitative evaluation of 3D reconstruction results based on CPU,GPU and FPGA methods

4 结 论

本文结合高并行指令优化策略,提出了一种基于FPGA软硬件协同优化方案的快速低功耗高精度三维重建方法。

1)本文方法实现了对无人机航拍影像中复杂低纹理区域、动态纹理区域及大视差范围区域的低功耗快速高精度的视差信息求解。

2)本文方法能够在单个FPGA上实现包括预处理和后处理阶段等完整三维重建方法,如无人机航拍图像序列读取、子图像提取、视差计算、亚像素级视差拟合及重建结果保存等。

3)为了对本文方法进行全面评估,基于CPU、GPU及FPGA平台的方法进行了对比研究,实验结果表明,本文方法在执行速度方面可与GPU方法相媲美,更在功耗方面明显优于GPU方法。

在未来的工作中,将尝试在硬件架构(如多FPGA系统)或算法等方面,对三维重建方法的质量和重建速度进行进一步的优化,或考虑在立体视觉的其他应用领域展开探索。