TFT-LCD白点不良机理研究及改善

2021-04-10高玉杰林鸿涛毛大龙盛子沫郭会斌

刘 信, 高玉杰, 郭 坤, 杨 志, 程 石, 林鸿涛, 毛大龙,盛子沫, 赵 剑, 吴 伟, 郭会斌, 江 鹏

(1. 武汉京东方光电科技有限公司,湖北 武汉 430040;2. 北京京东方显示技术有限公司,北京 100176)

1 引 言

随着生活水平提升,人们对显示器的品质需求越来越高,高分辨率、高刷新频率、高对比度、高亮度等高端产品逐渐占领市场。高端产品开发必然带来成本和周期的上升,进而影响企业收益,因此各企业不断采取各项措施来降低产品开发和生产成本[1-2]。四道掩膜版工艺是各工厂为降低生产成本而普遍采用的一种曝光工艺,相比于五道掩膜版工艺,减少了一道光刻工艺,即有源层和数据线采用一道掩膜版完成,用半曝光替代全曝光,减少工艺流程,提升工厂产能,增加产品收益。但四道掩膜版工艺会使数据线下方存在有源层,在显示器使用时,光照会使有源层导电,等效于数据线宽度增加[3-4]。高端产品的设计,在考虑工艺波动的情况下,其走线宽度和间距均处于极端值,四道掩膜版工艺带来的实际数据线宽度增加加重了液晶显示器的负载,影响产品画质及良率,本文研究的白点不良就是其中的一例。

对于任何一种高端显示器的开发,产品性能和良率一样重要。本文主要研究了四道掩膜版工艺导致白点不良的原因,通过光照和高温实验,明确了不良发生的机理。同时研究了栅极和源极的耦合电容及子像素存储电容对白点不良的影响,通过工艺调整相应的几何尺寸和膜厚,解决白点不良,为后续高端产品的四道掩膜版设计及工艺提供了可行性方案。

2 实 验

实验选择尺寸和分辨率相同的模组,将其分为4组,用于光照实验。选用不同工艺模组产品A、B、C、D研究栅/源极电容与白点的关系;模组产品B、E用于研究子像素存储电容与白点的关系。

2.1 直流实验

TFT-LCD正常显示时,栅极和数据信号均为交流电。对于数据信号,本实验将柔性电路板除掉,酒精清洗各向异性导电胶,在焊盘(Bonding Pad)涂上银浆,外接直流电源,可实现数据信号为直流电。该样品采用栅极驱动功能集成在阵列基板上的GOA(Gate Driver on Array)设计[5-6],将GOA所有信号CLK/STV/VDDO/ VDDE/VGL等设置为高电压,可实现栅级直流信号。实验时观察并记录白点现象等级。

2.2 光照实验

第1组(1-1#~1-3#)为参考组,TFT朝下放置(正常放置),被背光源照射;第2组(2-1#~2-3#)彩膜朝下放置(翻转放置),被背光源照射;第3组(3-1#~3-3#)在正常放置情况下,将白点区域下方用黑色垫片遮挡,样品背光源光照;第4组(4-1#~4-3#)在正常放置情况下,将白点以外其他区域下方用黑色垫片遮挡,样品背光源光照。以上实验每隔24 h进行观察,以上分别记录白点现象等级。

2.3 高温存储实验

将完成光照实验的第1组样品(1-1#~1-3#)放入高温炉中,温度为150 ℃,每隔2 h,进行现象观察,记录白点现象等级。

3 结果与讨论

3.1 电信号对白点的影响

为研究扫描/数据信号对白点不良的影响,本文设计了不同组合的信号加载到显示屏上,观察白点现象,其结果如表1所示。

表1 扫描/数据信号与白点现象的关系Tab.1 White dot phenomenon vs. gate/data signal

从表1可以看出,施加直流扫描信号时,白点消失。相比于交流,直流无电压跳变,可以消除数据线与扫描线的电容对像素电压的影响,即反冲电压(ΔVp)[7-8]的影响。施加直流数据信号时,白点消失,此时扫描信号仍为交流,ΔVp的存在会影响像素电压,但数据信号处于直流,即使扫描信号处于关闭状态,由于漏电流的存在,像素仍处于一定的充电状态,可以抵消大部分由于ΔVp不同导致的像素电压差异。另外,同时给扫描/数据线施加直流信号,白点依然消失。以上实验结果说明,白点不良是由于存在ΔVp,导致白点与其他区域的像素电压不同,使其最佳公共电压不一致,从而出现黑白的差异,导致白点,以下做详细说明。

如图1所示,公共电压的电位是依据屏内多数像素闪烁程度确定的,可以认为对于多数像素,公共电压的电位是在综合考虑了ΔVp和漏电流的基础上,保证了像素的正负帧电压的对称(大小设为a)。但对于白点区域,由于该区域的ΔVp与其它区域存在差异,因此白点区域与其他区域的最佳公共电压存在差异(设为c,可正可负)。

图1 像素与公共电极间的电压示意图Fig.1 Schematic illustration of the voltage between the pixel and the common electrode

本样品为常黑模式,像素电极与公共电压之间的有效电压越大,像素的亮度越高。因此,对于正常区域和白点区域,像素亮度可以分别用式(1)和式(2)定性地表示。

正常区域亮度:

a2+a2=2a2

(1)

白点区域亮度:

(a+c)2+(a-c)2=2(a2+c2)

(2)

显然,白点区域亮度高于正常区域亮度,因此该区域发白。

3.2 光照/温度对白点的影响

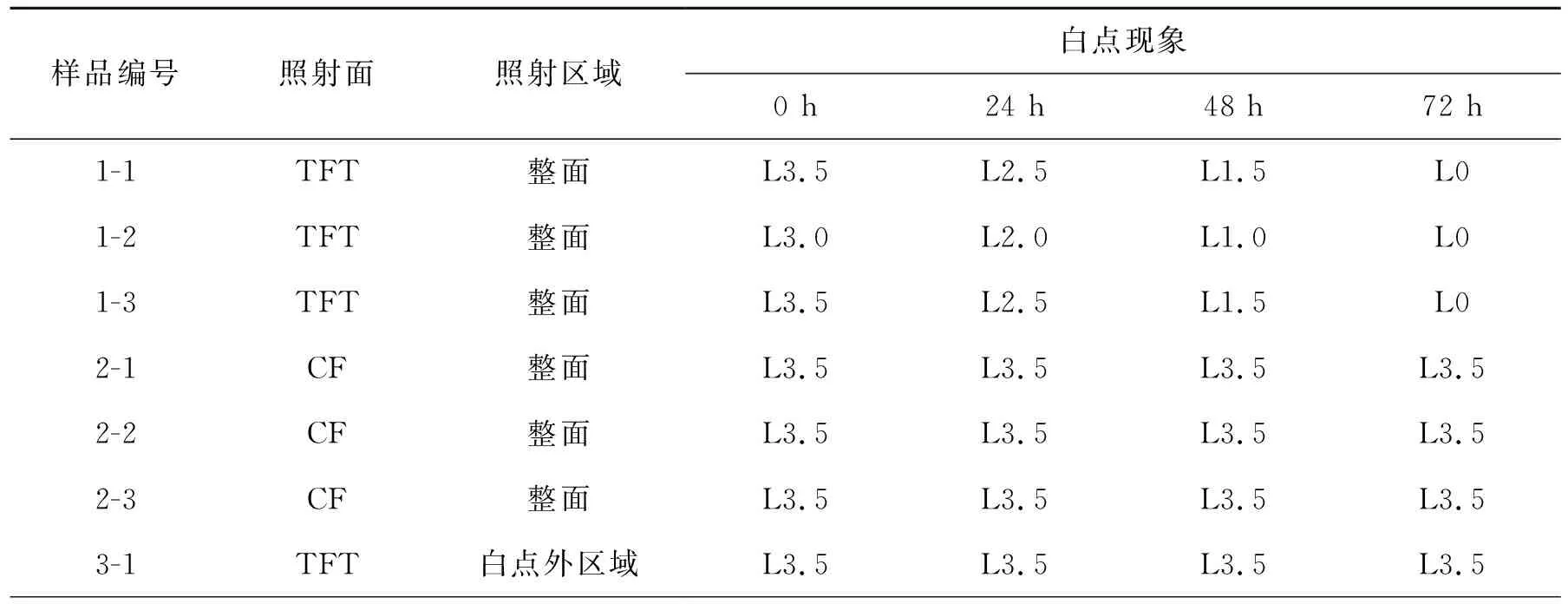

我们研究了照射不良样品的不同区域,白点的变化情况,并对其中部分样品进行了高温存储实验,结果见表2和表3。

表2 光照条件与白点现象的关系Tab.2 White dot phenomenon vs. light conditions

续 表

表3 高温老化与白点现象的关系Tab.3 White dot phenomenon vs. high temperature aging

从表2、3可以看到,TFT朝下放置状态下被背光源照射,白点不良逐渐减轻;彩膜朝下放置状态下被背光源照射,白点不良无变化。同时,背光源照射白点外区域,白点现象无变化;照射白点区域,白点现象消失。从中不难看出,不良受彩膜基板黑矩阵下TFT基板上有源层光照导电性能的影响。将白点消失样品进行高温存储,白点均复现。从该实验可以看出,白点区域有源层受Staebler-Wronski效应影响,改变有源层的导电性,ΔVp发生变化又得到了还原,使白点在光照下消失,在高温下复现。

Staebler-Wronski效应现象为a-Si∶H在可见光持续照射下,暗电导率和光电导率会随时间的增加而下降,在150 ℃以上的温度下退火可恢复。采用电子自旋共振进行测试,发现在光照情况下,a-Si∶H中的悬挂键(Dangling Bond,DB)信号强度增加。针对非掺杂的a-Si∶H,导带的电子迁移率比空穴电子迁移率大得多,电流主要通过电子传输形成。随着光照的进行,DB密度逐渐增加,靠近费米能级的深能级和其态密度均增加,导带内跃迁电子的寿命减少,导致光导率减小。在a-Si∶H中,光的电导率与迁移率和载流子寿命的乘积成正比,光的照射对迁移率的影响非常小,因此载流子寿命的减少是光电导率降低的主要原因。另外,在光照射下,跃迁的带间距内态密度增加。在光照射前,跃迁带间距中央靠近导带侧的费米能级向价带方向移动,所需的活化能增加,因此暗电导率也减少。

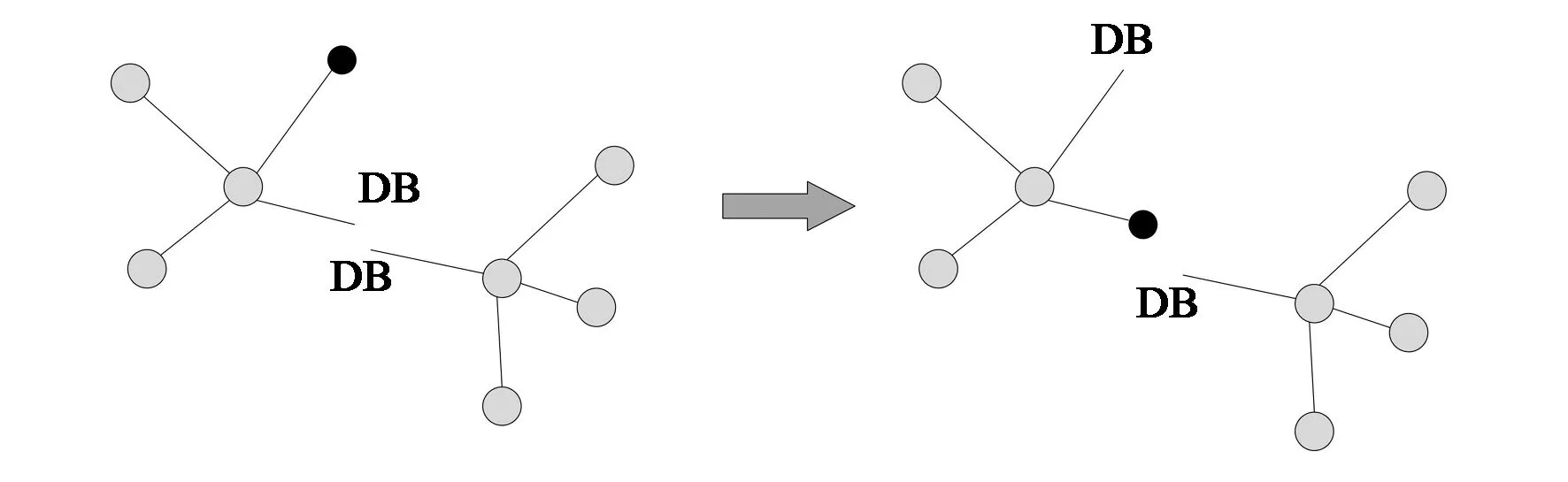

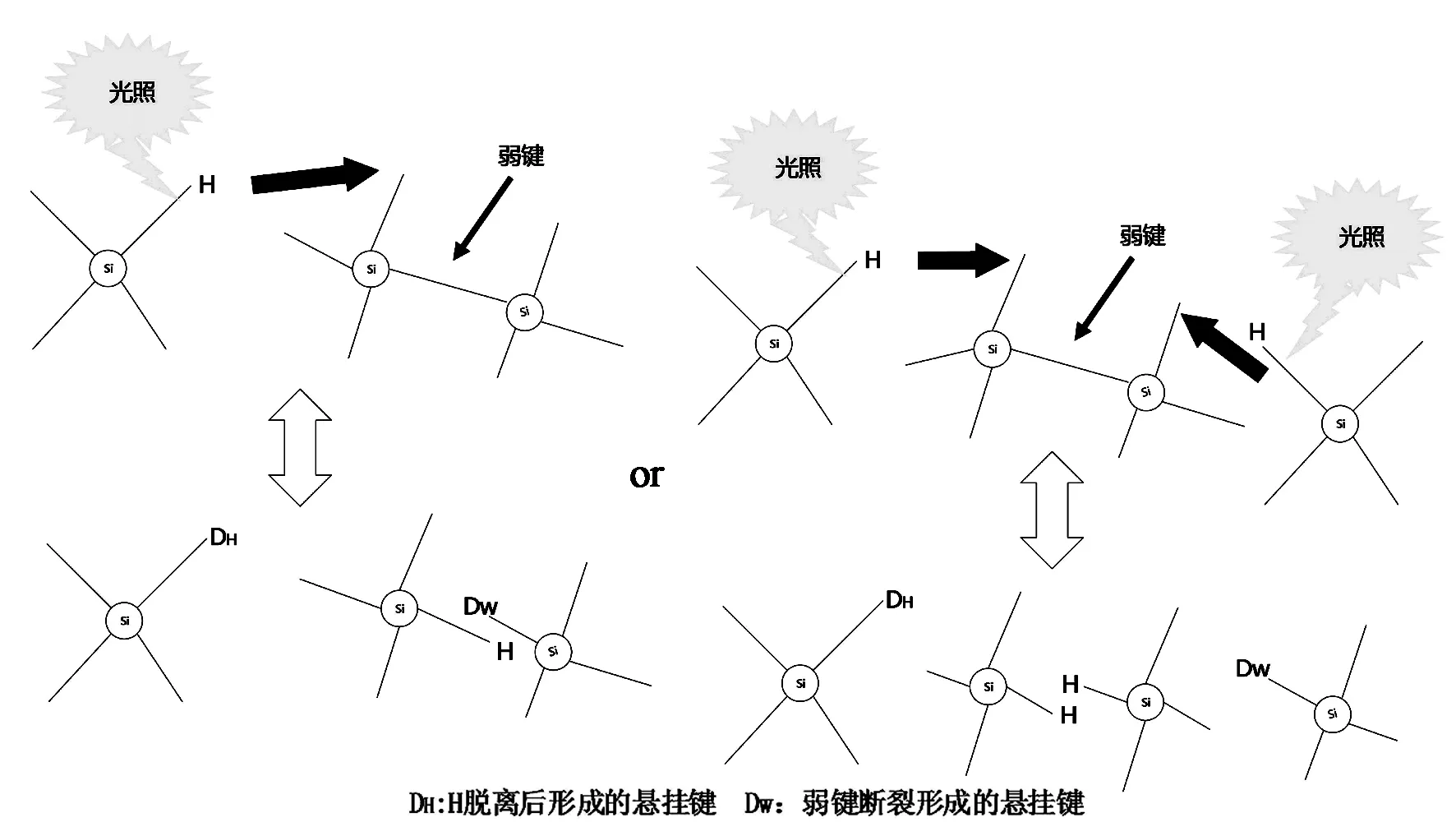

对于Staebler-Wronski效应产生的机理,国内外主要有3种解释模型。一是弱键断裂模型(图2),其机理为Si—Si弱键中的Si原子存在一个Si—H键,当两个载流子在弱Si—Si键附近复合时,其中部分能量以声子的非辐射方式释放出来,使膜中的Si—Si弱键断裂,形成两个临时悬挂键,为了达到更稳定的亚稳状态,邻近原子会在小范围内发生重构,其中一个Si原子的Si—H转向悬挂处,从而增加了悬挂键缺陷态密度[8]。二是“氢玻璃”模型(图3),在光照下,H从Si—H键中脱离出来并在a-Si∶H中移动,这种移动的H造成了弱Si—Si的热力学断裂,从而形成两个悬挂键缺陷,增加了悬挂键缺陷态密度[9-10]。三是氢碰撞模型(图4),光照射下,诱导Si—H键断开,形成1个悬挂键和1个可移动的H原子,当两个可自由移动的H原子在运动过程中在弱Si—Si键附近发生碰撞时,弱的Si—Si键断裂,形成了亚稳的不可移动的化合物(Si—H)2,增加了2个悬挂键,因此造成了H的聚集和悬挂键的增多,导致悬挂键缺陷态密度增加[11]。

图2 弱键断裂模型中 Staebler-Wronski效应微观机理Fig.2 Microscopic mechanism of the SW effect in SJT model

图3 “H 玻璃”模型中悬挂键形成示意图Fig.3 Schematic illustration of dangling bond formation corresponding to H-glass model

图4 氢碰撞模型示意图Fig.4 Schematic illustration of hydrogen collision model

3.3 栅/源极电容和存储电容对白点不良的影响

通过实验研究,白点是由于该区域的ΔVp与邻近区域差异导致,结合ΔVp的计算公式:

(3)

对于扫描信号确定的产品,ΔVp主要受到TFT基板各耦合电容、液晶电容及存储电容的影响,其中栅/源极耦合电容的影响较大。本文主要研究了栅/源极电容和存储电容对白点不良的影响。

3.3.1 栅/源极电容对白点不良的影响

栅/源极电容为TFT开关舌头处源极与栅极的耦合产生,对于四道和五道掩膜版,如图5所示,主要区别为数据线下方是否存在有源层,结合平行板电容公式:

(4)

图5 信号线下有无半导体截面图Fig.5 Sectional view of the data line with/without amorphous silicon layer

其大小主要受到源极宽度和栅绝缘层厚度影响,源极宽度体现为数据线侧边保留的有源层,即硅边。本文主要研究了不同的硅边宽度对白点的影响,其结果如表4所示。

表4 硅边宽度与白点现象的关系Tab.4 White dot phenomenon vs. active tail width

从表4可以看出,随着硅边的减小,由于数据线与扫描线的交叠面积减小,使栅极和源极耦合电容减小,白点逐渐减轻,如果有源层和数据层采用两道掩膜版,即无硅边,可以完全消除白点不良,但采用两道掩膜版,将增加开发成本,减少工厂产能。因此,兼顾经济效益,选择方案为有源层和数据线采用一道掩膜版,降低硅边宽度,硅边宽度受限于工艺,会存在一个极限值。在本实验中,硅边为1.2 μm时,白点基本不可见,品质可接受。

3.3.2 存储电容对白点的影响

像素存储电容受像素和公共电极的交叠面积、两者之间距离的影响,本文探究了不同钝化层厚度对白点不良的影响。

从表5可得,随着钝化层厚度降低,像素和公共电极距离减小,存储电容逐渐增大,ΔVp减小,白点不良程度逐渐减轻,但无法解决白点不良,存储电容提升会增加充电相关的问题,对于高端产品不太建议采用。因此,对于白点不良,建议仍然采用钝化层 600 nm。

表5 钝化层膜厚与白点现象的关系Tab.5 White dot phenomenon vs. PVX thickness

4 结 论

白点不良的产生,与有源层膜质和ΔVp存在直接关联性。白点区域有源层膜质与其他区域存在导电差异(这种差异性是由设备原因导致,目前还无法从设备方面消除),导致ΔVp有差异。通过持续光照白点消失实验和高温老化白点复现实验,直接证明了白点的消失是由于有源层在背光源照射下发生了Staebler-Wronski效应,电导率降低,减小了导电差异性,从而证明了白点产生的原因是有源层不同区域膜质与ΔVp的差异性。工艺上通过调整硅边宽度和钝化层厚度,来减小ΔVp值,改善白点不良。硅边宽度由2.0降低到1.2 μm可以解决白点不良。本研究成果对产品的效益提升及Staebler-Wronski效应的现象提供了重要的指导作用。