基于光纤传输的PCI Express总线延长方法与实现*

2021-03-20付文彬郭元兴孟珞珈

杨 光,付文彬,郭元兴,孟珞珈

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

PCI Express(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,采用点对点通信模式,双向数据传输,可以为每一个终端设备分配独享的通道[1]。它具有带宽高、速率快、串扰低和扩展性强等特点,广泛应用于计算机、服务器和其他通信设备[2]。正是由于PCI Express 总线具有很高的传输速率,因此对传输介质要求很高,导致其传输距离很短。

目前,PCI Express 总线的大部分应用环境为设备内部的互联总线,距离需求较短。但是,在一些特殊环境需要两个设备之间通过PCI Express 总线进行高速互联通信时,需要实现远距离传输。针对这种使用环境,PCI-SIG 组织专门制定了PCI Express 总线外部线缆连接使用规范,制定了延长PCI Express 总线的接口定义、接口形态、信号特征和上电时序等。为了实现PCI Express 总线的远距离传输,目前主要的手段是采用铜缆作为PCI Express总线的传输介质,同时在信号发送端采用中继芯片增强驱动能力,从而实现PCI Express 总线的远距离传输。该传输方式信号衰减严重,传输距离有限,目前最长达到15 m。此外,它采用铜缆,自身较重,不利于使用环境的搭建。

本文设计并实现了一种基于光纤传输的PCI Express总线延长方法,利用光纤介质信号传输质量高、传输距离远以及重量轻等优势,实现了PCI Express总线的远距离传输,同时搭建测试环境对该方法实现的功能和性能进行了测试,满足规范要求。

1 原理分析

通过PCI Express 总线外部线缆连接使用规范可知[3],PCI Express 总线信号包含高速差分信号和辅助信号。高速差分信号的传输速率为2.5 Gb/s(GEN 1)、5 Gb/s(GEN 2)和8 Gb/s(GEN 3),因此高速差分信号可采用10 Gb/s 的光电转换模块进行传输。辅助信号主要包括CREFCLK、CPERST#、CPRSNT#、CPWRON 和CWAKE# 信号。其中,CREFCLK 为100 MHz 的差分参考时钟,可在下游端采用晶振产生;其余信号均为低速的单端信号,可在PCI Express 总线下游链路端根据时序要求进行相关设置。

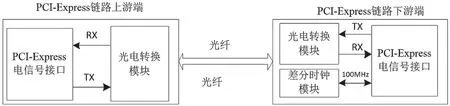

图1 为PCI Express 高速总线光纤延长方法示意图。在PCI Express 总线链路上游端,采用光电转换模块将PCI Express 总线发送端的电信号转换为光信号,经光纤传输至链路下游端,再由下游端的光电转换模块将光信号还原成电信号。反之,PCIExpress 链路下游发送端的电信号经光电转换模块转换为光信号后,再经光纤传输至上游端光电转换模块还原成电信号。

图1 PCI Express 总线光纤延长示意

根据PCI Express 总线协议[4],系统复位时,PCI Express 总线上的设备需要完成链路训练,实现物理层、数据收发模块和链路相关状态的初始化。只有正确完成链路训练,PCI Express 总线两端的设备才能进行数据交互。PCI Express 总线的链路训练由LTSSM(Link Training and Status State Machine)状态机控制。LTSSM 状态机分为“Detect”“Polling”“Configuration”“Recovery”“L0”“L0s”、“L1”“L2”“Disabled”“Loopback”和“Hot Reset”共11个状态。正常的链路训练路径如图2所示。

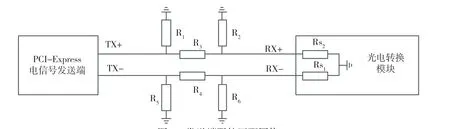

PCI Express 总线的物理层在进行复位后,LTSSM 首先进入“Detect”状态,通过Receiver Detect 识别逻辑检测链路的接收端,判断接收端是否可以正常工作。只有检测到接收端是合法的设备后,才能跳入“Polling”状态。在Polling 状态和Configuration 完成通道资源检测和寄存器配置后,跳入L0 正常工作状态进行数据收发。其中,Receiver Detect 识别逻辑是通过检测接收端的DC 共模输入阻抗来判断接收端是否合法[5]。如果接收端的DC 共模输入阻抗在40~60 Ω 内,则认为接收端工作正常。对于光电转换模块,它的输入阻抗并不在40~60 Ω 内,因此需要对PCI Express 链路中发送端的阻抗进行匹配,才能通过链路训练时的“Detect”状态检测。阻抗匹配电路如图3 所示,其中R1~R6为阻抗匹配网络,Rs1和Rs2为光电转换模块的输入阻抗。不同光模块输入阻抗不同,可通过调节R1~R6阻值将输入阻抗调至40~60 Ω内。

图3 发送端阻抗匹配网络

在PCI Express 总线链路训练过程中,还有一种“Electrical Idle”低功耗休眠状态。通常情况下,PCI Express 总线接收端需要收到EIOS 序列后才进行低功耗状态。但是,有时接收端在没有收到EIOS序列的情况下,若发现空闲状态检测电压阈值小于75 mV[5],也可以进入低功耗状态。因此,在链路训练时,因线路的抖动和不当的偏差,可能导致PCI Express 总线进行错误的低功耗状态判断。因此,硬件设计时需要防止电路产生抖动和偏差。

2 硬件设计

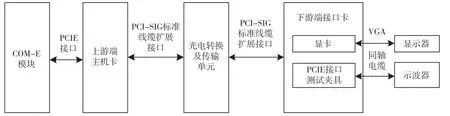

PCI Express 总线延长方法硬件总体设计如图4所示,分为上游端主机卡、光电转换及传输单元和下游端接口卡3 部分。其中,上游端主机卡用于将PCI Express 总线转换为外部线缆,连接使用规范中规定的标准接口;光电转换及传输单元主要用于PCI Express 总线的光电转换和光信号的传输;下游端接口卡主要实现将延长后的PCI Express 总线信号还原为标准接口。

2.1 上游端主机卡硬件设计

上游端主机卡主要由PCI Express 总线输入接口、电源模块、PCI Express 总线控制芯片、MCU和PCI-SIG 标准线缆扩展接口组成。PCI Express总线输入接口设计为通用的金手指接口,可插入通用的PCI Express 总线插槽。电源模块主要为上游端主机卡供电,由金手指接口输入12 V 和3.3 V电压,经电源模块PTH0808WAD、PME5218 和TPS74401 转换为5 V、2.5 V 和1.0 V 电压,以供电路板工作。PCI Express 总线控制芯片主要用于提高PCI Express 总线信号质量,防止出现抖动和偏差,导致链路训练时进行错误的“Electrical Idle”状态判断。本设计中PCI Express 总线控制芯片采用89H24NT6AG2ZCHLGI。该芯片为24-Lane 的交换芯片,严格遵循PCI Express 总线协议,在接口信号上具有去预重、接收均衡和驱动强等特点,可有效提升PCI Express 总线电信号信号传输质量。MCU 采用C8051F320,通过IIC 总线对89H24NT6AG2ZCHLGI 进行相关功能的配置。PCISIG 标准线缆扩展接口采用Molex 公司的75586-0104 和74540-0401,且接口定义与规范保持一致。

2.2 光电转换及传输单元

光电转换及传输单元主要由PCI-SIG 标准线缆扩展接口、阻抗匹配网络、光电转换模块和光纤组成。PCI-SIG 标准线缆扩展接口与上游端主机卡设计相同。阻抗匹配网络可根据第1 章节的方法进行设计。光电转换模块采用10 Gb/s 光电转换模块进行传输,满足光纤与光模块配套即可。设计中采用Samtec 公司的PCIEO-4G3-030.0 高速光纤线缆组件,将PCI-SIG 标准线缆扩展接口、阻抗匹配网络、光电转换模块和光纤进行高度集成,方便用户设计。该组件集成的光纤长度为30 m,传输速率满足GEN 1 和GEN 2。PCIEO-4G3-030.0 高速光纤线缆组件两端分别为host 端口和target 端,其中host端口接上游端口,target 端接下游端口。

2.3 下游端接口卡硬件设计

下游端接口卡主要由PCI-SIG 标准线缆扩展接口、电源模块、PCI Express 总线控制芯片、MCU、时钟Buffer 和标准PCI-Express 总线接口组成。其中,PCI-SIG 标准线缆扩展接口、PCI Express 总线控制芯片和MCU 与上游端主机卡设计相同。电源模块由外部输入12 V 电压,通过MQ7250R2T、PME5218 和TPS74401 转换为电路所需的3.3 V、5 V 和1.0 V。时钟Buffer 采用6 输出差分缓冲器ICS9DB106BGILF进行时钟扩展,用于标准PCI Express 总线接口扩展。设计中采用89H24NT6AG2ZCHLGI 进行信号质量提升,同时利用其交换功能,将延长后的PCI Express总线扩展为4 路标准X4 接口。

硬件连接示意图如图5 所示,光电转换及传输单元的host 端口与上游端主机卡相连,光电转换及传输单元的target 端口与下游端接口卡相连。

3 测试验证

测试环境的搭建主要用于该方法功能和性能的验证,如图6 所示。测试环境由COM-E 计算机模块、上游端主机卡、光电转换及传输单元、下游端接口卡、PCI Express 接口测试夹具、显卡、电源和示波器组成。COM-E 计算机模块的PCI Express 总线经上游端主机卡、光电转换及传输单元和下游端接口卡延长后,通过接入的显卡可以测试PCI Express总线延长后的数据传输功能。通过接入PCI Express总线测试夹具,将信号传输至示波器,从而实现对PCI Express 总线延长后的接口性能测试。

图6 测试环境示意

从测试环境示意图分析可知,COM-E 计算机模块的VGA 显示接口并没有从COM-E 计算机模块主板引出,而是通过延长后的PCI Express 总线接入显卡扩展VGA 接口引出。COM-E 计算机模块上电后,如果显示器正常显示操作系统界面,则验证了PCI Express 总线经延长后扩展VGA 接口功能正常和数据传输能力正常。

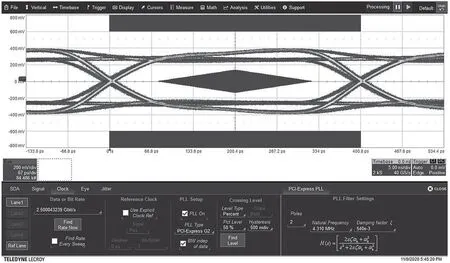

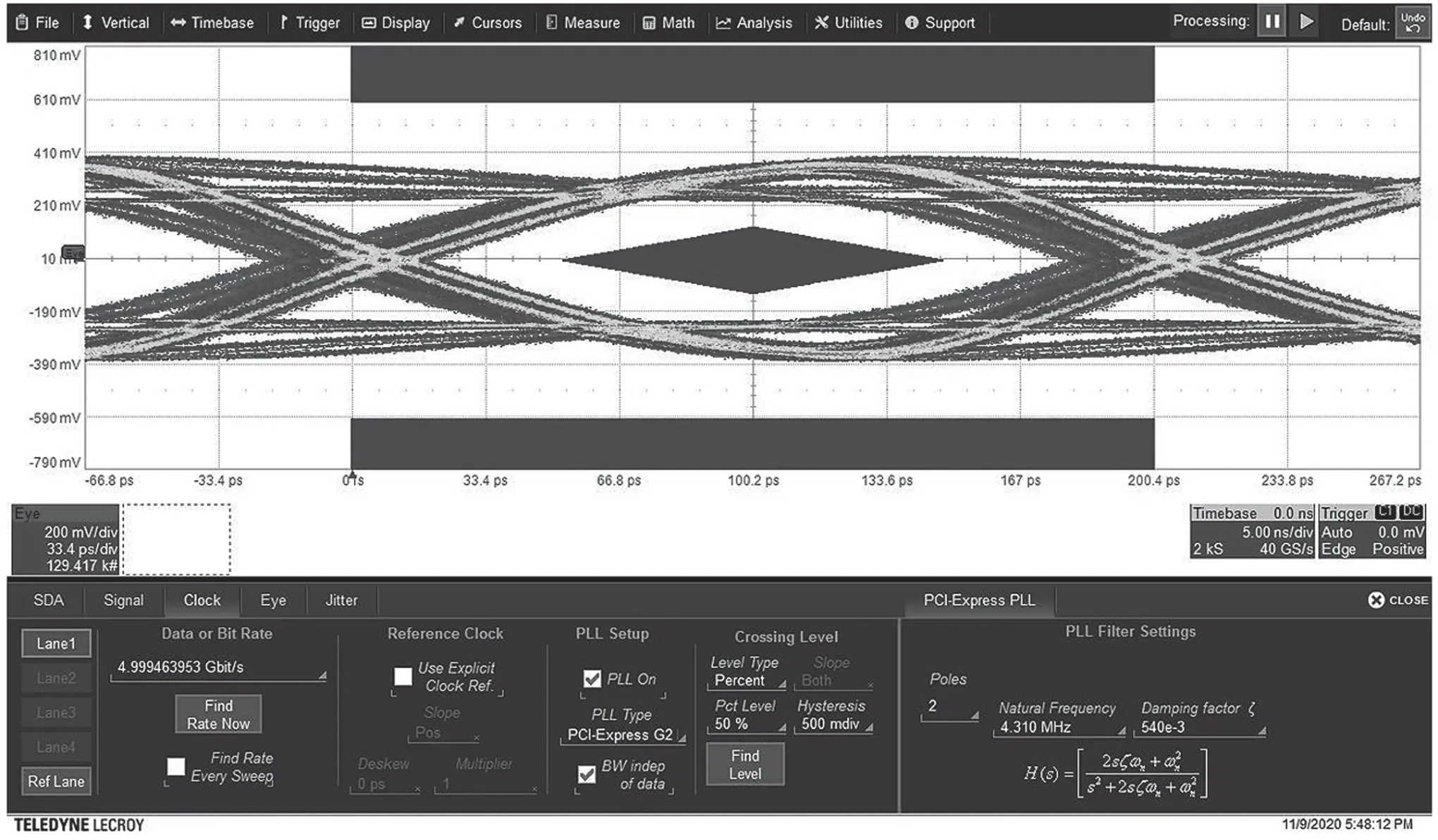

接口性能的测试是通过PCI Express 接口测试夹具将延长后的PCI Express 总线信号引入示波器进行信号质量的测试。示波器采用力科816Zi-B,自带PCI Express 总线测试模块,并根据PCI Express总线规范参数提供眼图模板。其中,一对差分对的测试结果如图7 和图8 所示。图7 为光纤30 m 延长后,速率为2.5 Gb/s 的眼图。从眼图中可以看出,占空比上下区域对称,眼睛张开,噪声和抖动都在正常范围内,眼图没有触碰深色的模板区域,信号质量良好。图8 为光纤30 m 延长后,速率为5 Gb/s的眼图。可以看出,眼图的噪声和抖动增大,但占空比区域任然对称,眼睛仍然处于张开状态,没有触碰深色的模板区域。信号质量仍在可接受范围,并不影响使用。

图7 光纤30 m 延长2.5 Gb/s 眼图

图8 光纤30 m 延长5 Gb/s 眼图

通过测试环境的验证可知,基于光纤传输的PCI Express 总线延长方法在通信功能和信号质量上都能满足两个设备之间的远距离通信需求,进一步验证了该方法的可行性和正确性。

4 结语

PCI Express 总线在计算机、通信以及航空航天等领域得到了广泛应用。因此,为实现PCI Express总线的远距离传输,提出了一种基于光纤传输的PCI Express 总线延长方法,结合原理分析进行硬件设计,并搭建测试环境验证了其功能和性能。结果显示,PCI Express 总线的光纤延长方法较传统的同轴电缆延长方法,具有传输距离远、信号质量高和重量轻等优势,可用于设备之间的远距离高速互联和计算机总线类接口的板卡试验测试等,具有很高的实用价值。