体Si和SOI工艺SRAM芯片电磁敏感度的温度效应

2021-03-15吴旭景王蒙军吴建飞李彬鸿郝宁高见头李宏张红丽

吴旭景 王蒙军 吴建飞 李彬鸿 郝宁 高见头 李宏 张红丽

(1. 河北工业大学电子信息工程学院,天津 300401;2. 天津先进技术研究院,天津 300450;3. 国防科技大学电子科学学院,长沙 410073;4. 中国科学院微电子研究所,北京 100029)

引 言

静态随机存储器(static random-access memory,SRAM)具有功耗低、速度快、无需实时刷新等优点,被广泛应用于各种处理器的高速缓存和片上系统. 随着信息技术的飞速发展,存储器市场占有率已超过集成电路(integrated circuit, IC)市场的一半. IC一直遵循着摩尔定律在发展,器件尺寸不断减小导致电路密度在不断的增加[1],存储器同样通过不断地减小尺寸和增加容量来提高集成度,这导致其电磁敏感度逐渐受到关注[2]. 对于绝缘体上硅(silicon on insulator, SOI)和体硅(silicon, Si)工艺的对比一直是研究的热点,体Si器件随集成度的增加,功耗以及可靠性受到极大的影响,而SOI由于独特的结构逐渐成为低功耗、高可靠性IC的主要技术[3]. 同时温度、湿度等环境因素同样会对器件的电磁兼容性能造成极大的影响[4-5],这使得客户对产品在复杂环境中的可靠性要求更加严格,因此对SOI和体Si工艺的器件在复杂环境中的可靠性研究及对比具有重要意义.

对于SOI和体Si工艺的对比以及复杂环境下IC的可靠性问题,国内外学者在不断地展开研究.两种工艺应用于电路时对于如阈值电压、工作频率等电学特性的研究相对较多[6-7],通过比较这些特征参数的变化也证实了SOI工艺相对体Si工艺在未来高频电路及大规模IC中具有一定优势. 基于SOI较体Si工艺一些特征参数上的优势,文献[8]通过比较相同带隙电路体Si和SOI工艺的敏感度特性,得出采用SOI工艺的测试芯片比采用体Si工艺的测试芯片具有更好的敏感度性能. 文献[9]根据汽车行业标准评估了CAN收发器电磁兼容性能,可以看出0.14 μm的SOI CMOS CAN收发器在不使用共模扼流圈的情况下,表现出优异的电磁发射 (electromagnetic emission, EME)和电磁干扰(electromagnetic interference, EMI)性能. 文献[10]评估了电离总剂量(total ionizing dose, TID)辐射和EMI的联合效应,结果表明嵌入式系统受TID辐射和EMI影响时的故障发生率明显高于其仅受EMI影响时的情况. 文献[11]对热应力下微控制器的抗扰度做了测试研究,发现温度的变化会导致微控制器抗扰度发生明显漂移. 对于不同工艺的电磁兼容性研究,普遍依照标准进行测试研究,很少考虑到环境因素;对于复杂环境下的电磁可靠性研究,都只针对一款芯片进行测试研究,测试结论对IC不具有普遍性. 既考虑环境因素又对不同工艺的IC进行敏感度研究的相关文章目前还没有.

结合以上不同工艺及复杂环境下芯片的可靠性研究,针对SRAM存储器,本文对不同工艺下温度效应对敏感度的影响进行了测试研究. 首先结合理论分析温度效应对器件的影响,并结合不同工艺的器件特性进行对比分析,然后对两款芯片热应力下的敏感度进行实测对比并对测试结果进行分析,最后依据理论分析及实测结果给出结论.本文研究对不同工艺的IC在复杂环境中的可靠性研究具有参考价值.

1 热应力下电磁敏感度分析

半导体通常由载流子迁移率(μ)、饱和漏电流(Ids)、器件阈值电压(Vth)等参数来表征器件性能,这些参数的变化量是衡量器件可靠性的重要依据. MOS器件作为典型的温度敏感器件,漏源电流、阈值电压和迁移率会随着温度的变化产生漂移[12]. 从式(1)到式(5)可以看出它们都是关于温度的函数.

式中:ɛox为二氧化硅的介电常数;tox为二氧化硅的厚度;W和L分别为沟道的宽度和长度;Vg为栅极电压;β为一个与制造工艺有关的常数;T为温度.

漏源电流的增加是电路失效的主要原因,漏源电流由沟道电流(信号电流)和结电流(漏电流)组成. 从式(1)、(2)容易看出迁移率和漏源电流都会随温度的升高而减小. 在−55 ℃到125 ℃范围内温度每变化100 ℃,迁移率会随之变化40%,这导致沟道电流也会成比例地随之变化. 结电流也会随温度的升高而增加,但在测试温度范围内沟道电流的变化占主导地位,所以漏源电流随温度的升高会呈现减小状态.

式中:φms为半导体之间的功函数,Qf为表面态电荷密度,这两项与温度无关;ɛs为介电常数;q为电子电荷;NA为衬底掺杂浓度;Cox为栅氧化层电容;φB为半导体两端电压;k为玻尔兹曼常数;ni为本征载流子浓度;Eg0为禁带宽度,可以看做常数.由式(3)、(4)、(5)可知,阈值电压(Vth)随温度的升高同样会降低,但变化较小,在测试温度范围内其变化通常不会超过200 mV,所以对Vg−Vth影响很小,因此这里主要考虑载流子迁移率的温度效应.

当外界EMI作用于MOS器件上时,器件工作状态下的栅极电压会受到EMI的作用发生如等式(6)所示的变化:

式中,Vrf表示外界EMI在MOS器件栅极引起的电压波动. 由式(1)和(6)整理可得EMI引起的饱和漏电流的变化量为

综上可知温度和EMI都会对MOS器件的漏源电流产生影响,而当温度应力和电磁应力同时作用于MOS器件时,随着温度的升高,载流子迁移率(μ)会随之减小,这使得在相同EMI的情况下,由式(7)可以得出漏电流的变化量ΔIds会相对较小,从而表现出温度越高MOS器件抗扰度越好的状态.

载流子迁移率作为温度效应下影响电磁敏感度的主要因素,使得SOI工艺和体Si工艺的SRAM芯片敏感度阈值漂移一致. 虽然在测试的温度范围内结电流和阈值电压随温度变化较小,但由于SOI工艺和体Si工艺的结构差异使得结电流和阈值电压随温度的变化量存在一定的差异,这可能是导致SOI和体Si工艺敏感度阈值漂移一致但SOI工艺SRAM芯片敏感度阈值漂移稍大于体Si工艺SRAM芯片的原因.

如图1、图2所示,SOI器件和体Si器件最明显的差别是:SOI器件存在隐埋氧化层,隐埋氧化层的存在既有如消除闩锁效应等优点也有像自热效应等缺点,由于体Si器件没有隐埋氧化层,所以体Si器件的漏电流会大于SOI器件;其次体Si器件结面积(S)包括四个侧面和一个底面,而SOI器件只有一个侧面,且体Si器件PN结之间的空间电荷区(V)明显大于SOI器件. 同时由式(5)可知随着温度的升高本征载流子浓度ni会随之增大,所以随着温度的升高SOI器件漏电流增量相对体Si工艺要小很多,漏源电流变化相对会较小. 这使得相同的温度变化量SOI器件抗扰度阈值偏移量要大于体Si器件. 对于阈值电压,上述已证明随温度的升高阈值电压会减小,但体Si器件阈值电压的减小是费米能级和空间电荷减小导致,SOI器件阈值电压的减小只是费米能级的降低,所以体Si器件的阈值电压随温度的变化要比SOI器件阈值电压随温度的变化大的多,这使得当热应力和EMI同时作用到器件时,SOI器件随着温度的升高漏源电流变化相对较小,从而表现出随温度的升高SOI器件敏感度降低会更多一些. 同时由于SOI器件存在隐埋氧化层,其热传导率较差,当温度升高时热效应会加剧,这同样可能是相同温度变化下SOI器件抗扰度阈值偏移量大于体Si器件的原因.

图1 体Si CMOS器件示意图Fig. 1 Bulk Si CMOS device profile

图2 SOI CMOS器件示意图Fig. 2 SOI CMOS device profile

2 热应力下敏感度测试

2.1 测试芯片及测试板

测试芯片为中国科学院微电子研究所提供的两款SRAM芯片,一个为0.5 μm的体Si工艺,另一个是0.35 μm 的SOI工艺,如图3和图4所示.

图3 体Si测试芯片Fig. 3 Bulk Si test Chip

图4 SOI测试芯片Fig. 4 SOI test Chip

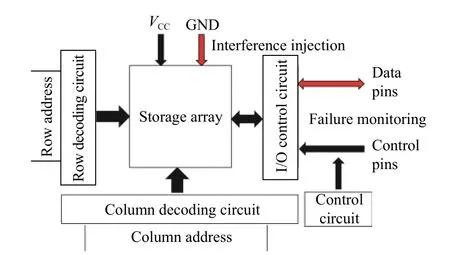

SRAM芯片为5±10% V电压供电,典型的电源工作电流为100 mA,存储容量为1 MB,军用工作温度范围为−55 ℃到+125 ℃. 一个完整的SRAM存储器由存储单元组成的存储阵列和外围电路构成. 为使干扰更好地耦合到SRAM芯片的存储阵列,我们依据IC电磁兼容(electro magnetic compatibility, EMC)测试规范选取了GND引脚作为待测引脚,如图5所示.

图5 SRAM功能结构图Fig. 5 SRAM functional structure diagram

依据测试标准IEC 62132-4[13],设计了保证芯片正常工作且符合测试要求的测试板,如图6所示.待测芯片在测试板的一侧,其他器件在测试板的另一侧. 为了保证两个芯片的测试电路一致,两种工艺的SRAM芯片通过锁紧座固定到测试板上.控制器为独立的一个模块,通过跳线的方式来控制存储器正常工作. 干扰通过SMA连接器和6.8 nF电容注入到待测引脚,同时采用磁珠和电感组成的无源网络确保干扰注入的质量.

图6 测试板正反面Fig. 6 The front and back of test board

2.2 测试平台及流程

依据IEC 62132-4直接功率注入法(direct power injection, DPI)测试标准,结合温箱和DPI的测试设备搭建热应力下IC传导抗扰度测试平台如图7所示. 热应力下的敏感度测试采用温箱为测试芯片提供相应的工作温度环境,将测试板放入温度可控的温箱内,设置温箱温度到预测值进行相应的DPI测试,干扰由信号发生器产生,通过功率放大器和定向耦合器将干扰注入到测试板上的SMA连接器,电源和控制器使芯片处于正常的工作状态. 为了保证测试板上所有器件在测试温度下可以正常工作,选取了−10 ℃、30 ℃、80 ℃三个温度进行热应力下的敏感度测试.

图7 热应力下敏感度测试平台Fig. 7 Sensitivity test platform under heat stress

由于测试过程中将整个测试板放入到温箱内,所以测试板上的无源器件都会直接暴露在测试设定的温度中,尤其对于干扰注入路径,其阻抗特性随温度变化的影响应该被考虑,文献[14]对100 MHz~2 GHz频率范围内不同温度下无源分布网络及无源器件的阻抗参数进行了测试对比,发现阻抗参数保持了很好的温度一致性. 同时证实了在100 MHz~3 GHz范围内,电源分布网络阻抗参数随温度变化产生的微弱漂移不会对敏感度的趋势造成明显改变,测试中可以忽略. 文献[15]直接测试分析了不同温度下干扰路径的阻抗参数变化,发现其阻抗参数随温度变化很小. 而与无源元件相比,温度对晶体管的影响相对更加明显[16]. 所以,可以认为温度对测试芯片的影响是导致灵敏度阈值漂移的主要原因.

两种工艺的SRAM芯片测试流程及参数设置保持一致,如图8所示.

图8 测试流程图Fig. 8 Test flow chart

测试频率(f)从10 MHz开始逐渐增加到1 GHz,10 MHz到100 MHz之间步进为10 MHz,100 MHz到1 GHz之间步进为100 MHz. 注入功率(P)的上限值设为37 dBm,功率达到限制仍未失效将对下一个频点进行测试. 芯片正常工作时示波器监测数据端口输出高电平为4.8095 V,低电平为0.03225 V.失效判据一般分模拟输出监测和状态输出监测,由于示波器最多只能监测四个数据端口,所以失效数据位可能不会被示波器监测到,且干扰注入后数据端口监测到的波形如图7所示,高低电平变为波动的干扰正弦波,随着EMI的增加高低电平逐渐变宽且抖动较大,所以这里采用状态输出监测. 失效状态主要以控制器监控软件的监测结果为主,即数据读取“1”“0”状态发生翻转视为失效. 失效时的逻辑高电平最低电压低于3 V,逻辑低电平的最高电压高于2 V. 故障点的正向功率值通过与正向功率计相连的软件读取. 为了防止温度骤变和长时间高低温下工作影响SRAM芯片的性能,在一个温度下对SRAM敏感度测试完成后,关掉温箱使SRAM芯片恢复5 h再进行下一个温度测试.

3 敏感度测试结果分析

对SOI工艺和体Si工艺两款SRAM芯片的相同引脚进行热应力下敏感度测试,图9为SOI工艺的SRAM芯片在不同温度下的敏感度曲线,图10为体Si工艺的SRAM芯片在不同温度下的敏感度曲线.

图9 热应力下SOI工艺SRAM芯片的敏感度曲线Fig. 9 Sensitivity curve of SRAM chip in SOI technology under heat stress

图10 热应力下体Si工艺SRAM芯片的敏感度曲线Fig. 10 Sensitivity curve of SRAM chip in bulk Si technology under heat stress

对于体Si工艺,随着温度的升高,可以看到敏感度有变好的趋势,在100 MHz之前敏感度阈值漂移相对不明显,80 ℃与−10 ℃敏感度阈值最大相差0.94 dBm,在100 MHz之后敏感度阈值漂移相对明显,尤其在700 MHz处80 ℃的敏感度阈值比−10 ℃的敏感度阈值高3.24 dBm. SOI工艺同样随着温度的升高,敏感度有变好的趋势,而且在100 MHz之后敏感度阈值漂移相对明显,在600 MHz处80 ℃的敏感度阈值比−10 ℃的敏感度阈值高3.81 dBm.不同工艺的SRAM在温度效应下敏感度阈值漂移情况一致,温度升高载流子迁移率减小,降低了EMI引起的漏电流波动,削弱了EMI的作用,使得芯片的敏感度阈值发生漂移,表现出更好的电磁抗扰能力.

从图9可以发现,SOI工艺在20 MHz之前敏感度阈值在温度从−10 ℃上升到80 ℃时有不到1 dBm的下降趋势,与前面提到的结论相反,而体Si工艺没有出现类似情况. 这是因为SOI工艺本身的浮体效应[17]所导致,温度的升高加强了漏端载流子的碰撞电离,导致栅极导通电压降低,漏端输出电流随之增加. 在低于20 MHz时出现此现象是因为在20 MHz之前的低频EMI会在CMOS即使断开的状态下通过,而高频EMI则是通过本征电容耦合到输出端,随着干扰的增加漏电压达到一定值时浮体效应发生,这就掩盖了高温下载流子迁移率减小所导致的漏电流减小的情况,表现出温度越高敏感度阈值随之降低的现象.

为了进一步比较热应力对两款不同工艺的SRAM芯片敏感度阈值的影响程度,选取了两种工艺的SRAM芯片−10 ℃和30 ℃下敏感度阈值差以及−10 ℃和80 ℃下敏感度阈值差进行对比,由于两款芯片100 MHz之后随温度的变化敏感度漂移相对明显,所以对两款芯片100 MHz~1 GHz频段内的高低温敏感度阈值差进行比较,如图11和图12所示.

SOI工艺和体Si工艺SRAM芯片高低温敏感度阈值差对比发现,SOI工艺的SRAM芯片相对体Si工艺的SRAM芯片随温度变化敏感度阈值漂移更明显一些:温度从−10 ℃到30 ℃ SOI工艺SRAM芯片敏感度漂移量比体Si工艺SRAM芯片普遍多0.5 dBm,在500 MHz处差值最多达到0.83 dBm;当温度从−10 ℃到80 ℃时,SOI工艺的SRAM芯片敏感度偏移量比体Si工艺的SRAM芯片普遍多1 dBm;在600 MHz处差值达到最大2.96 dBm.可以看出,SOI工艺和体Si工艺的SRAM芯片在相同温度的工作环境下,随着环境温度的升高,SOI工艺的SRAM芯片抗扰度提升幅度大于体Si工艺的SRAM芯片.

图11 两款SRAM芯片−10 ℃和30 ℃敏感度阈值差Fig. 11 Sensitivity threshold difference of two SRAM chips at−10 ℃ and 30 ℃

图12 两款SRAM芯片−10 ℃和80 ℃敏感度阈值差Fig. 12 Sensitivity threshold difference of two SRAM chips at−10 ℃ and 80 ℃

4 结 论

针对复杂环境中SOI和体Si工艺IC的可靠性问题,本文研究了两种工艺的SRAM芯片在温度和EMI共同作用下的可靠性. 通过对SRAM芯片GND引脚敏感度实验研究可以发现:100 MHz之前,两款工艺敏感度阈值随温度的升高几乎没有变化;100 MHz之后,SOI工艺SRAM芯片在温度每升高40 ℃时敏感度阈值最大增加达到3.02 dBm,体Si工艺SRAM芯片在温度每升高40 ℃时敏感度阈值最大增加达到2.35 dBm. 这主要是由于温度的升高会导致MOS管的载流子迁移率减小,正好削弱了EMI的作用. 同时测试结果表明在100 MHz之后SOI工艺的SRAM芯片随温度每升高40 ℃敏感度阈值偏移量普遍比体Si工艺的SRAM芯片多0.5 dBm. 这主要是由于SOI工艺器件的结面积、空间电荷区体,以及存在隐埋氧化层等结构导致相同的温度变化漏源电流变化相对体Si工艺器件更明显,从而表现出随着温度升高敏感度阈值漂移更明显的现象. 所以无论SOI工艺还是体Si工艺,在SRAM芯片GND模块1 GHz以下的敏感度测试中应该充分考虑其实际工作环境,综合测试才能更好地预估被测芯片的可靠性. 同时证明了就SRAM GND模块SOI工艺相对体Si工艺在电磁和高温混合环境下具有一定的优势,且温度越高电磁敏感度方面优势越明显. 对两种工艺进行热应力下敏感度测试对比,为SOI工艺与体Si工艺在高温和电磁混合环境下的可靠性研究提供参考.

针对标准IEC 62132-4测试不考虑环境温度的问题,在此基础上增加环境温度因素进行了敏感度测试研究,同时对两种工艺的SRAM芯片进行对比研究,使测试结果适用于更多的IC. 未来将对数据、地址、控制引脚所对应的模块展开进一步的研究.