航电系统综合核心处理机容错设计

2021-02-28何立军王梦凡王生宵秦琪周广飞

何立军 王梦凡 王生宵 秦琪 周广飞

摘要:综合化核心处理机作为综合模块化航空电子系统控制和管理的核心,对于实现航空电子系统的功能、性能起着决定性的作用。介绍了一种基于冗余技术的综合核心处理机容错设计,从供电容错、网络容错、模块容错设计等进行介绍,对产品可靠性进行分析,结果表明冗余设计能够明显提高产品任务可靠性。

关键词:综合核心处理机;容错;冗余;可靠性

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2021)35-0115-03

Fault-Tolerant Design of Integrated Core Processor for the Avionics Systems

HE Li-jun, WANG Meng-fan, WANG Sheng-xiao, QIN Qi, ZHOU Guang-fei

(Xi’an Aeronautics Computing Technique Research Institute of AVIC, Xi'an 710065, China)

Abstract: Integrated Core Processor is the control and management center of Integrated Modular Avionics System. It is crucial for the implementation of Avionics System functions and performances. A fault-tolerant ICP design, based on redundant technology, is presented as in Power Supply Fault-tolerant, Network Fault-tolerant and Module Fault-tolerant, as well as its reliability analysis, Thus Mission Reliability has been improved remarkably after a redundant product design.

Key words: integrated core processor; fault-tolerant; redundant; reliability

新一代航空电子系统是一种综合化、模块化的机载分布式系统,综合核心处理机是新一代航空电子系统的核心,它承担着大量飞行任务的执行、控制和飞机安全性保障等工作,核心处理平台的可靠运行对于实现航空电子系统的功能、性能起着决定性的作用。容错技术是提高可靠性的有效方法,机载系统常采用余度设计,利用多余资源来换取系统可靠性的提高。该方法可有效提高机载产品的可靠性和安全性,实现产品一次故障工作,二次故障安全等要求。

本文首先介绍了某综合核心处理机系统组成,接着分析了该核心处理机供电、网络、系统管理、数据处理等方面所采用的余度容错技术,为机载电子设备容错设计提供可参考的依据。

1 系统设计

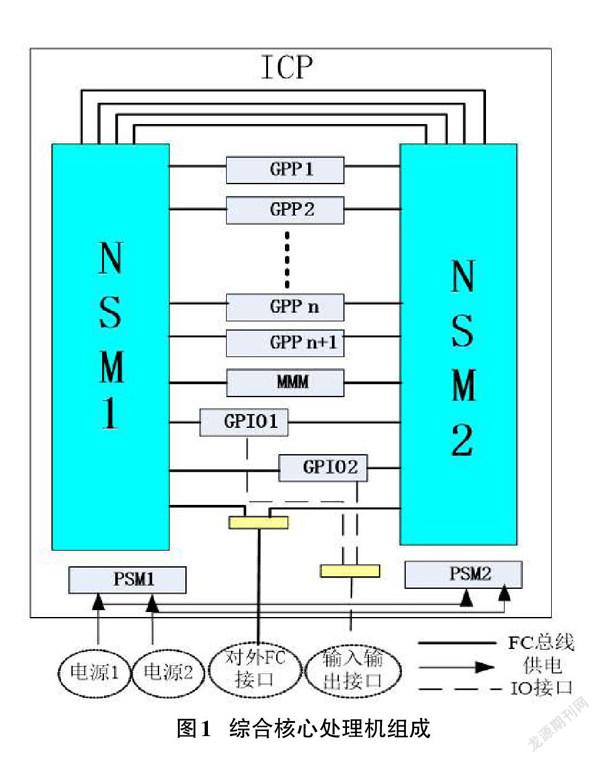

综合核心处理机ICP作为航空电子系统的管理和处理中心,承担了系统管理、传感器管理和数据融合、雷达数字功能处理、电子战数字脉冲功能处理、通信导航识别数字功能处理、红外搜索跟踪、分布式孔径、数字地图处理、战场态势处理、图像处理、显示控制和管理处理、音频处理、数据管理、健康管理等多个任务。某综合核心处理机采用符合ASAAC标准的LRM模块,基于高性能数据处理和统一高速网络技术,设计了一种FC交换网络的综合核心处理机系统,如图1所示。

ICP内部包括5种标准LRM:通用处理模块(GPP)、通用处理及IO模块(GPIO)、大容量存储模块(MMM)、网络交换模块(NSM)、电源模块(PSM)。GPP、MMM、GPIO的FC接口连接到NSM上,从而實现各LRM间通过FC交换网络完成数据通信。

2 容错设计

综合核心处理机具有综合化、模块化、软件化、网络化等多种特征,在结构上进行了高密度集成的一个实时的容错的分布式的机群。核心处理机在综合化航空电子系统中居于核心位置,是整个综合航电的“大脑”和“神经”。在系统设计过程中采用热备份、温备份、冷备份等技术,使系统具有完备的容错、重构和冗余控制能力,能够承担安全级别为生存关键和任务关键的相关航电任务功能。

2.1 电源容错

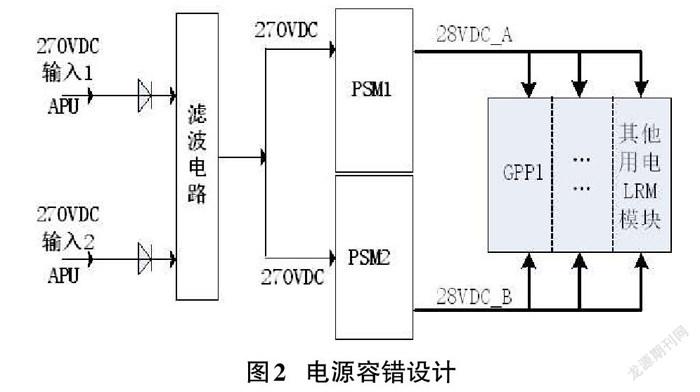

电源容错设计如图2所示。ICP内部配置2块PSM,按照并联方式为其他所有用电LRM进行供电。

飞机通过2根270VDC电源汇流条向ICP提供270VDC电源,2路270VDC输入电源并联后,经过同一套滤波电路后分别向2块PSM模块提供270VDC。当飞机供电系统出现1路270VDC供电故障时,另一路供电输入可以支持ICP保持全状态工作;当出现2路270VDC供电故障时,由APU为ICP提供输入电源,此时ICP按照系统配置为部分LRM提供电源,ICP降级工作。

2块PSM模块采用1+1余度供电设计,一旦某一电源发生故障,另一电源能独立承担对所有LRM模块供电的能力。用电LRM模块设计为2路并联输入,无论是由于某路外部供电故障或是LRM供电输入端故障,均可确保模块正常工作。

PSM模块除了完成功率转换外,还具有智能管理和开关矩阵控制处理能力,能够对供电输入、输出等进行检测诊断,能够基于监控到的信息控制电源开关矩阵,及时对由于用电模块发生类似短路故障造成输出监测异常的接口进行关闭,提高故障隔离性,以确保系统在任何情况下的正常工作。

2.2 网络容错

对于FC交换网络,应用中网络可能出现的故障有NSM模块故障、NSM模块某交换端口故障、LRM模块FC节点故障等几种主要故障模式。ICP中FC网络架构在应用层提供一定的余度容错能力,能够有效地避免出现某种故障时,ICP不降级或完成关键任务。网络架构详见图1。

ICP中共设计2个NSM,级联后组成更大规模交换网络。FC网络架构中,ICP与外部雷达、电子战、CNI等子系统之间的数据通道均在应用级提供备份FC接口;在ICP内部,所有LRM模块对外均包含2路FC节点接口,同时连接到2个NSM模块。当网络出现某种故障(或网络接口或交换机或通信电缆)时,网络数据可通过另一路FC接口进行通信。当链路中2个网络接口设计为备份工作模式,故障时ICP可正常工作;当链路中2个网络接口设计为同时使用,故障时ICP可使用1路接口降级工作,完成关键任务执行。

2.3 模块容错

模块级容错主要通过各个主要功能模块的冗余备份及系统容错重构管理软件来实现。

ICP中的通用处理模块(GPP)主要承担ICP中的数据处理与部分信号处理功能,用于完成ICP中雷达数据处理、电子战信号处理与数据处理、光电控制与目标解算等任务。GPP模块设计为n+1备份工作模式,提供热备份、温备份、冷备份方式,GPP模块可预先驻留所有功能模块程序,当某一功能模块失效,通过系统配置预案方式用备份的GPP模块代替故障失效模块或动态地在处理器资源使用率较低的模块上分配执行。

ICP中的通用处理及输入输出模块(GPIO)主要承担PHM、火控解算等任务,以及ICP的系统控制与管理功能。ICP是一个多处理机、多任务系统,所有任务将在系统控制器的统一控制与管理下协同工作。系统控制器任务由GPIO承担。ICP中一共有2块GPIO,它们工作在1+1热备份方式下。在初始化时竞争控制权,没有竞争上的GPIO模块作为主控制器的热备份,在运行过程中系统的主控制器发生故障时,系统自动切换到备份模块。2块GPIO模块之间设计2路用于控制器抢权的离散量接口,1路为输出离散量,1路为输入离散量,如图3所示,输出离散量用来表示自己是否取得系统控制权,当输出为1时表示取得控制权,输出为0时表示未取得。系统控制器抢权过程如下:

1)系统识别到该模块为GPIO1时,设置为系统控制器,输出离散量设置为“1”;

2) GPIO2模块检测到输入为“1”时,设置自身输出离散量为“0”,作为备份模块;

3) 如系统控制器GPIO1发生故障,输出离散量状态由“1”变为“0”;

4) GPIO2监测到输入为“0”时,判断系统控制器故障,设置自身输出离散量为“1”,GPIO2负责实现ICP主控制器相关功能。

GPIO模块除完成相应的计算处理功能外,还负责对外IO接口,互为备份的2块GPIO模块,它们都能访问外部I/O接口,但系统控制器在数据处理、接收控制指令、系统控制等方面起着决定性的作用;备份模块执行诊断和监视系统控制器工作状态的好坏,通过查询运行中的系统控制器的工作状态,可接收外部输入进行处理,同系统控制器执行同样的处理、操作,但不执行输出控制,不进行系统控制。备控模块能够实时保存最新的系统控制数据,以便在主/备模式切换时保证系统工作的无缝连接。IO功能接口设计如图4所示,对于外部输入信号,同时输入到2块GPIO模块中,进行同样的处理,对于输出信号,2块GPIO模块输出接口并联后输出到外部接口,但使用抢权输出离散量作为使能控制信号,仅作为系统控制器的GPIO模块可以输出,备份模块禁止输出,这样控制逻辑保证一个时刻只有一个通道对外打开,提高系统工作的稳定性,避免两个处理器竞争抢占外部接口共同控制的情形。

3 可靠性分析

综合核心处理机按照系统架构设计,主要由特定的LRM模块完成相应的计算处理功能,来实现整个系统任务的运行,为了便于分析通过容错设计后的架构对整个系统任务可靠性的提高,这里简化相应模型进行计算,假设系统共需要GPP模块5块,所有模块失效率都相同为λ。

在沒有冗余备份,按照综合核心处理机功能设计需要完成系统功能任务的情况下,需要NSM模块1块,GPIO模块1块,GPP模块5块,MMM模块1块,综合核心处理机任务可靠性模型如图5所示。

在进行容错设计后,综合核心处理机任务可靠性模型如图6所示。

对于串联系统,其对应的系统可靠性数学模型和平均无故障时间见公式(1)和(2)。

[RS=e-i=1nλit] (1)

MTBF = [0∞tf(t)dt] =[1i-1Nλi] (2)

对于并联系统,其对应系统可靠性数学模型见公式(3),当所有模块失效率相同时,系统的平均无故障时间见公式(4)。

[RS=1-i=1N1-Rit] (3)

MTBF = [1λi=1N1i] (4)

由公式可知,无容错设计的综合核心处理机其平均无故障时间为:

MTBF = [19λ] = 0.11[1λ]

增加容错设计后,对于双余度设计,其余度失效率为[23λ],对于GPP模块5+1备份设计,其余度失效率为[1130λ],所以综合核心处理机平均无故障时间为:

MTBF = [123λ+23λ+23λ+1130λ+λ] = [30101λ] = 0.297[1λ]

由此可见,综合核心处理机在采用余度容错设计后,产品可靠性得到了较大提高。

4 结论

基于冗余技术,设计了一种具有一定容错设计的综合核心处理机方案,大幅度地提高了系统任务可靠性,该方法可广泛应用于机载电子设备,使机载电子设备适应高可靠性的作战要求。但是,现代化战斗机的发展背景下,机载电子设备越来越朝着集成化、小型化方向发展,冗余设计必然带来设备的结构尺寸、重量、费效比等方面的压力;因此毫无节制的设计冗余显然是现代化机载电子设备所不能承受的。综合考虑结构尺寸、重量、经费、功耗、软硬件配制,考虑各种约束条件,综合多层次冗余方式的权衡是现代化机载电子设备的重要容错设计思路。

参考文献:

[1] 周涛.航空电子系统的可靠性分析[J].科技创新导报,2016,13(7):19-22,80.

[2] 王永国,邓道杰,於二军,等.机载机电系统双余度管理技术研究[J].航空计算技术,2019,49(3):95-98,102.

[3] 赵刚,谭伟.以冗余为中心的航电设备可靠性设计[J].电子技术,2018,47(6):81-83.

【通联编辑:梁书】