基于DSP和FPGA的CANFD通信实现

2021-02-18孙乐羊

杨 波,韩 杰,孙乐羊

(北京航天时代光电科技有限公司,北京 100094)

0 引言

控制器局域网(Controller Area Network,CAN)为德国Bosch公司20世纪80年代开发的一种串行数据通信协议,最初是为了解决汽车中大量控制与测试仪器之间的数据交换,由于其接口通信简单实用、成本合理,已在各个工业领域得到广泛应用,成为国际上应用最广泛的开放式现场总线之一。

但是随着工业水平的提高,控制系统越来越复杂,对数据传输速率、数据吞吐量及通信可靠性提出了更高的要求。传统的CAN总线通信已经不能满足市场需求,CAN总线的升级总线——波特率可变控制器局域网(CAN with Flexible Data⁃rate,CANFD)应运而生。从2012年第十三届ICC大会上Bosch公司发布CANFD协议,到2015年提交国际标准化ISO11898系列,CANFD技术正在飞速发展[1]。

CAN总线通信的最高传输速率为1Mbps,实际可实现速率只能达到 500kbps[2⁃3]。 CANFD 继承了CAN总线的绝大多数特性,如双绞线串行通信协议、仲裁技术、纠错机制等,但在总线带宽和可传送数据长度方面进行了改善,并通过改变帧结构和提高位速率成功的将数据传输速率提高到了5Mbps,实现了速度与稳定的两者兼得。目前在车载通信领域,CANFD已逐渐取代CAN总线,成为主流总线通信之一[4⁃7]。但车载领域的CANFD总线通信多采用单片机控制以达到节省成本、实现简单的目的,不能应用于对可靠性能和抗干扰能力要求更高的无人机等武器领域中。

CANFD控制器 MCP2517芯片为 SPI通信方式,支持SPI通信的微处理器有很多,如单片机、数字信号处理(Digital Signal Processing,DSP)等,本文提出采用DSP+现场可编程门阵列(Field Pro⁃grammable Gate Array,FPGA)来实现CANFD通信。DSP通过外部存储器接口(External Memory Interface,EMIF)与 FPGA相连,使 FPGA作为DSP的高速数据传输接口对CANFD控制器进行读写操作。本文提出的基于 DSP+FPGA控制的CANFD总线通信方法能够克服单片机抗干扰能力差、数据读写速度慢的缺陷,更能够满足对可靠性有更高要求的航天航空控制的需求。

1 CAN总线与CANFD总线

由于CAN总线每次只能传输8字节数据,通信速率较慢,且总线的位填充会造成干扰,可靠性低。CANFD总线由CAN总线改进后优势明显,具体体现在以下几个方面:

1)数据场长度:数据场由数据帧中传输的数据组成,CAN的DLC数据位是4bits,数据帧中最多包含8字节传输数据。CANFD对数据场的长度进行了扩展,并采用非线性定义的方式定义数据字节,每数据帧传输数据长度可达64字节,避免了数据分裂的状况。

2)可变比特率:CANFD总线在仲裁段和数据段可采用不同的波特率传输,通过控制场的比特率转换(BRS)位来控制是否切换比特率,隐性表示转换可变速率,显性表示不可转变速率,CANFD的波特率表示为500kbps/2Mbps。其中,500kbps为仲裁段的传输速率,2Mbps为数据段的传输速率。

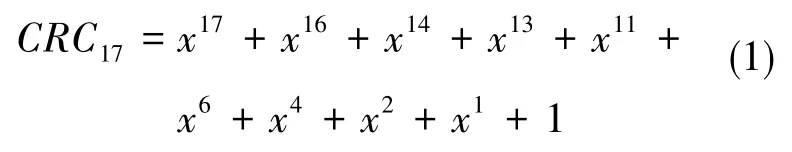

3)新CRC格式:由于CAN总线位填充规则对CRC的干扰,使得错帧漏检率没能达到设计预期。CANFD总线对CRC算法做出了改变,将填充位纳入到CRC计算中,即CRC以含填充位的位流进行计算,以一个填充位开始并且序列每4位插入一个填充位加以分割,且填充位的值是上一位的反码。格式检查时,如果不是反码就做报错处理,且CRC长度是由传输数据长度决定的,当传输数据为0~16字节时,CRC长度就为17,CRC多项式可表示为

当传输数据长度为17~64字节时,CRC长度为21,CRC多项式就表示为

CANFD的CRC算法新的CRC段纠错方式可以改善错误帧漏检率。

4)DLC编码:CANFD数据帧采用了新的DLC编码,在数据场长度为0~8个字节时,采用线性规则,当数据长度为12~64个字节时,采用非线性规则编码,具体的编码规则如表1所示。

表1 DLC编码规则Table 1 Rules of DLC code

2 系统硬件设计

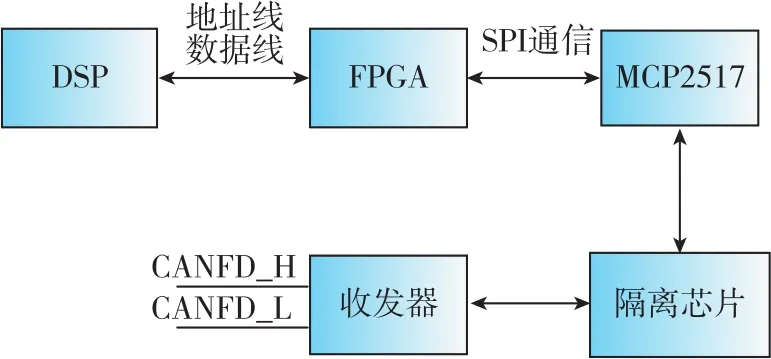

系统包括DSP、FPGA、CANFD控制器、收发器、信号隔离芯片。

DSP、CANFD控制器与FPGA通过SPI接口通信,DSP选用TI公司的TMS320C6713,FPGA选用Cyclone公司的EP4CE6F17C8。DSP作为数据解算核心和控制核心,自身更擅长数据处理而非逻辑控制,且自身接口有限,没有良好的通用性。FPGA接口多且大多可通用,逻辑控制简单,能够满足大数据量高速的传输控制,且可实现译码、外围接口及接口电路的集成[8]。

DSP+FPGA+MCP2517配合实现CANFD总线的数据传输,FPGA作为DSP与外围接口之间的桥梁,在接收到信号上升沿时,对相应数据进行锁存,完成信号的采集、滤波、解调,再将数据库存放在制定的内存存储器,DSP通过EMIF总线接口读取相应数据,并作新数据处理和控制指令的执行,且并行处理方式的FPGA对CANFD控制器进行数据传输和使能、中断控制。

支持SPI的微处理器有ARM、STM32、DSP、FPGA,采用DSP+FPGA模式来实现CANFD通信,能够克服单片机固有的缺陷,更能够满足对可靠性有更高要求的航天航空控制的需求。单片机处理速度低、接口少、资源有限,遇到强干扰程序容易跑飞[9⁃12]。系统的硬件设计框图如图1所示。

图1 系统硬件框图Fig.1 Block diagram of system hardware

2.1 CANFD控制器模块设计

CANFD控制器采用 MCP2517,MCP2517是Microchip公司开发的一款带 SPI接口的外部CANFD控制器,微处理器只需要支持SPI通信即可扩展CANFD。MCP2517控制器支持CAN 2.0B和CANFD模式,时钟频率可达40MHz,通过SPI可与控制器进行通信,SPI的时钟频率可达20MHz;31个FIFO可配置为接收或发送;32个过滤器和屏蔽器对象可设置来对接受报文的ID屏蔽;仲裁域比特率高达1Mbps,数据段波特率高达1Mbps;发送报文可设置发送优先级。

CANFD控制器模块设计电路如图2所示。

图2 CANFD控制器模块原理图Fig.2 Schematic diagram of CANFD controller module

2.2 CANFD总线收发器模块设计

采用TJA1044GT芯片作为CANFD总线的收发器,芯片的差分接收端并联120Ω的匹配电阻,来克服 “长线效应”,收发器模块电路如图3所示。收发器与CANFD控制器之间选用隔离芯片ISO7242对输入输出总线差分信号进行隔离,隔离电路如图4所示。

图3 CANFD总线收发器模块电路图Fig.3 Circuit diagram of CANFD bus transceiver module

图4 信号隔离模块电路图Fig.4 Circuit diagram of signal isolation module

3 系统软件设计

系统软件设计主要分为模块初始化、报文接收、报文发送,软件实现流程如图5所示。

图5 软件设计流程图Fig.5 Flowchart of software design

模块初始化是指DSP通过FPGA向CANFD控制器芯片发送配置信息,对CANFD控制器进行初始化设置,模块初始化配置的流程如下:

1)选择工作模式为配置模式,设置波特率可变。

2)配置标称位时间和数据位时间寄存器,根据想要设置的仲裁域和数据域的波特率值计算寄存器设置值。

3)配置FIFO控制寄存器,设置FIFO的报文深度、有效负载大小、报文发送优先级、接收还是发送FIFO、设置非空/非满中断允许。

4)设置接收过滤器和屏蔽寄存器。

5)配置CANFD控制寄存器,选择工作模式为CANFD工作模式。

模块初始化完成后,可进行报文发送和接收配置,配置流程如下:

1)读取发送/接收下一报文的地址:MCP2517控制器的RAM区没有对每个FIFO对象设置固定的内存地址,报文对象的地址取决于所选的配置,但是应用程序不必计算地址,用户需要发送开始前通过读取发送/接收FIFO的用户地址寄存器值来获取下一个报文对象的地址。

2)发送报文时,DSP通过FPGA向CANFD控制器的FIFO地址(上一步骤读到的下一发送报文对象的地址)写入要发送的报文;接收报文时,通过配置过滤器对象和屏蔽器对象给接收FIFO匹配一个或多个过滤器。

3)启动发送/接收:设置FIFO控制寄存器中的报文请求发送和FIFO头部递增。

4)报文发送/接收过程中可观察FIFO状态寄存器中的报文索引标志及发送/接收FIFO的用户地址位是否正确递增。

4 实验验证

4.1 实验步骤和方法

DSP TMS320C6713的主频为528MHz,FPGA EP4CE6F17C8的主频为66MHz,MCP2517FD芯片的时钟频率为 40MHz,SPI接口的时钟频率为20MHz。所以,将实验条件设置为通信电缆长3m、接收发送的报文长度为最大64字节。

CAN总线通信最高传输速率为1Mbps,正常可实现速率只能达到500kbps,CANFD由于控制域和数字域采用不同的波特率进行数据通信,通信速率在理论上大于CAN总线通信。在实验中验证当波 特 率 为 500kbps/2Mbps 和 1Mbps/5Mbps 时CANFD总线通信的准确性,实验步骤为:

1)首先使用Modelsim仿真软件对FPGA程序进行时序仿真,仿真结果预期一致则证明FPGA与CANFD控制器通信正常。

2)DSP通过FPGA来配置MCP2517控制寄存器的值,将控制器设置为CANFD模式,设置波特率、ID号和报文深度,有效数据长度为64字节。

3)编写DSP程序实现CANFD总线的自发自收功能,提前编辑CANFD总线要收发的数据信息,每次发送200个报文,共发送10次。

4)利用CANFD通信调试上位机对比发送数据与接收数据,统计传输时间、错误字节数,计算误码率。

4.2 仿真验证及结果

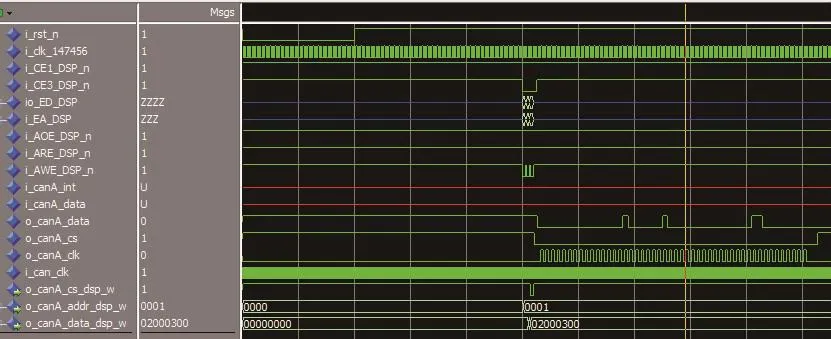

使用Modelsim仿真软件对FPGA程序进行时序仿真并给定输入,如果得到预期输出,则证明可以实现对CANFD控制器的时序控制,且理论上可以实现基于DSP+FPGA系统的CANFD通信。

仿真模拟DSP通过FPGA向CANFD总线发送信息,根据控制器芯片MCP2517的SPI指令格式,FPGA应向MCP2517发送复位指令来将控制芯片的内部寄存器复位为默认状态,复位指令为发送地址0x0000和数据信息0b000,接着向控制芯片地址为 0x0001的寄存器写入数据信息0x02000300,最终得到的仿真时序图如图6所示。

图6 仿真验证时序结果Fig.6 Timing results of simulation verification

由图6可知,时序仿真结果与设想一致,表现为:当DSP控制FPGA的片选拉低且写使能信号拉低后,FPGA控制的CANFD的片选被拉低,CANFD的数据线上依次传输地址信息和数据信息(0x0001和0x02000300), 证明了基于 DSP+FPGA系统的CANFD通信可行性。

4.3 实验验证及结果

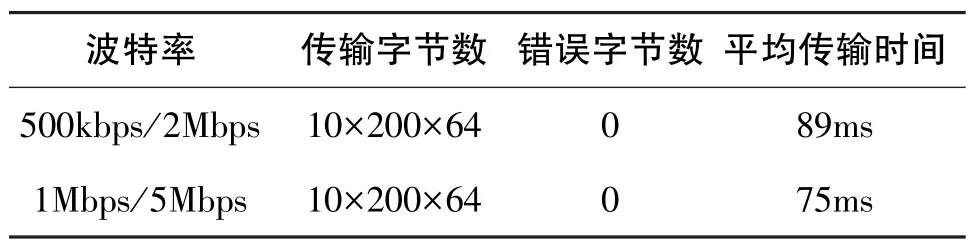

在DSP+FPGA+CANFD控制器实验平台上对4.1节中的步骤2~步骤4进行实验验证,通过CANFD测试盒和上位机来记录发送和接收的数据,对发送和接收的数据进行比对,实验结果如表2所示。

表2 实验验证结果Table 2 Results of experiment verification

由表2的实验结果可知,在通信电缆长3m、发送10次数据、每次发送200条报文、报文有效长度为64字节、波特率设置为500kbps/2Mbps及1Mbps/5Mbps条件下,错误字节数均为0,误码率小于1%,证明了该系统可实现可靠的CANFD通信。

由于实验条件有限,不能充分验证在不同工作环境下的CANFD通信情况,如极限温度对通信数据准确性的影响、不同波特率的有效通信距离变化等,所以本文提出的方法仍需要加入考虑环境温度和通信距离等更多因素的对比实验来验证。

5 结论

随着汽车、无人机等领域对通信数据传输速率、数据吞吐量及可靠性提出了更高的要求,CANFD总线通信方法已逐渐开始取代传统的CAN总线通信,保证CANFD数据传输的稳定性和可靠性也逐渐成为学者及工程师关注的重点。本文采用DSP+FPGA+MCP2517的方法来实现CANFD通信,并通过了仿真和实验验证,结果表明:该方法降低了软件调试难度,减轻了处理器的运行负载,提高了系统的抗干扰能力,实现了5Mbps数据传输速率,是CAN总线最高传输速率的5倍。实际应用中会有通信距离、环境温度等多种因素影响通信效果,本文提出的方法还需要通过更深入的研究来完善总结。