基于ARM-FPGA的推进电机振动反馈系统设计

2021-02-02龚学锐杨一鹏徐晓康邱长青

龚学锐,杨一鹏,徐晓康,邱长青

(船舶综合电力技术重点实验室,武汉 430064)

0 引言

推进电机作为船舶的主要动力设备,对其进行有效地控制,将直接影响船舶整体的性能。实现对推进电机振动的实时监测与反馈,利用反馈数据对电机进行控制,能够进一步保障电机的安全运行;同时利用监测信息可以评估设备的健康状态,对相关故障进行及时报警,保证推进电机在船舶航行中的可靠性。

电机运行产生振动。不同运行状态下的振动形式所包含的信息也不尽相同。因此,根据电机振动情况判断电机故障类型和部位,进而对电机进行控制是保障电机正常运行的重要手段之一。ARM和 FPGA是被广泛应用的嵌入式处理器,ARM具有较强的事务管理功能,而 FPGA接口丰富、灵活性强、可扩展性好,两者结合构建的嵌入式采集系统兼备各自的优点。与传统的嵌入式系统相比,这样的架构能够根据需要灵活地选择连接的外设和控制器,同时能够根据需求在硬件实现和软件实现之间进行权衡。当软件实现成为瓶颈时能够用硬件逻辑定制协处理器引擎来高效的实现算法,具有较好的性价比需求。

本文针对船舶推进电机,基于 FPGA+ARM的异构架构设计了一种主动控制用振动监测及信号反馈系统,并分别从硬件和软件设计两方面进行论述,最后借助实验证明该系统在电机振动监测方面具有有效性和可靠性。

1 硬件电路设计

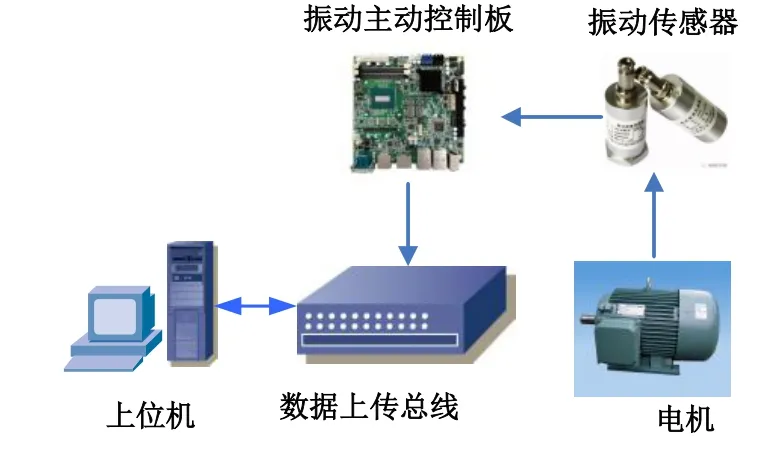

图1为整体监测系统的总体框图,主要由振动传感器、振动主动控制板、数据上传通信、上位机这几个重要部分组成。其中基于 FPGA和ARM的振动主动控制板是整个系统的核心部件,它通过振动传感器获取电机的振动信号,进行电机故障振动信号的采集,从中提取出用于后续诊断的故障特征向量,并将相关信息通过 CAN总线和串口传输给上位机,进行后续的相关控制。

1.1 信号采集电路

信号采集电路主要分为模拟调理电路和 AD采样电路两部分,图2为模拟调理电路的设计框图,其主要芯片使用的是OPA1652以及THS4524。Opa1652是一款低噪声的双通道运放。低失真:1 kHz 时为 0.00005%;采用双电源或者单电源供电,供电范围宽至40 V,典型的供电范围是±2.25 V至±18 V或 4.5 V至36 V,本设计中采用±5 V供电。THS4524 是一款4通道低功耗、完全差分运算放大器,实现输入单端信号到差模信号的转换。调理电路利用OPA1652芯片实现电压增益降低后通过 THS4524实现单端转差分输出至后续的AD采样电路,并在此过程中同时实现了输入的宽范围低通滤波功能。

图1 系统总体框架图

图2 模拟调理电路框图

AD采样电路采用ADS1274芯片实现4路数据的同步采样,该芯片在工业领域广泛应用,在AD内部每个通道分别有一个模数转换器,实现模拟信号采集。同时AD内部有4个数字滤波器,在特定工作模式中,会对采集的数据进行滤波,减小噪声,提高精度。最后通过串行方式将采集结果输出。

1.2 数字处理电路

数字处理电路的核心芯片采用 xilinx zynq7系列芯片 xc7z020-clg484-2,该芯片结构集成了基于ARM公司双核ARM Cortex-A9多核处理器系统(Processing System,PS)和基于 xilinx的可编程逻辑资源的 FPGA系统(Programmable Logic,PL)。与此同时为完成大量数据缓存整体电路还接有外部存储器DDR3和eMMC,具体结构如图3所示。ARM作为主控制核,控制FPGA完成信号采集和预处理部分,并将它们存储至外部DDR3存储器中。同时ARM通过通讯电路以CAN通信的形式获取所需上位机所需数据并从DDR中提取,经数据后处理后将相应数据上传至上位机,用于实现后续功能。

图3 数字处理电路结构图

2 系统软件设计与实现

本文软件系统在 vivado2017.4和 xilinx的SDK软件编译环境中实现,采用verilog和C/C++语言,分别在芯片PL和PS两侧实现FPGA和ARM的程序功能。系统对整体软件的需求为能够同时进行 4路 AD采样结果的快速傅里叶变换(FFT)处理,最终对4路处理结果中挑选1路的某个频点通过 CAN接口上传计算后数据,同时还能够将时域数据通过串口上传至上位机,总体流程图如图4所示。整体软件由PS和PL两部分协同工作,PS侧作为主控,主要承担通讯功能、控制功能和数据后处理。PL部分则主要实现FFT计算和AD数据采样两个功能。

图4 系统流程图

2.1 系统通讯功能实现

系统与上位机通信主要通过CAN通讯完成,中断函数通过邮箱地址判断接受指令是参数设置还是数据请求,如果是参数设置命令,则通过解析接受到的指令更新并维护内部参数组,包括是否控制pl侧进行FFT处理,是否上传调式数据,是否使用频率校正,同时上位机还能够设置系统默认的初始化值并生成 fat文件供芯片上电时读取,实现掉电记忆。具体流程如图5所示。若是数据请求指令,则计算相应四个频点的位置,跳转进入数据处理的主体函数进行处理,以此来响应数据请求指令。

2.2 处理算法实现

处理主体主要包含三个部分,第一部分主要负责根据配置参数计算待处理时域数据在ddr中的存储位置,并请求FPGA进行FFT计算将数据存储到相应地址,具体流程如图 6-a)所示;第二部分主要是数据的后处理部分,如图6-b),主要对FFT处理后的数据进行后处理,包括频点选取、增益矫正、量纲转换等。第三部分为数据回传部分,主要负责将处理后的数据通过 CAN通信回传给上位机。同时能够根据上位机参数设置将指定长度以及抽取数据源的时域数据通过串口传给上位机,但这一部分在正常工作模式下一般不打开。

图5 通讯程序流程图

图6 主题函数流程图

3 实验测试结果

图7 系统板卡实物图

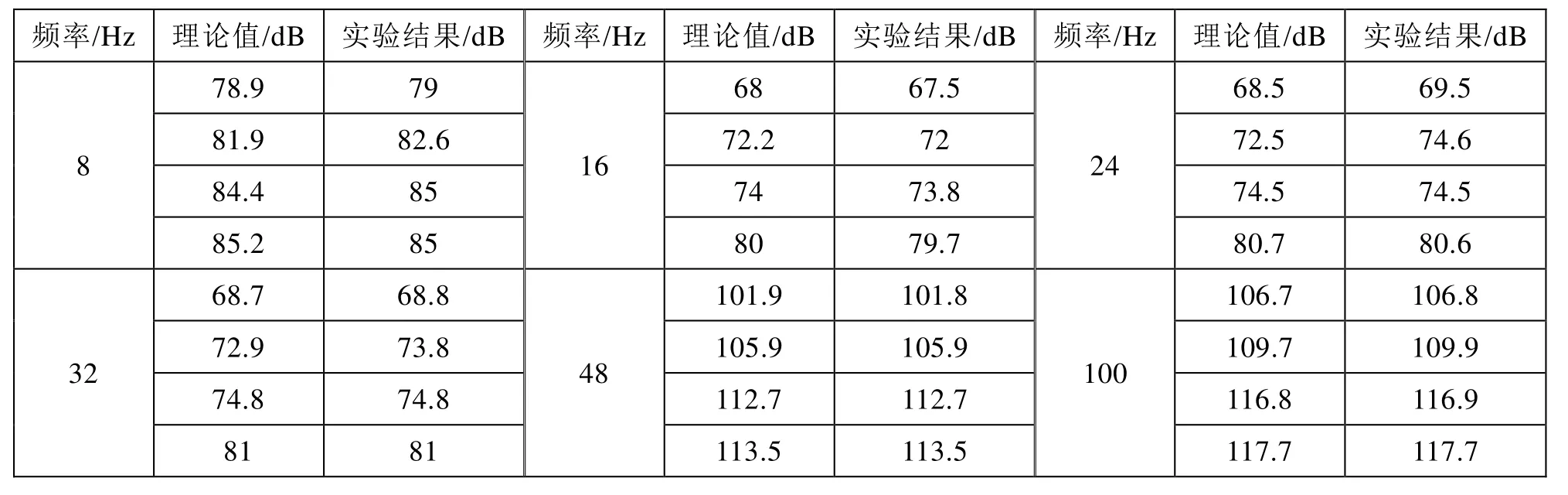

根据上述硬件和软件设计,对本系统进行实验验证,图7为本系统实物图,中间为系统核心板,图8为上位机监测界面。实验通过信号发生器输入激振器模拟在不同频率引发不同程度的电机振动噪声并与理论值进行对比。实验结果如表1所示,实验证明在一定频率范围内系统保证了良好的检测精度。

表1 振动信号监测数据

图8 上位机监测界面

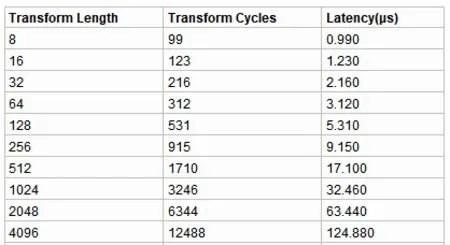

图9 FFT计算用时

实际延迟造成的原因主要有一下几个方面,AD采集、存储和FFT计算:AD采集和FIR计算采用随路计算,即随着AD数据流进行计算。即需要在1个采样点的时间内完成当前点采样以及fir滤波,否则就会被后来的数据冲掉。AD采样率是30.720 K,所以这部分延迟为不大于32 μs。而存储采用axi总线存入 ddr3中,axi总线目前使用的是150 M*64bit,因此这部分时间可以忽略不计。FFT每路延迟最大如图9所示,每路需要124 μs。总计不超过500 μs。综上所述振动板处理延迟较小,能够实现参数实时反馈。

4 结论

本文对推进电机振动信号反馈系统从硬件和软件方面进行了设计,结合ARM和FPGA的异构系统架构设计了一种精度高、实时性强的电机振动信号反馈系统,对采集数据进行后处理计算,并通过上位机下达指令需求上传相应数据,为后续设备故障检测、运维提供了良好的技术基础。且该系统资源占用少、扩展性强,具备较强的应用价值,可以广泛应用。