自适应中值滤波器优化及其FPGA实现

2021-01-16王丽红胡长宏范鲜红高春歌张晓峻孙晶华

王丽红 胡长宏 范鲜红 高春歌 张晓峻 孙晶华

摘要:针对现有自适应中值滤波器运行耗时长以及在高椒盐噪声密度下去噪性能低的问题,提出一种基于FPGA的自适应中值滤波器优化方法,对铁轨图像进行滤波研究。加入像素噪声阈值判断和二次求中值的方法,提高图像在大椒盐噪声密度下的处理能力,在大窗口中只对外围像素求中值减少迭代处理,降低算法的复杂度和运算量,利用FPGA的流水线结构和并行处理能力,加速算法的运行。与现有仿真滤波效果最优的中值滤波器相比,优化方法图像细节保持更加完整,运算量降低15%,峰值信噪比值平均提高0.9dB,采用FPGA运行优化算法将耗时降低到了毫秒级,为铁轨图像实时处理应用提供了基础。

关键词:自适应中值滤波;噪声闲值FPGA;流水线结构;实时处理

DOI:10.15938/j.jhust.2021.05.009

中图分类号:TP391.41 文献标志码:A 文章编号:1007-2683(2021)05-0068-08

0 引言

图像滤波去噪是图像预处理过程的关键技术之一,其性能好坏直接影响后续图像的效果。图像滤波去噪最常用的方式是将某一点像素与其邻域内的几个像素放在二维像素窗口内进行处理,这是由于某一点的像素值与其邻域像素相关度最大,噪声信号和边缘像素与其邻域其他像素灰度值差异较大。基于此,可采用剔除邻域内噪声信号的方式来达到去噪的目的[1]。中值滤波是基于邻域处理的一类非线性滤波方法,可有效去除椒盐噪声[2]。椒盐噪声最明显的特点是会形成灰度值极大或极小的噪声点,这在图像显示上是一些突兀的黑白點,且这些点一般是孤立存在的,互相之间没有联系[3]。但是中值滤波存在局限性,当滤波窗口较小时去噪能力较差,当滤波窗口较大时,虽然有较好的去噪能力,但不能较好的保持图像细节。为此学者们提出自适应中值滤波器(Adaptive Median Filter,AMF)以及优化方法来应对这种问题。标准的自适应中值滤波器利用窗口迭代的方法求出窗口中值再判断输出,在大滤波窗口下存在细节显示模糊,且在大窗口内对小窗口像素的重复排序使得排序效率较低[4-6]。文[4]提出尽可能使用小窗口滤波,并引入判断阈值对疑似噪声的中心像素进行二次判断进而输出。文[5]提出在自适应中值滤波器判断到最大窗口时,利用非极值像素灰度值的均值来替代输出,在高椒盐噪声密度下滤波具有良好效果。现有的算法研究都基于计算机运行,实时性不能满足实际应用需求。针对铁轨健康状态视觉检测应用需求,提出在求中值时加入对噪声判断的步骤,提高铁轨图像噪声处理能力,降低窗口迭代引起的运算量,同时结合FPGA流水线并行处理结构加速算法的运算速度,提高自适应中值滤波算法的实时性[7]。

1 自适应中值滤波器优化

自适应中值滤波器加入了窗口自适应增大功能,在滤波窗口内判断中心像素是否为噪声,进而选择输出原中心像素值还是窗口像素的中值[8]。假设在大小为N×N的正方形像素邻域内,尸。是窗口中心像素的灰度值,W1为当前窗口边长,Wmax为规定的最大窗口边长。Pmin、Pmed和Pmax分别为某一窗口中的灰度最小值、灰度中间值和灰度最大值,则自适应中值滤波的输出流程为:

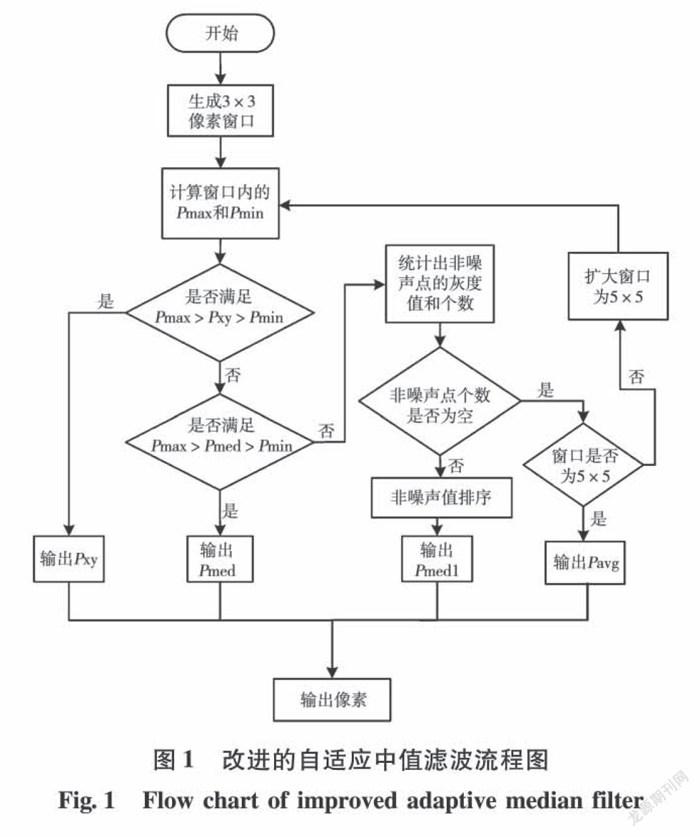

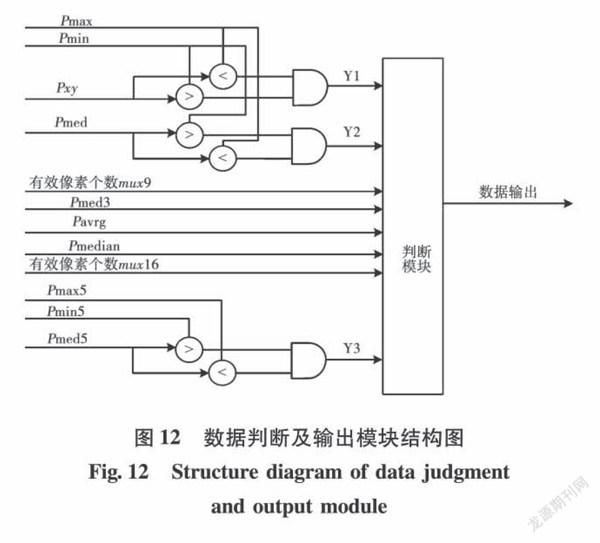

1)若Pmin 2)若Pmin 从以上滤波方法可发现,算法对噪声点的判断是以Pmin和Pmax为基准的,如果Pxy=Pmin或者Pxy=Pmax,则认为Pxy为噪声点,这样的判断很容易把边缘或细节这些高频区域误认为噪声点[9]。在一个奇数边长的窗口中,若椒盐噪声密度大于50%,会导致窗口内的中值仍然是噪声点,则自适应中值滤波算法不能取到误差较小的结果[10]。另外,随着滤波窗口的增大,椒盐噪声滤除效果得以提高,但图像细节丢失变严重[11]。 为此,本文对现有自适应中值滤波进行优化,采用最大为5×5的窗口,通过遍历3×3窗口内的所有像素,筛选出非噪声信号,求出非噪声数组中值并判断输出,只有当小窗口中所有像素都被噪声污染时才增大窗口。具体流程如图1所示。 图1 改进的自适应中值滤波流程图 第1步:在3×3窗口中采用标准的3×3中值滤波方法,若满足Pmin 第2步:对3×3窗口内所有像素进行非噪声点判断和统计,并将统计结果放在一个数组,若数组非空,则将这个数组的中值Pmed1作为输出结果。这是由于3×3窗口内有效像素灰度值的变化不会很大,若在该窗内存在非噪声点的像素,统计这些像素值并用其中值Pmed1替代中心像素Pxy输出,这样就可排除噪声且对图像质量影响不大,这与标准中值滤波的思想一致。本文为了简化计算,设灰度值在1和254之间的像素为非噪声信号;若数组为空,则说明3×3窗口内经判断都是椒盐噪声,则将窗口扩大到5×5窗口。 第3步:在5×5窗口中,仅对中心像素Psr和3×3窗口以外的16个像素进行判断,判断条件与前两步一致。采用这种方法可减小计算量提高运算效率。若5×5窗口内非噪声数组为空,即5×5窗口内数据均为椒盐噪声,则进入第4步。 第4步:求出3×3窗内中心像素四邻域的灰度值的平均值Pavg,将该值作为输出结果。这是一种折中的做法,可避免直接输出椒盐噪声。 以上过程的优势在于小窗口细节保持良好且能有效滤除噪声,在大窗口滤波时由于剔除了小窗口的所有噪声点,降低了大窗口排序带来的运算压力,提高了算法的运算效率。 2 仿真实验 以一幅360×134像素的断裂铁轨图作算法研究,采用处理器为Intel Core i7-8700的计算机进行仿真,处理器的正常运行频率可达3.19GHz,仿真过程中像素点的灰度值采用64位浮点数。图2给出了标准的3×3,5×5中值滤波器,最大窗为5×5的AMF,文[4]和[5]提出的方法以及本文方法去除椒盐噪声密度为70%的图像的效果。后三种方法最大滤波窗口为5×5。由图2可以看出,标准的中值滤波和自适应中值滤波器的去噪效果有限,文[4]和[5]与本文方法效果接近,但通过裂缝边缘和铁轨平面的细节可看出文[5]对细节处理不佳。 椒盐噪声密度为70%的情况下,以上算法运行时间如表1所示,本文算法的效率要优于文[4]和文[5],消耗的时间是文[4]的94%,是文[5]的75%。 采用峰值信噪比(PSNR)和平均均方误差(NMSE)评价滤波的效果[12]。PSNR表示信号的最大功率与噪声功率的比值,NMSE表示图像灰度函数的稳定性,PSNR越大,NMSE越小,说明滤波效果越好,图像还原度越高。 不同椒盐噪声密度下几种方法的PSNR和NMSE参数曲线如图3和图4所示。可以看出,标准的3×3和5×5中值滤波性器能明显低于5×5自适应中值滤波器及其优化后的滤波器。椒盐噪声密度大于50%的情况下,标准的中值滤波器及5×5自适应中值滤波器的PSNR与NMSE参数都骤降,而文[4]和[5]以及本文优化的滤波器的两种参数曲线变化缓慢,这说明优化方法可有效提高滤波器在较高噪声密度下的去噪效果。由图3可见,椒盐噪声占比从10%到90%范围内,本文方法的PSNR值略高于文[4]和[5]且整体趋势平滑,经计算本文方法在噪声密度小于80%时,PSNR的平均值比文[4]高1.23dB,比文[5]高3.64dB,大于80%后文[4]的PSNR值快速降低,文[5]的PSNR值降低缓慢,大于87%后文[5]的PSNR值具有优势。 综上所述,本文方法降低了中值滤波器算法的复杂度,能够保持图像的细节,去椒盐噪声的效果更好。此外,本文方法对窗口内像素的判断是全覆盖式的,不会漏掉有效像素,这对于还原图像有重要意义。 3 基于FPGA的滤波器实现 根据表1的结果,不同中值滤波器在Intel Corei7-8700处理器上的运行时间都超过了2s,不能满足铁轨图像实时处理的要求。为此,采用Altera公司的Cyclone IV系列FPGA产品EP4CElOF17C8N,加速算法的运行速度。该芯片具有10320个逻辑单元,可满足算法硬件实现的资源需求。 数字图像的传输是以数据流的形式将像素灰度串行传输[13],像素输出流向是单向的,若图像处理算法没有反馈或迭代运算,则可采用流水线设计的方式来提高系统的工作频率[14]。流水线设计只需在开始时刻需要额外的处理时间,其余时间都是在不断输出数据[15]。若采用串行CPU处理像素,则每个像素都会花费多个时钟周期完成处理,所有像素处理时间累加就是一幅图像处理完毕到显示所需的时间,像素越多则耗费的时间成倍增加,因而无法得到实时的处理效果[16]。而采用FPGA流水线处理结构,所有像素处理所耗费时间只需几个时钟周期,这就使得FPGA很适合于实时处理图像[17]。 3.1 滤波器实现的总体架构 本文优化滤波器在FPGA上实现的结构如图5所示。它包括了行场同步控制模块、5×5窗口生成模块、数据排序模块、噪声判断及中值输出模块和数据判断及输出模块。这些模块采用流水线的方式对图像信号流并行处理,运算过程中像素点的灰度值采用8位的定点数。 实现流程为:数据输入端串行输入一幅360 x134像素的8位灰度图像数据,以行场信号为数据有效标示位。通过5×5窗口生成模块可产生以Pxy为中心像素的像素窗口。Pxy和其外围第一层数据构成3×3窗口进行排序,同时Pxy和其外围第二层数据构成5×5窗口进行排序,在排序模块中分别加入一个噪声判断和像素输出模块,用以计算该窗口内的有效像素个数以及寄存灰度值,进而求出窗口内的中值。最后将所有可能的结果同步后交给数据判断及输出模块,进行最终的输出判断。经仿真验证,在像素时钟频率为24MHz下,从窗口读出一个数据到该数据处理结束后输出,仅延迟6个时钟周期,实现了图像的实时处理和输出。 3.2 基于IP核的像素窗口生成模块 滤波器首先需要先生成5×5窗口,也就是将一帧画面中5×5窗口内的25个数据对齐。本文利用Altera FPGA中自带的IP核Shift Regester可快速实现。对360×134像素的图像,需要先缓存前5行的像素[18]。通过IP核设置界面选择RAM的位宽为8,抽头距离TAP_DISTANCE为256,抽头数目NUMBER_OF_TAPS为5。图6为该IP核的工作原理,假设输入9个8位的数据流,这与图像传输的数据方式一样,通过控制抽头数目和抽头距离可将其变为一个3行3列的数据窗口。 在设置好IP核之后,生成5行同步的数据,另外还需选取5列数据,才能生成窗口。具体做法为:将这5行数据的第1列分别放入寄存器中,待下一个时钟周期,再将第二列放入新的寄存器中,第一列则用打拍同步的方式使两列数据对齐,重复这种操作,在第五个时钟沿就有5行5列数据同步。 3.3 排序模块设计 5×5窗口内的数据对齐后,再将其同时分别放人两个排序模块中,其一是对3×3窗口9个数据进行排序,其二是对5×5窗口外围16个像素及中心值共17个数据进行排序。图7表示取5×5窗口中的3×3窗进行排序,图8表示对外围数据和中值的排序。 对3×3窗口的排序采用快速求中值的方法,直接输出9个数中的最大值、最小值和中间值[18]。图9为该方法的原理图,设3×3窗口内的各个像素分别为P11、P12、P13、P21、P22、P23、P31、P32、P33。在第一个时钟周期内,将窗口内的每一行的數分别放入3个三输入排序模块中,可求出每一行的最大值Pmax1、Pmax2、Pmax3,最小值Pmin1、Pmin2、Pmin3和中间值Pmed1、Pmed2、Pmed3;在第二个周期内将这些最大值组,中间值组和最小值组分别放入3个三输入排序模块,求得整个窗口的最大值,最小值;在第三个周期内,将最大值组的最小值Pmin_of_max、最小值组的最大值Pmax_of_min以及中值组的中间值Pmed_of_med放入三输入比较器中确定整个窗口的中间值Pmed_of_9。 为实现对5×5窗口中外围数据的快速排序,采用17值并行全比较排序方法,该方法需要的比较器数目为256个,只需要4个时钟周期可完成比较输出[19]。该模块分为四部分,首先将所有元素两两比较,若比较数比被比较数大,则为真,输出1,否则输出0,这样每个数据累计获得1的次数最多为16,最少为1;通过比较次数的大小就可判断出数据大小[20]。特别的,若出现数据相同的情况,这时可根据数据出现的先后顺序来选择比较器,设两个相等的数分别为Pm和Pn,Pm为比较数,m和n分别为数据的原始排序位置。若m>n,这时的比较器采用“≥”号,相当于给比较数的次数加1,而若m 3.4 噪声判断和像素输出模块设计 在3.3节排序模块进行的同时,需要对该窗口内像素数据进行噪声判断,并求出非噪声像素数组的中值。在噪声判断模块中,设灰度值0为阈值1,灰度值255为阈值20该模块从数据输入到统计出有效像素个数需要两个周期,图10所示为3×3窗口中该模块噪声判断及非噪声像素个数统计部分的结构图,5×5窗口中外围像素的噪声判断和统计原理同理。 图11 所示为3×3窗口非噪声像素数组的中值输出模块的原理图,若非噪声数目为奇数,则输出该数组的中值;若数目为偶数,则输出中间两值的均值。该模块应在噪声判断和统计模块后加入,需要先将非噪声像素放入寄存器中组成新的数组,由于不同元素数目会导致数组的中值位置不同,这里利用替代的方法。若判断某一灰度值为0或255即噪声信号,则将该值替换为255。再将替换后的数组放入新构造的9值并行全比较排序模块,这样有效像素经过由小到大的排序会在数列的前列,噪声会被放在最后,这时只要根据有效像素的数目,即可确定取数组的哪一个元素,或哪两个元素的均值。如计算得到有效像素数目为5,则经过排序的9值数组前5个值是有效的,后面的都是255,取第3个元素输出即可。5×5窗口中外围非噪声数组采用同样的求中值方法。 噪声判断和像素输出模块耗费时钟周期为5,但由于加入3个并行全比较模块,需要大量比较器资源,故逻辑资源消耗较多。 3.5 数据判断及输出模块设计 完成3.3和3.4节模块的运算后,需要将运算结果对齐处理,然后交由数据判断及输出模块,图12为数据判断及输出模块结构图。 设Pmed3和Pmedian分别为3×3和5×5窗口非噪声像素的中值。整个判断的流程为:若有效像素mux9≥1,说明小窗口有非噪声点,在3×3窗口内进一步判断,若Y1为真,则直接输出Pxy,若Y1为假且Y2为真,则输出Pmed,否则输出均值Pmed3;若mux9=0并且mux16≥1,说明3×3窗口内全是噪声,换至5×5窗口判断,若Y3为真,则输出Pmed5,否则输出Pmedian最后,若Mux9和mux16都为0,则直接输出Pxy四邻域的灰度均值Pavrg。经过判断模块的输出值即为优化后的自适应中值滤波器的输出结果。 3.6 FPGA资源使用情况分析 以上模块实现的滤波器,基于EP4CElOF17C8N采用Modelsim工具进行RTL和门级仿真验证成功后,对硬件代码进行综合生成硬件烧写文件。 FPGA硬件资源消耗情况如表2所示,可看到该模块的逻辑资源占用为3565个,占总资源的35%,需要的RAM资源为25536比特,占总RAM的9%,内部乘法器资源未使用。滤波器算法主要对数据进行移位处理和大小比较,所以逻辑单元资源使用较多,未使用到乘法器。 4 实验测试 EP4CE10F17C8N芯片运行优化后的中值滤波器程序,对图2(b)中的8位噪声图像数据进行处理,运行结果传送至计算机中运算PSNR和NMSE参数。采用计算机的仿真结果和FPGA运行的结果对比如图13和图14所示,图中文[4]方法、文[5]方法和软件实现方法都是采用计算机仿真运行相应的算法,硬件实现方法是采用FPGA实现,其原理与软件实现方法一致。在不同的噪声密度下,软件实现方法的结果均优于FPGA运行的结果,但趋势基本一致。这是因为计算机采用的是64位浮点,而FPGA处理器采用的是8位定点,运算过程中数据截取导致误差,因此计算机运行效果要比FPGA好。 由图13对比可见,FPGA运行结果的PSNR平均值比仿真实现小2.35dB,80%噪声密度以下,稍好于文[5]结果,比文[4]的效果略差,但在噪声密度大于80%后,FPGA运行结果的PSNR值仅比软件实现方法的平均PSNR值低0.96dB,优于文[4]的仿真结果,比文[5]的结果略差。此外,椒盐噪声 图14 不同方法的NMSE参数对比密度为70%时,在24MHz时钟下FPGA运行滤波器算法耗时约2.56ms,远低于仿真耗时3.72s,表明FPGA的流水线并行处理结构处理图像具有独特的优势。图14中4种情况得到的NMSE参数相差很小,80%噪声密度以下最大相差不到0.O1dB,FPGA硬件和文[5]仿真基本相当,比其他两种情况略差。 5 结论 对自适应中值滤波器进行了优化,通过加入噪声像素判断步骤,减少对像素的重复排序,提高滤波效率和效果,利用FPGA流水线并行处理结构力大大提高了滤波器执行的速度。仿真结果表明,优化后的中值滤波器综合了文[4]和文[5]的优势,与此相比,能够保持图像的细节,迭代运算效率更高,去椒盐噪声的效果更好。实验测试采用FPGA将滤波器执行的时间由秒级降低到毫秒级,为铁轨健康状态的图像实时处理應用提供了基础。后续研究将会提高FPGA的数据宽度,降低运算结果误差,以进一步提高滤波效果。 参考文献: [1]DRAPER B A,BEVERIDGE J R,et al.Implementingimage Ap-plications on FPGAs[C]//16th International Conference on Pat-tern Recognition(ICPR 2002),2002(3):265. [2]LI ZY,LIU GH,XU Y,et al.Modified Directional Weighted Fil-ter for Removal of Salt&Pepper Noise[J].Patten RecognitionLetters,2014,40:113. [3]陈明轩.数字图像中随机值脉冲噪声的滤除算法研究[D].北京:北京信息科技大学,2013:4. [4]胡瑢华,余传桂,胡环星,等.用于磁瓦图像的改进的自适应中值滤波算法[J].机械设计与制造,2015(2):119. [5]黄文笔,战荫伟,陈家益,等.改进的自适应中值滤波算法[J].计算机系统应用,2018,27(10):187. [6]刘鹏宇,哈睿,贾克斌.改进的自适应中值滤波算法及其应用[J].北京工业大学学报,2017(4):581. [7]TANG J,WANG Y,CAO W,et al.Improved Adaptive MedianFiltering for Structured Light Image Denoising[C]//2019 7th In-ternational Conference on Information,Communication and Net-works(ICICN),Macao,Macao,2019:146. [8]张旭明,徐滨士,董世运.用于图像处理的自适应中值滤波[J].计算机辅助设计与图形学学报,2005,17(2):295. [9]钱伟新,刘瑞根,王婉丽.一种改进的自适应中值滤波算法[J].光学与光电技术,2011(4):55. [10]韩剑辉,葛威.改进型位级中值滤波硬件算法的实现[J].哈尔滨理工大学学报,2015,20(3):35. [11]石婷,张红雨,黄自立.基于Stratix Ⅱ EP2S60的改进中值滤波器的设计及实现[J].国外电子元器件,2007(1):12. [12]师廷伟,金长江.基于FPGA的并行全比较排序算法[J].数字技术与应用,2013(10):126. [13]海敏娟.基于時间序列分析算法的船舶磁场估计[J].舰船科学技术,2021,43(8):124. [14]万丰丰,周国民,周晓.一种去除椒盐噪声的自适应模糊中值滤波算法[J].浙江大学学报(理学版),2019,46(4):445. [15]屈正庚,牛少清.一种改进的自适应加权中值滤波算法研究[J].计算机技术与发展,2018,28(12):86. [16]王志军,于之靖,诸葛晶昌.一种自适应中值梯度倒数加权的图像滤波算法[J].激光与光电子学进展,2017,54(12):148. [17]袁素真,毛峡,陈立江,等.基于双量子比特态测量的量子自适应中值滤波[J].北京航空航天大学学报,2013,39(11):1443. [18]陈健,郑绍华,余轮,等.基于方向的多阈值自适应中值滤波改进算法[J].电子测量与仪器学报,2013,27(2):156. [19]孙海英,李锋,商慧亮.改进的变分自适应中值滤波算法[J].电子与信息学报,2011,33(7):1743. [20]燕红文,邓雪峰,中值滤波在数字图像去噪中的应用[J].计算机时代,2020(2):47. (编辑:温泽宇) 收稿日期:2020-07-01 基金项目:国家自然科学基金(61775044);中央高校基本科研专项资金项目(3072019CF2515). 作者简介:王丽红(1964-),女,学士,高级工程师;胡长宏(1973-),男,博士,副教授. 通信作者:孙晶华(1963-),男,博士,教授,硕士研究生导师,E-mail:sjh1111@sina.com.