基于延时控制的Glitch PUF电路设计

2020-11-12董永兴徐金甫李军伟

董永兴 徐金甫 李军伟

(解放军信息工程大学 河南 郑州 450001)

0 引 言

当今社会,传统密码安全手段受到新兴攻击技术的威胁越来越大。物理不可克隆函数(Physical Unclonable Function,PUF)因其不可克隆性和不可预测性等优良特性,在信息安全领域具有十分巨大的应用潜力[1-2]。目前大部分的物理不可克隆函数是基于现场可编程门阵列(FPGA)实现的。FPGA作为一种半定制电路,可根据用户需求进行编程与配置,具有灵活性高、可重复配置等优点。但其应用于PUF时,缺点也很明显。尤其是对于延时类的PUF而言,电路的布局布线严重影响输出结果,这导致电路的输出结果出现一定的偏差。

为了解决这一问题,许多研究者采用专用集成电路(Application Specific Integrated Circuit,ASIC)设计PUF电路。针对ASIC电路设计成本高、周期长等特点,文献[3-5]使用Monte Carlo仿真方法,模拟工艺和环境的变化,验证所设计PUF的电路性能。

随着对PUF研究的不断深入,国内外学者提出了多种针对PUF电路的攻击技术[6-8]。文献[6]采用机器学习的逻辑回归(Logistic Regression, LR)和演化策略(Evolution Strategies, ES)对多种PUF电路成功攻击并实现预测。文献[7-8]从理论上描述了PUF激励响应行为,配合相应的算法攻击PUF。机器学习对PUF电路实现攻击的主要原因是PUF电路的结构相对固定,产生的大量激励响应对具有一定的线性特性,使得机器学习能够预测延迟信息和生成信息之间的关系,从而实现对电路的攻击。因此,增强电路的非线性特性成为研究重点关注的问题。

文献[9]提出了一种利用门电路之间的延迟变量生成非线性毛刺波形的Glitch PUF架构。通过对电路生成的毛刺信息进行获取、抖动校正、采样等操作,实现毛刺信息与输出信息的转化。文献[10]提出一种基于信号传输理论的Glitch PUF方案。该方案利用毛刺信号的非线性特性抵抗建模攻击,采用多级延迟采样电路实现输出响应,并用Monte Carlo仿真验证电路的性能。但为了保证性能,上述电路增加了辅助电路,增大了资源消耗。

在保证电路在具有良好非线性特性的同时令资源消耗较小是本文关注的重点。本文提出一种基于延时控制的Glitch PUF电路结构(Delay Controlled Glitch PUF, DC-Glitch PUF)。通过提取组合逻辑电路门的传输延时,控制路径延时差,采用T触发器采样电路输出波形。利用延时模块控制不同路径的波形到达T触发器的时间,使其达到良好的性能。在TSMC 65 nm CMOS工艺下,使用Monte Carlo仿真验证电路的性能。

1 Glitch PUF

Glitch PUF首先由Anderson等[11]提出,该PUF基于FPGA实现,电路利用传输路径延时的不同产生毛刺,毛刺决定单元电路的输出结果,输入不同的激励信号选择不同单元电路“异或”输出响应。此结构的问题在于单元电路是静态输出,不能完全保证信息的安全。因此,非线性毛刺的动态输出是关键所在。Suzuki等[9]提出了一种新的Glitch PUF架构,通过随机放置各种组合逻辑门,利用门延时和逻辑转换延时的不同,产生不同宽度的毛刺,保证了毛刺产生与输入数据的非线性。但为了有效采集信号,增加了抖动校正和资源消耗较大的采样电路。针对Glitch PUF的性能和应用场景而言,电路毛刺的产生和电路的轻量级属性是非常重要的。

2 毛刺产生

毛刺与Glitch PUF的性能密切相关。由于Glitch PUF依靠产生的毛刺信号决定电路的输出结果,因此,毛刺信号的峰值、宽度与非线性特性是Glitch PUF电路架构关注的重点。

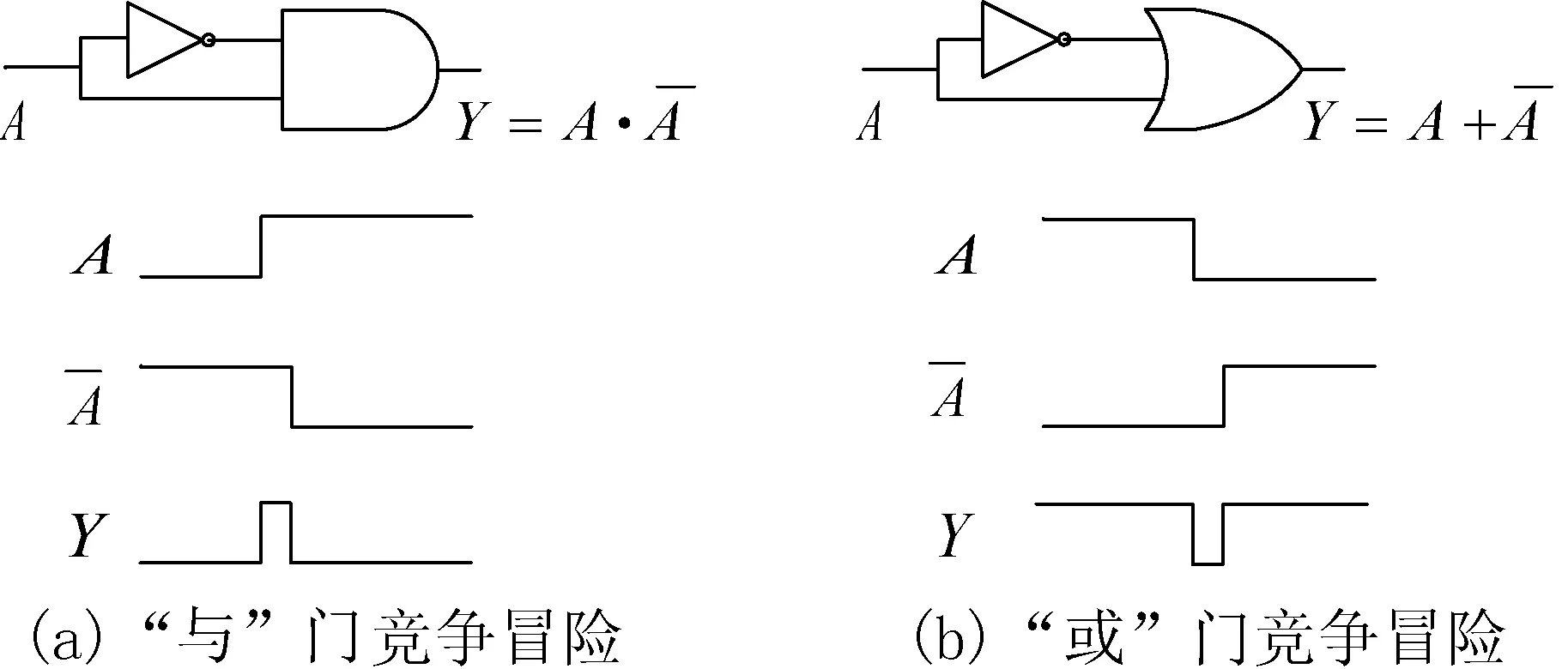

组合逻辑电路的毛刺主要是由竞争冒险现象产生的。电路信号在传输过程中,通过门电路和电路连线时会有一定的延时,逻辑翻转也需要一定的转换时间。这使得电路信号在实际电路中传输时,到达逻辑门输入端的时间不同,逻辑的变化也有先后,从而导致电路出现意想不到的尖峰信号,这就是毛刺信号,其产生往往具有非线性特性。

毛刺产生受诸多因素的影响,如温度、电压和噪声等。在不考虑外界因素的影响下,电路本身的特性也会导致毛刺产生。

图1 简单电路竞争冒险现象

对于逻辑组合电路而言,电路信号输入的顺序和传输延时也会影响到电路的输出。如图2所示,信号C到达“与”门的时间不同会使得电路输出结果不同。若C先于A、B到达“与”门,则电路出现狭窄的尖峰脉冲;反之,则电路输出不会产生毛刺信号。因此,实际电路中延时对于毛刺的产生有非常重要的作用。

图2 多输入组合逻辑电路产生毛刺的情况

3 PUF电路设计

3.1 延时调节模块设计

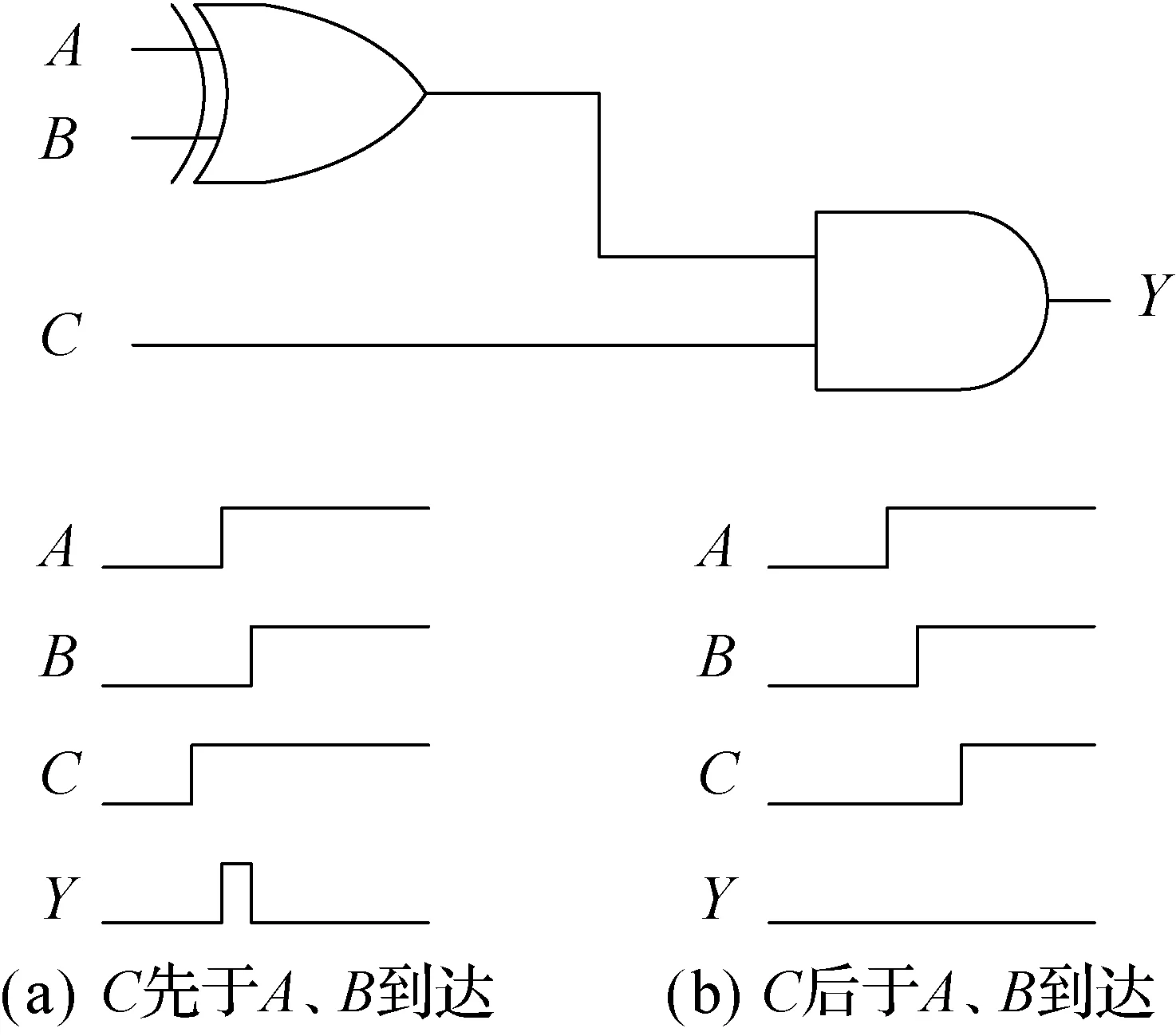

经过前文分析,毛刺的产生与电路延时息息相关。由于传输路径的脉冲过滤限制和逻辑门存在惯性延迟,导致产生的毛刺不一定能全部传递到输出端。只有脉冲宽度大于惯性延迟的毛刺,才可以经由逻辑门输出。因此,为保证良好的电路性能,控制电路毛刺信号的产生是十分重要的。

以“异或”门为例,如图3所示,w为输入信号x1和x2的延时差宽度。当w大于惯性延迟d时,产生的毛刺可以输出;反之,输出端不会输出逻辑1。当w=d时,毛刺波形有50%的概率输出。

图3 “异或”门的惯性延迟影响毛刺输出

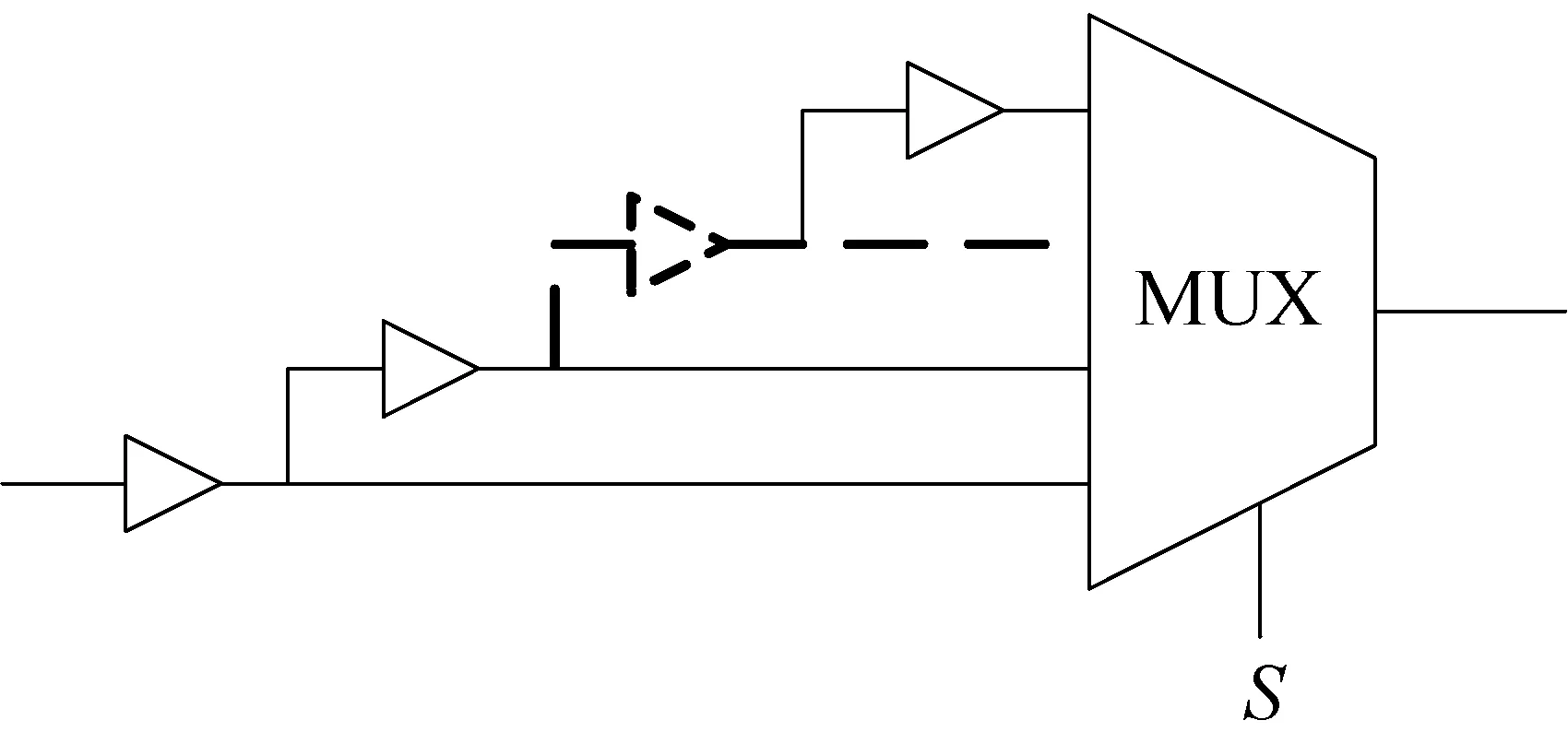

本文在毛刺产生模块的路径上增加延时调节模块,用以改变毛刺的宽度,以期提高电路性能。如图4所示,多路不同数量的缓冲器链连接到多路数据选择器,选择信号S通过数据选择器选择不同的延时路径输出波形。延时调节模块不同路径延时的大小不仅与缓冲器数量有关,而且与器件参数有关。沟道长度和宽度的不同、阈值电压的差别、金属连线等都会使延时大小不同。因此,即使是相同的选择信号,延时也存在差异,使得电路随机性增加。

图4 延时调节模块

3.2 毛刺产生模块

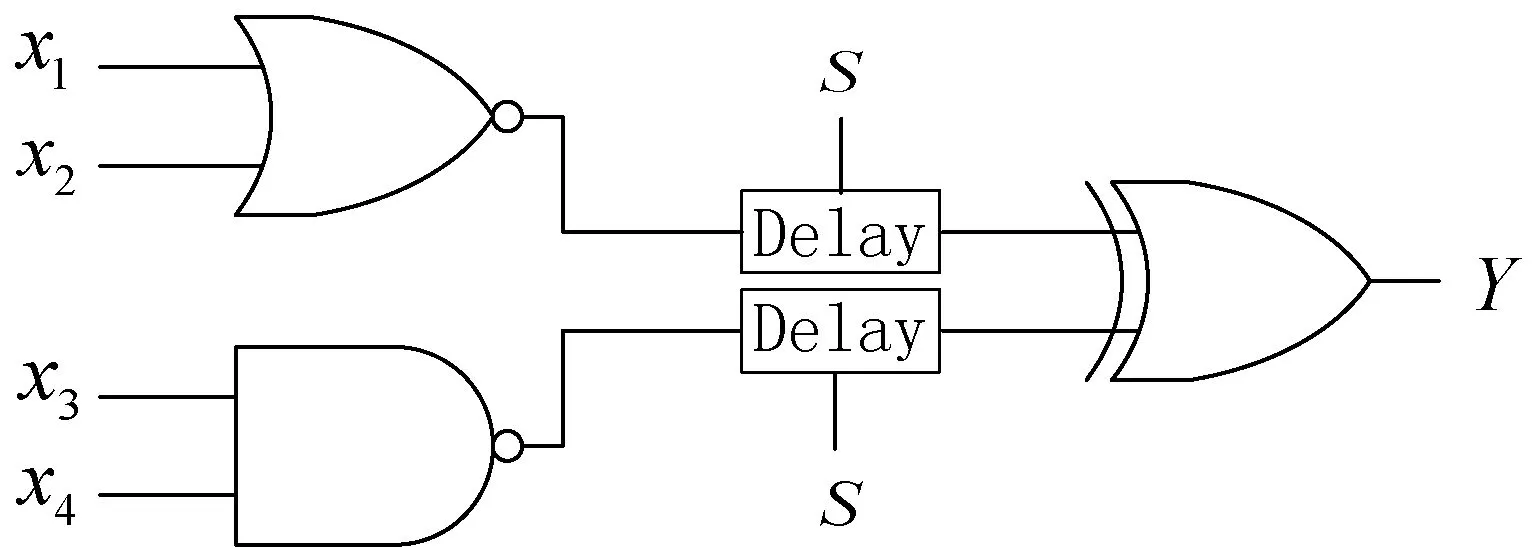

电路的逻辑会影响电路毛刺的产生。本文借鉴竞争冒险电路,采用“与非”门和“非或”门相结合,使用“异或”门输出波形。如图5所示,Delay单元为延时调节模块。本文采用四级延迟,选择信号S[1∶0]用于控制路径的延时。x1、x2、x3、x4为输入信号,Y为输出。通过控制延迟调节模块的选择信号,使得不同路径的延时不同,以此调节信号到达逻辑门的先后顺序,控制毛刺信号的宽度。

图5 毛刺产生模块

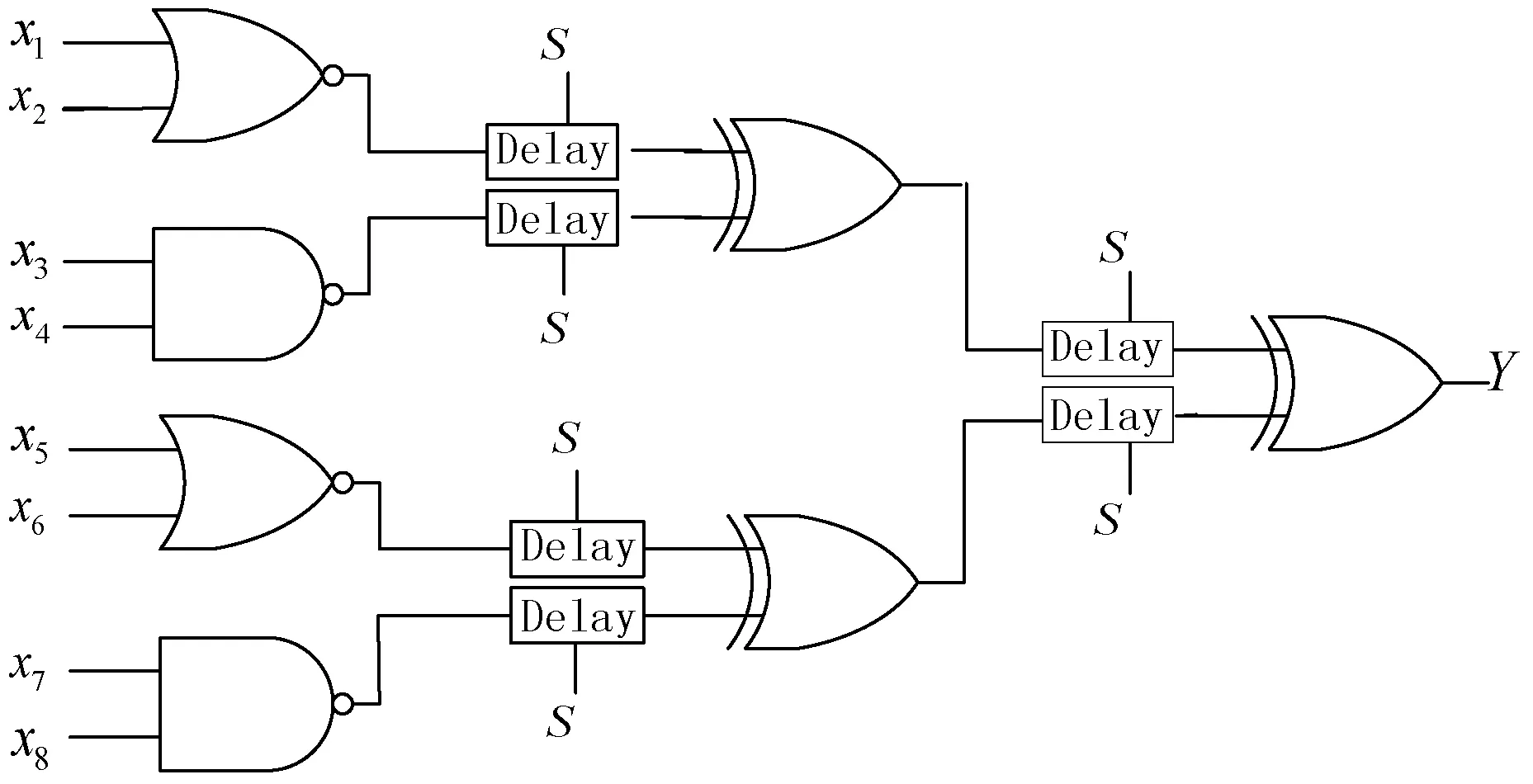

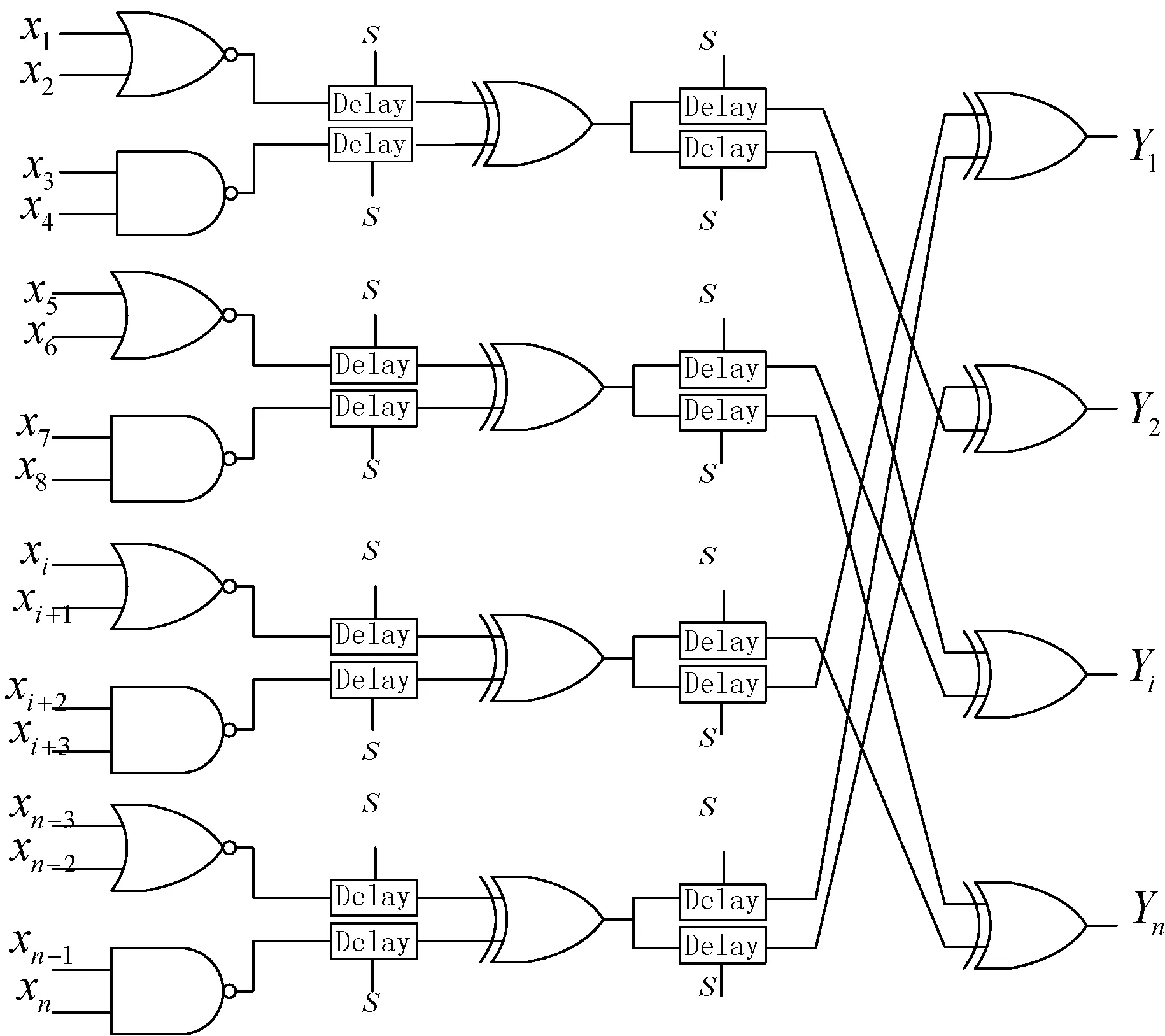

为使得电路产生的毛刺宽度对延迟调节模块更敏感,本文采用“异或”门树网络,如图6所示。电路增加了输入信号的数量,增强了产生毛刺的非线性特性,增加其抗建模攻击属性。延迟调节模块选择不同的延迟大小,使得信号到达“异或”门的时间不同,对毛刺的产生和能否传递到输出端有重要影响。

图6 延时敏感型毛刺产生模块

3.3 采样模块

当毛刺产生模块输出波形后,需要采样电路将波形转化为响应比特位。如何在极短时间内准确采样产生的脉冲信号并输出响应是Glitch PUF电路设计的关键。最普遍的思想就是提高时钟采样精度,使用多相位时钟采集波形,但这样做会使得电路资源消耗增大。

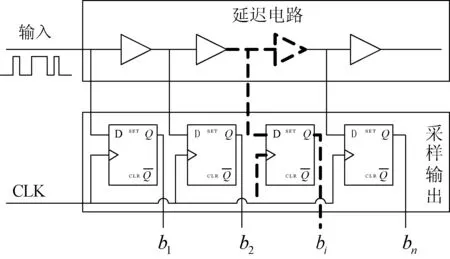

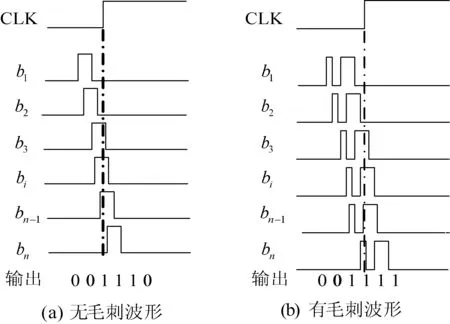

文献[9]与文献[10]采用了相同的采样电路,如图7所示。信号波形输入后,通过缓冲器对波形延时传递,使用D触发器采样不同时刻的波形并输出逻辑值。电路存在毛刺波形与无毛刺波形相比,输出位bi会有所不同,如图8所示。虽然这样的采集方案减少了时钟线的资源消耗,但为了保证有效的采样精度,增加了缓冲器和D触发器的数量,使电路资源消耗也增多。

图7 延迟采样电路

图8 不同波形下的采样结果

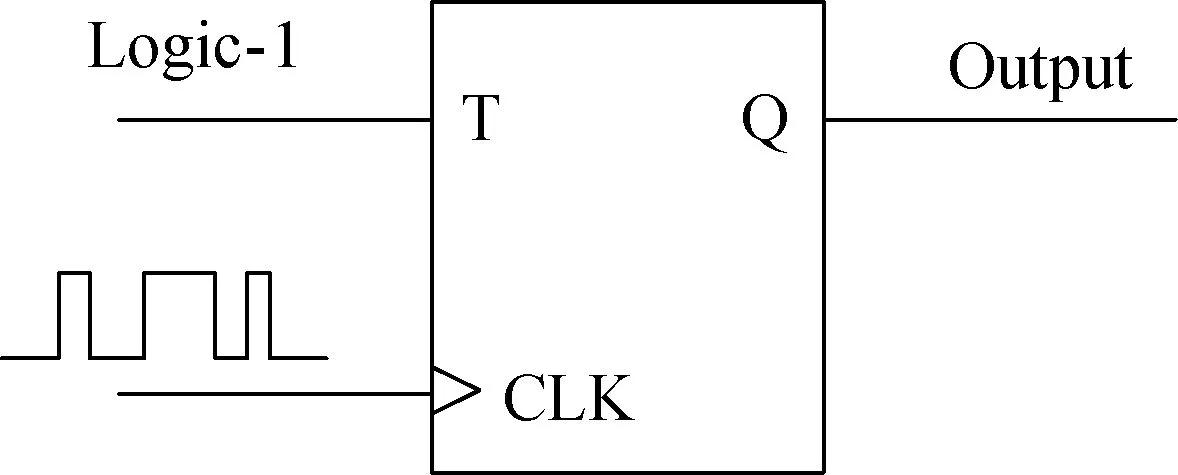

不同于文献[9-10]提出的通过使用延时电路采样信号波形的思想,本文提出利用波形产生毛刺数量的奇偶性来判决生成响应值,使用T触发器采样毛刺产生模块电路的输出。

T触发器输入端置“1”,输出波形连接至T触发器时钟端,Q端输出,如图9所示。当波形有偶数个上升沿时,Q端输出为“1”,反之,输出为“0”。当毛刺产生模块输出的毛刺信号过窄或峰值过低,不足以使得触发器输出翻转时,电路输出不变。在实际电路运行过程中,难免会出现错误翻转的情况,T触发器采样使得电路错误翻转次数为偶数次时,并不会改变电路的输出,这增加了电路的鲁棒性。

图9 T触发器采样电路

3.4 电路架构

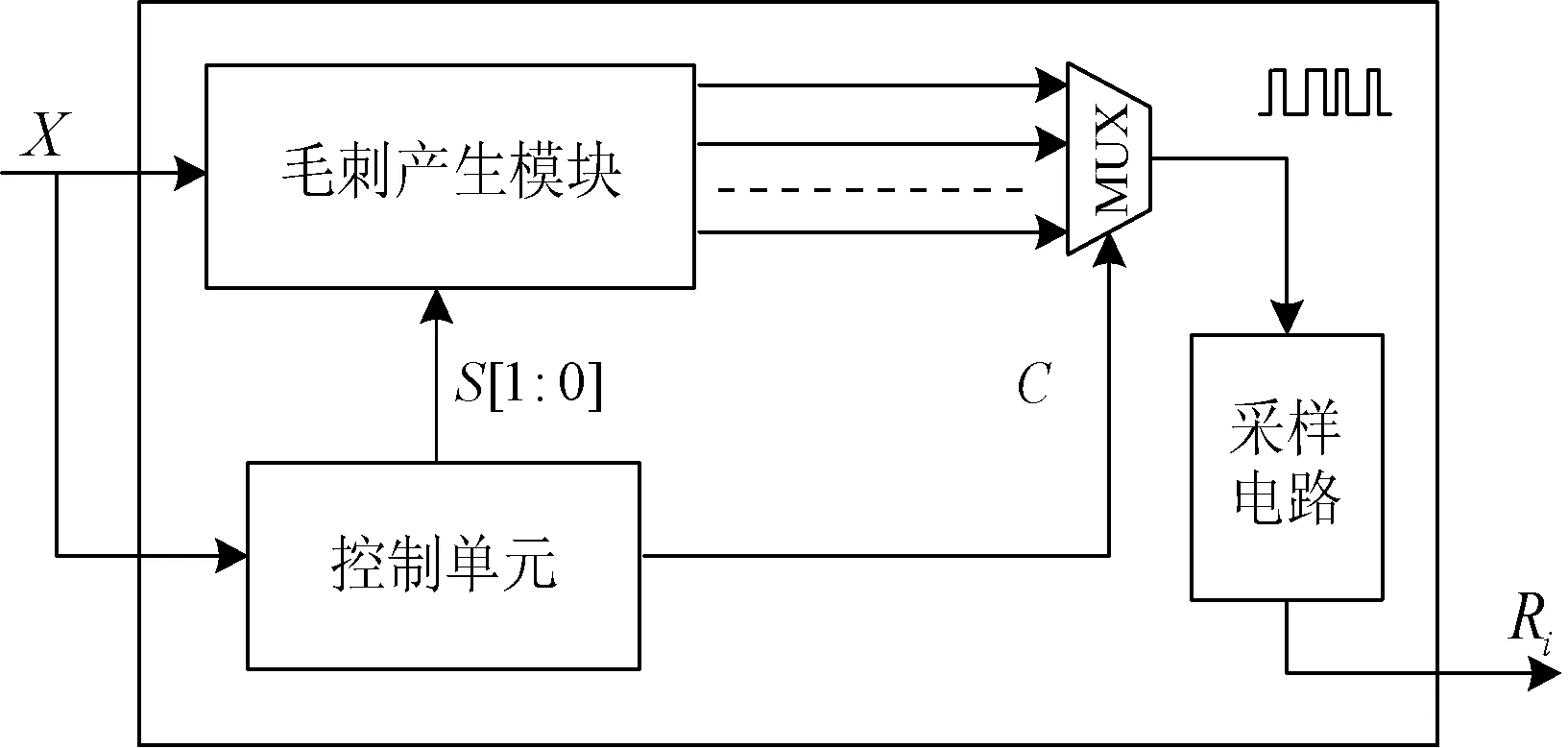

Glitch PUF电路的架构如图10所示。通过控制单元发出的S[1∶0]控制毛刺产生模块中延迟调节模块的延迟大小,C通过数据选择器选择不同的毛刺波形输入到采样电路,采样电路输出单比特响应。

图10 电路架构

为节约资源且增加电路的随机性,本文在单比特响应电路的基础上,设计多比特Glitch PUF输出电路结构,如图11所示。每增加一个单比特响应电路可增加一位输出。采用循环输入方式,将单比特电路不同的输出结果经由“异或”门输出。可在每个输出后接一个采样T触发器,有N个毛刺产生模块,则可产生N比特不同的输出。

图11 多比特响应电路结构

不同于Anderson PUF的单元电路静态输出,本文提出的电路架构可实现动态输出。随着输入信号和控制信号的变化,输出随之改变,可增强电路的随机性和安全性。

4 实验结果

4.1 电路输入与毛刺波形

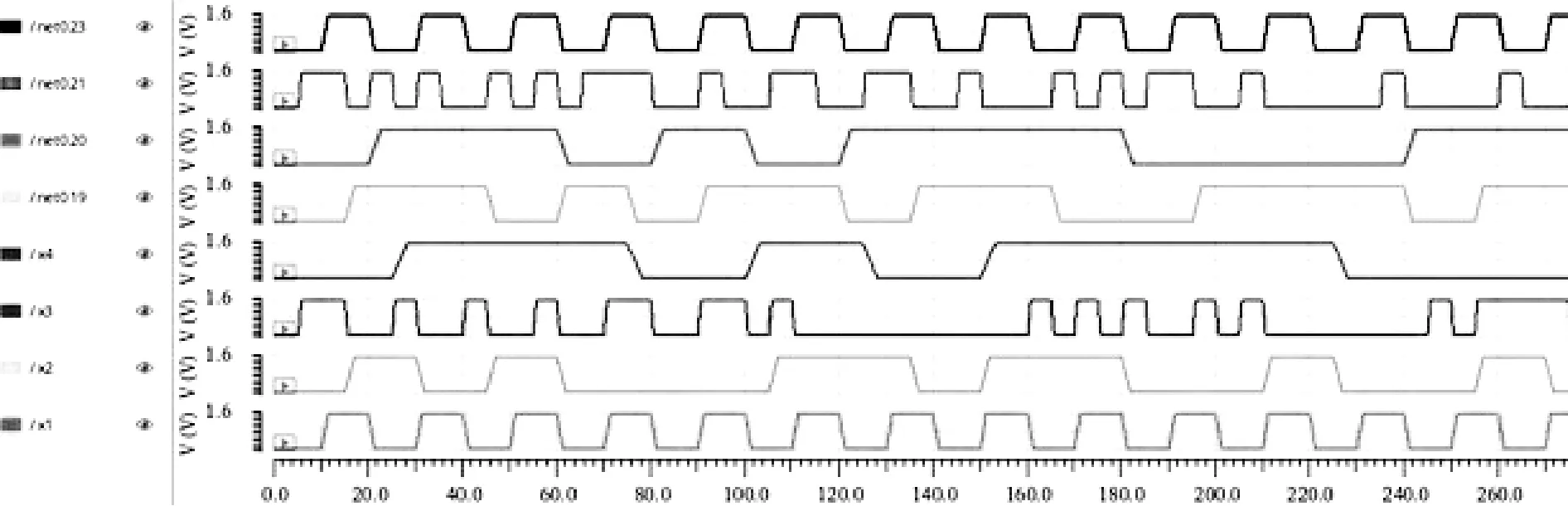

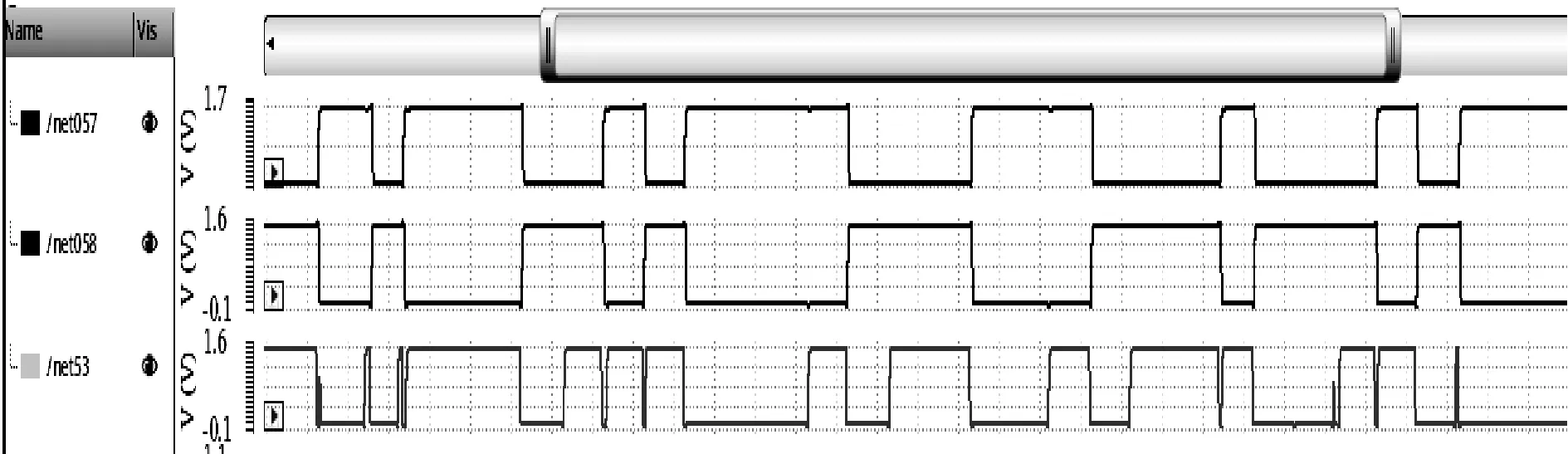

本文采用TSMC 65 nm CMOS工艺库,使用Monte Carlo仿真验证所设计的Glitch PUF电路性能。毛刺产生模块的输入采用伪随机数发生器随机生成xi,如图12所示。通过设置不同的选择信号S[1∶0],使得路径延迟不同。图13为一个毛刺产生模块的输出波形与采样电路输出波形。由实验可知,在输入xi不同时,电路会产生意想不到的尖峰脉冲,而这些尖峰脉冲的出现,使得输出结果出现变化。但并不是所有的尖峰脉冲都会引起输出结果的改变,有些尖峰脉冲的宽度很小或者峰值很低,并不会引起结果的改变。

图12 毛刺产生模块的输入

图13 毛刺波形与采样结果波形

4.2 Monte Carlo仿真

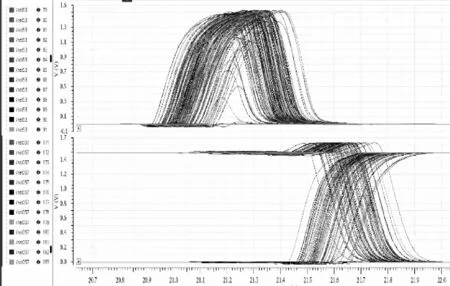

本文在环境温度为27 ℃时,对电路Monte Carlo仿真200次,毛刺波形如图14所示。可以看出,毛刺的宽度和峰值不完全一致。在仿真过程中,电路的采样结果会随着毛刺波形的改变而改变。

图14 Monte Carlo仿真结果

电路不采用延迟模块的结果显示,有125次仿真结果使得采样电路的输出为逻辑0,这表示在实际电路制作过程中,所设计的毛刺产生模块的唯一性为62.5%。多次实验显示,将两条路径的延迟差增大时,产生逻辑0数量减小,最小数目为103次,电路唯一性达到48.5%。

PUF电路在运行过程中会受到温度变化的影响。为验证电路的稳定性,通过Parametric Analysis将仿真温度区间设置为-40~85 ℃,每隔1 ℃仿真一次,共仿真126次。结果显示,有18次仿真波形出现错误翻转,其中有7次波形翻转了偶数次,导致输出结果未发生变化。因此电路在温度区间[-40,85]的稳定性为91.3%。在温度区间[-10,70]有3次波形发生翻转,电路的稳定性为96.3%。

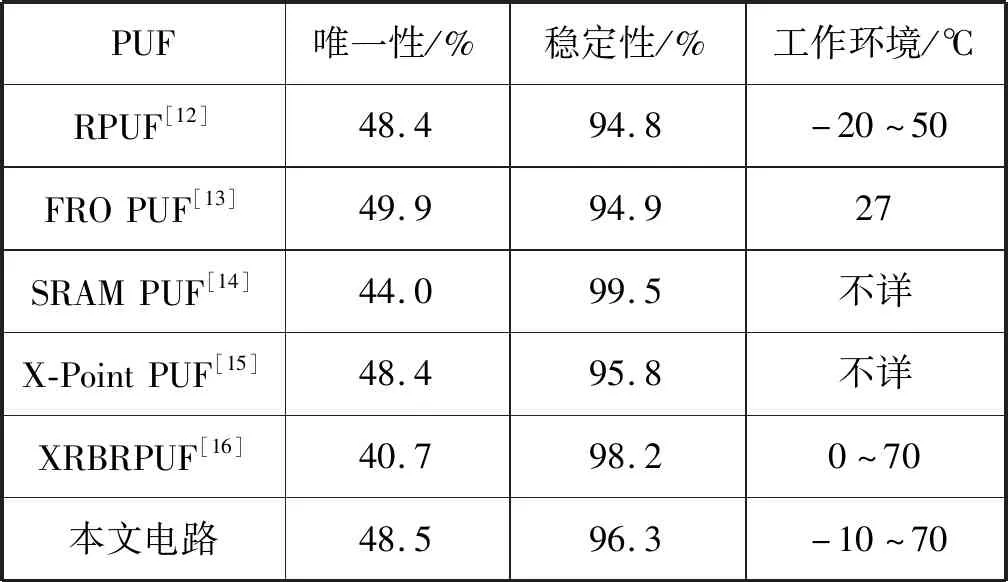

基于延时控制的Glitch PUF与其他相关论文结果对比如表1所示。可以看出,基于延时控制的Glitch PUF的唯一性仅次于FRO PUF,但FRO PUF的唯一性仅是在27℃时测量,且采用了精细的延迟配置线来提升性能。在稳定性方面,本文PUF与其他PUF基本持平,但其采样的温度范围更大,更贴近电路的实际使用环境。因此,本文所设计的DC-Glitch PUF具有良好的唯一性和稳定性,有较高的应用价值。

表1 不同PUF性能对比

5 结 语

本文设计了一种基于延时控制的Glitch PUF电路。通过毛刺产生模块、延时调节模块、T触发器采样电路等,控制电路路径延时,调节毛刺生成宽度,实现数据的比特输出。在TSMC 65 nm CMOS工艺下,使用Cadence验证设计的电路逻辑功能正确,Monte Carlo仿真结果显示电路具有良好的唯一性和稳定性。基于延时控制的Glitch PUF电路利用生成毛刺的非线性特性,可以抵御建模攻击的威胁,可应用于信息安全领域。