宽带扩频信号的并行结构捕获设计

2020-11-11王丽韫

王丽韫

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081 )

0 引言

扩频通信由于抗干扰能力强、可以在强噪声环境下进行通信、功率谱密度低、具有隐蔽性和低的截获率等优点[1],因而获得了广泛的应用。常用扩频信号伪码速率不超过10 Mcps,信号带宽较窄,随着飞行器通信频段由传统的L,S频段向更高的Ku,Ka 频段迈进,带宽达数百兆赫兹的宽带扩频体制逐步得到应用[2]。

同窄带扩频信号相比,宽带扩频信号带宽更宽,AD采样速率要求高达数百兆赫兹甚至上吉赫兹,受硬件工作速度的限制,直接进行高速率的信号处理是不可能的,需采用并行处理算法降低对器件工作速度的要求。对于宽带扩频信号的接收处理,在下变频、匹配滤波[3]及解扩等方面需要采用并行结构的处理算法,本文设计了一种基于FFT并行处理结构的伪码捕获算法,使得数字处理速率在硬件可承受的时钟频率范围,并且研究了该算法的抗噪声性能。

1 宽带扩频信号中频接收处理

1.1 直接中频采样和免混频正交数字下变频

此时本地载波信号的取值实际上是:1,0,-1,0,1,这样混频器就可以避免复杂的振荡器和乘法器,而用简单的组合逻辑和取反电路实现[5]。

1.2 高速采样数据并行频域匹配滤波

免混频形式的正交下变频混频后进行并行匹配滤波,匹配滤波器通常采用有限冲激响应(FIR)滤波器,滤波需要计算FIR 滤波器h(n)和信号序列x(n)的线性卷积,为提高运算速度,用FFT计算线性卷积。由于两个序列的循环卷积与其各自离散傅里叶变换的乘积相对应[6],即yi(n)=xi(n)⊗h(n)与Y(k)=X(k)H(k)具有一一对应关系。需要找到循环卷积与线性卷积相等的条件,设FIR 滤波器h(n)的长度为N1,信号序列x(n)的长度为N2,循环卷积等于线性卷积的条件是N≥N1+N2-1。为了得到正确的没有混叠的循环卷积,需要对序列h(n),x(n) 加长到N点,N=N1+N2-1,加长的部分以零补充。实际应用中将输入信号序列进行分段处理,而且每一段的卷积输出按适当方式衔接在一起,以构成正确的滤波序列输出。假设将序列x(n) 分成为长度N的小段,滤波器h(n)仍然不变,它的长度为N1,且N>N1。若用N点离散傅里叶变换进行处理,则循环卷积的结果前N1-1 点是混叠的,必须舍弃。为了得到正确的结果,分段时在第i段和第i+ 1 段之间插入N1-1 个重复的信号采样点,也就是说,每一段信号均由N2(即N2=N-N1+1) 个点的新数据序列和前一段保存下来的N1-1 个点的旧数据序列组成,这就是所谓的重叠保存法。利用FFT运算求得yi(n)=xi(n)⊗h(n)再舍弃yi(n) 的前N1-1,最后将剩下的yi(n) 顺序地连接起来,得到正确的输出序列y(n) 。取N1=17/N2=16/N=32的组合情况,N1-1=N2=16,便于输入序列重叠保存分段处理。由于所设计的FIR滤波器序列M=[(N1-1)/2]具有线性相位特性且为偶对称,由M=[(N1-1)/2]可得到:

其中,M=[(N1-1)/2]表示取不大于(N1-1)/2的最大整数。也就是说FIR 滤波器有N1=17个采样周期的延迟[7]。在此N1=17,因此FIR 滤波器延迟时间为8 个采样点。把FIR 的8 个采样延迟等效到IFFT 输出端,即取IFFT 中间16 个采样点作为匹配滤波器的线性卷积输出,正好抵消匹配滤波器8个采样点的群延迟。匹配滤波如图1所示。

图1 32点FFT/IFFT匹配滤波器实现结构Fig.1 Implementation framework of 32 point FFT/IFFT matched filter

2 基于FFT的并行处理结构伪码捕获算法

经过频域匹配滤波后得到基带并行数据,然后在并行结构上进行伪码捕获,将接收基带信号与本地伪码进行相关计算,如果序列较大,直接计算相关值运算量非常大,如果把相关表示为DFT的形式,则可用FFT来有效计算相关,运算量大幅减少,运算时间变短。频域计算相关的原理简述如下:

设x(t)和y(t)为两个时间函数,x(n)和y(n)分别为其等间隔采样序列,序列长度为N。X(k),Y(k)分别为x(n),y(n)的N点离散傅里叶变换,设Z(k)=X(k)Y*(k),则[8-9]

由于

图2给出了利用FFT伪码捕获方法的原理图。

图2 FFT伪码捕获方法的原理图Fig.2 Elementary diagram of an algorithm of pseudorandom code acquisition FFT-based

3 仿真结果

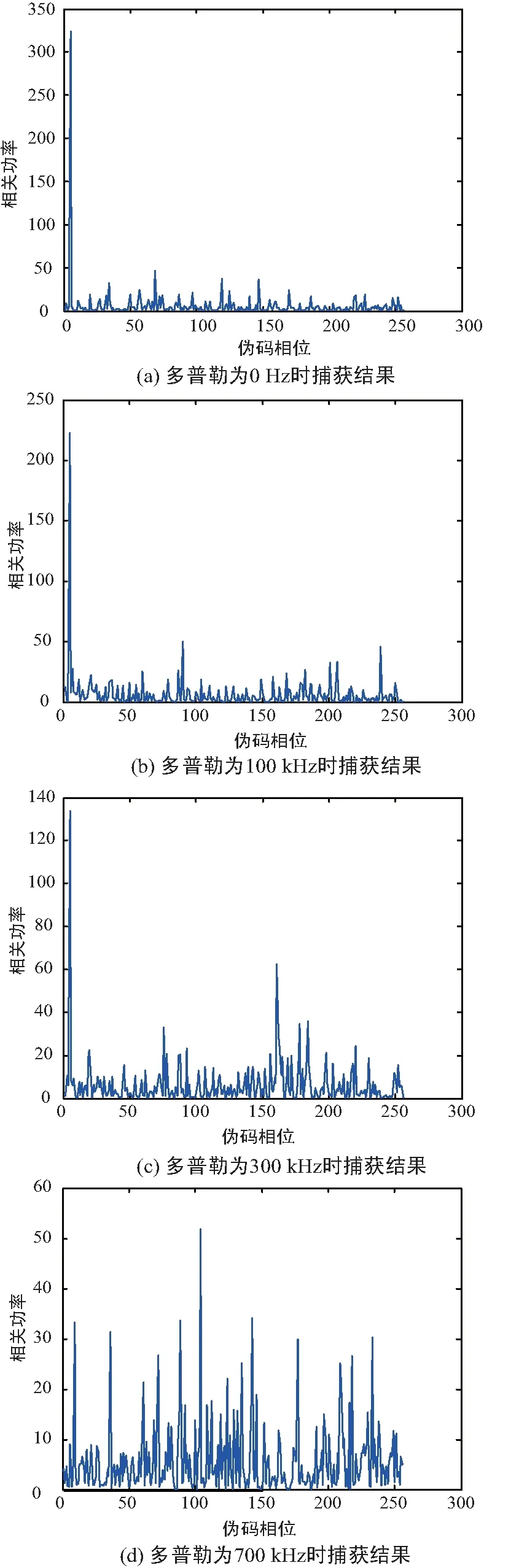

用Matlab软件仿真了FFT伪码捕获算法,本实验选择的伪码长度为256,FFT点数取256点,Eb/N0=14 dB,图3的(a)~(d)分别为多普勒为0 Hz,100 kHz,300 kHz,700 kHz的捕获结果。

由于研究的扩频信号码速率较高,达到180 Mbit/s,为了改善频谱特性,提高信道的频带利用率,加了成型滤波,要求采样率是码片速率Rc的4倍,即720 MHz。用Matlab软件仿真FFT伪码捕获算法的性能,当采样率为4倍码速率,即fs=4Rc时,FFT点数为1 024时,不同信噪比下的捕获概率如表1所示。

表1 采样率fs=4Rc的捕获概率Tab.1 Acquisition probability with sampling frequency fs=4Rc

对于180 Mbit/s码速率,4倍码速率的采样率为720 MHz,在FPGA中无法直接处理,把16路基带并行数据抽取其中4路,每一路采样率180 MHz,也就是每个码片1个采样点,4路采样数据分别进行FFT伪码捕获,FFT点数为256点时,输出4路时域相关值,把4路时域相关值累加,用这种方法仿真伪码捕获性能,得到在不同信噪比下的捕获概率如表2所示。

图3 FFT伪码捕获算法得到的时域相关结果Fig.3 Correlated result of an algorithm of pseudorandom code acquisition FFT-based

表2 采样率fs=Rc,4路相加的捕获概率Tab.2 Acquisition probability with sampling frequency fs=Rc,and add operation for four signals

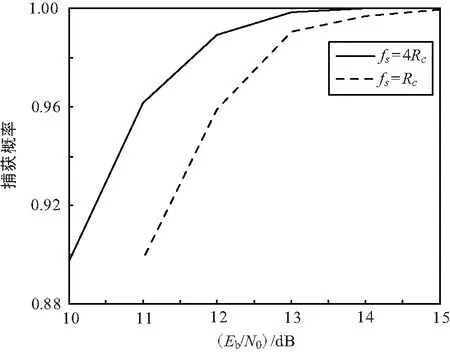

比较表1和表2的仿真结果,采样率fs=Rc,4路时域值相加方法比采样率fs=4Rc的捕获性能恶化约1 dB,但是由于采用4路并行处理,降低了数字信号处理的速率,解决了宽带扩频信号捕获的硬件处理速度难题。图4为两种捕获算法的性能仿真图。

图4 两种伪码捕获算法的性能Fig.4 Performance of the two algorithms of pseudorandom code acquisition

以上分析是FFT伪码捕获算法的基本性能,对于实际系统,为了提高接收机的灵敏度,需要加纠错编码。本文的研究环境是加卷积编码,编码后要求解调门限Eb/N0=5 dB,FFT伪码捕获算法的捕获门限远远不能满足解调门限,在此采用一种把IFFT输出的时域相关值进行非相干累积的方法来改善伪码捕获算法的性能[12-16]。每进行一次FFT伪码捕获,输出N点IFFT的结果,也就是接收基带信号与本地伪码N个相位的相关值,非相干累积是把若干次对应相位的相关值进行累积,以获得更好的抗噪声性能。由于每一次捕获输出N个相关值,为了和下一次捕获输出的N个对应位置的相关值累积,需要把上一次捕获的时域相关值写入RAM中进行储存,等到下一次IFFT运算时,每输出一个时域相关值,把RAM中存储的相应位置的相关值读出进行累加,累加结果再存入RAM,与之后做的IFFT运算的输出结果继续进行累积,直至累积到适当的次数,满足加纠错编码后的解调门限时的捕获性能。累积次数越多,捕获的抗噪声性能越好,但是累积次数越多,捕获时间就会增加,设计中采用满足捕获性能时尽可能少的非相干累积次数。

分别对10次非相干累积、12次非相干累积、16次非相干累积的捕获性能进行了仿真。图5为FFT伪码捕获算法加非相干累积的捕获性能仿真图。可见,非相干累积提高了FFT伪码捕获算法的抗噪声性能,累积次数越多,捕获的抗噪声性能越好。信噪比提高的幅度约为10lgN,N为累积次数。

图5 FFT伪码捕获算法加非相干累积的捕获性能Fig.5 Performance of the algorithm of pseudorandom code acquisition FFT-based with irrelevant accumulation

在并行结构上采用基于FFT的算法完成伪码捕获后,得到本地伪码与接收基带信号相关峰值的相位,根据此相位信息产生本地伪码,每个码片4个采样点,采样率720 MHz,本地伪码产生是4路并行数据,然后进行基带信号与本地伪码的并行相关解扩。

4 结束语

本文设计了一种宽带扩频信号基于并行处理结构的伪码捕获算法,采用并行结构进行下变频与匹配滤波,提出并行采样数据分别进行FFT伪码捕获,输出各路时域相关值,把各路时域相关值相加,从而实现宽带扩频信号的伪码捕获。仿真结果表明这种方法比直接高速采样串行处理性能相差约1 dB,但是处理速率降低4倍,解决了宽带扩频信号捕获的硬件处理速度难题;为了满足加纠错编码后解调门限时的捕获性能,采用将IFFT输出的对应相位的时域相关值进行非相干累积的方法。研究结果表明,这种方法能够实现宽带扩频信号的快速捕获,而且显著提高了FFT伪码捕获算法的抗噪声性能,累积次数越多,捕获的抗噪声性能越好,但是累积次数越多,捕获时间就会增加,因此设计中应折中考虑满足捕获性能和捕获时间的要求。