栅极坡度角对TFT器件制程的影响

2020-11-05黄中浩高坤坤田茂坤闵泰烨冯家海

刘 丹, 刘 毅, 黄中浩, 高坤坤, 吴 旭, 田茂坤, 王 恺,张 超, 王 瑞, 闵泰烨, 冯家海, 方 亮

(1. 重庆京东方光电科技有限公司,重庆 400700; 2. 重庆大学 物理学院,重庆 400044; 3. 中国科学院 重庆绿色智能技术研究院,重庆 400714)

1 引 言

薄膜晶体管液晶显示器(Thin Film Transistor-Liquid Crystal Display,TFT-LCD)因其色彩逼真、画质清晰、轻薄节能等优点,取代了CRT显示器。经过近十几年的发展,TFT-LCD在显示技术中占据了重要地位,可对应大、中、小各型尺寸显示。随着显示技术的不断发展,近些年出现了有机发光二极管(Organic Light Emitting Diode, OLED)、量子点发光二极管(Quantum Light Emitting Diode, QLED)、Mini-LED、Micro-LED等新型显示技术。OLED具有响应快、轻薄、柔性化等特点,将逐步发展成为主流显示技术。但OLED对环境敏感,可靠性差,制程良率低,且制造成本高,目前该技术适用于中小型尺寸显示。由此可以预见,在未来的一段时期,TFT-LCD将和OLED共存,二者相互竞争发展[1-3]。QLED显示属于电致发光,其器件的结构与OLED类似,最大的区别在于OLED的有机发光层是有机材料,而QLED的发光层是无机材料。无机材料的可靠性优于有机材料,理论上QLED有着更好的环境适应性。QLED技术目前还处于研发阶段,未量产。Mini-LED和Miro-LED属于LED型显示,Mirco-LED的像素更小,技术难度更大。Mini-LED目前已经商业化,Micro-LED预计在未来2~5年实现商业化[3]。新型显示技术也同TFT-LCD进行交叉融合,进一步提升TFT-LCD显示性能。QLED技术已应用于TFT-LCD的背光源,该技术与LED背光源相比,可提供更纯的三基色,使得显示的颜色更真实,色域更广阔。三星、TCL已经推出QLED背光源电视。Mini-LED技术同样可以应用于TFT-LCD的背光源,Mini-LED背光源可实现局部调光,使TFT-LCD达到OLED的显示效果[2-3]。

重庆京东方生产的高开口率高级超维场转化型液晶显示器(High aperture advanced super dimensional switching, HADS)用于笔记本电脑。HADS产品的TFT属于底栅结构,其制程依次是:栅极(Gate)、非晶硅层(Active)、像素电极(PXL ITO)、源极和漏极(Source和Drain,SD电极)、钝化层(Passivation,PVX)、公共电极(Common ITO),共经历6次光刻[4]。栅极依次采用磁控溅射成膜、光刻、湿法刻蚀制得,栅极在截面方向形成梯形状台阶,有坡度角(Profile),坡度角受膜厚、光刻、刻蚀等参数的影响[5]。栅极和有源层之间覆盖着栅极绝缘层(Gate Insulator,GI层),GI层由SiNx构成,其采用化学气相沉积(Chemical Vapor Deposition,CVD)方法制得。覆盖在栅极台阶处的SiNx,沿水平方向有着厚度,沿着竖直方向也有厚度,水平方向的厚度与竖直方向厚度的比值为台阶覆盖率(Step Coverage,栅极坡度角处水平方向绝缘层厚度与竖直方向绝缘层厚度之比)[6]。如果栅极的台阶覆盖率偏低,意味着栅极台阶处水平方向的GI层较薄,在此方向可能有短路的风险,进而导致产品良率下降。在栅极坡度角不变的情况下,可以通过调整CVD工艺制程参数的调整来获得较大的台阶覆盖率,进而规避风险[6-8]。然而,随着工艺数的变化,栅极坡度角会发生变化[5],栅极坡度角对GI层台阶覆盖率的影响以及该影响与后续制程、产品良率的关系却未见报道。

本文结合重庆京东方生产的15.6HADS产品的TFT工艺制程,通过工艺的调整获得不同坡度角的栅极,然后将不同坡度角的栅极样品制备成TFT器件。通过此实验,研究了栅极坡度角对GI层台阶覆盖率的影响。在此基础上,明确了栅极坡度角对后续的SD电极刻蚀的影响,推测并证实了栅极坡度角与TFT制程中栅极腐蚀的关系。最后,针对栅极坡度角偏大带来的不利影响提出改善方案。

2 实 验

2.1 实验流程

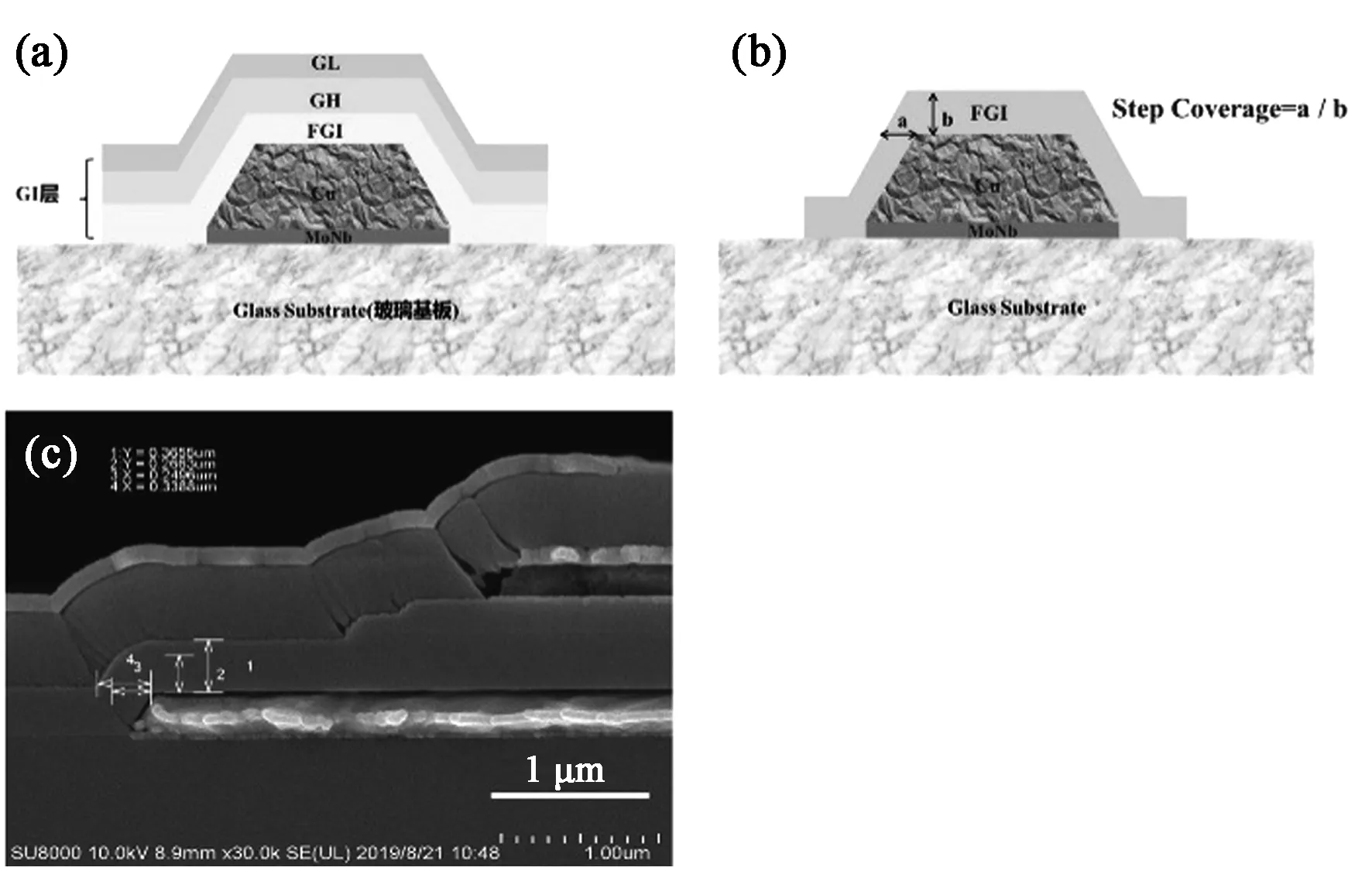

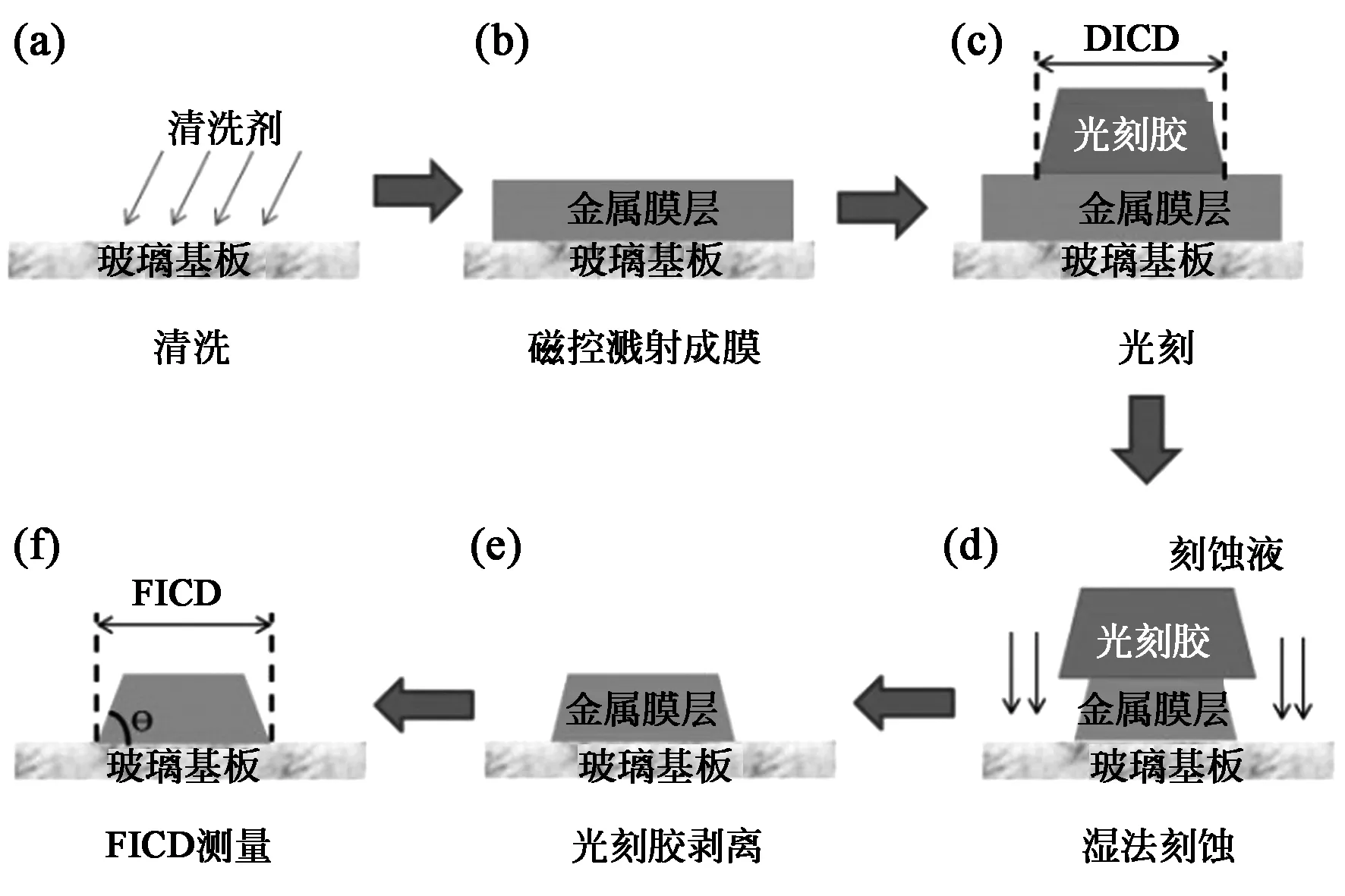

实验在京东方8.5代线的15.6HADS产品的工艺流程中进行,该产品的TFT器件结构和制程顺序如图1所示。在栅极阶段,通过膜厚、刻蚀液种类、刻蚀时间的变化,获得不同坡度角的栅极。将不同栅极坡度角的样品分为A和B两种类型,A类型样品包含了栅极膜厚、坡度角的变化,该类样品随后进行栅极绝缘层(Gate Insulator,GI)成膜。按照工艺制程顺序,GI膜层又可以细分为3层,依次是快速GI膜层(Fast Gate Insulator,FGI)、高速GI膜层(GI in High Speed,GH)、低速GI膜层(GI in low speed,GL)。GL层与a-Si接触,故谢振宇等人将GL层称作栅界面SiNx层[6]。GI分层情况如图2所示。在栅极坡度角位置,FGI在水平和竖直方向的厚度依次为0.249 6 μm和0.266 3 μm,水平厚度与竖直厚度之比为台阶覆盖率,FGI的覆盖率为93.7%。同理,整个GI在该处水平和竖直方向的厚度为0.338 8 μm和0.365 5 μm,对应的覆盖率为92.7%。FGI和GI的覆盖率参数接近,采用FGI的覆盖率反映整个GI的覆盖率。A类样品仅完成FGI成膜,然后对样品进行切片,并采用扫描电子显微镜(Scan Electronic Microscope,SEM)进行微观形貌测试。在截面方向上,采用SEM观察覆盖有FGI膜层的栅极形貌,测试栅极台阶处FGI膜层的水平厚度和竖直厚度,然后换算获得台阶覆盖率数据,以此研究栅极膜厚和坡度角对FGI层台阶覆盖率的影响。B类样品的栅极膜厚相同,只是经历不同的刻蚀液和刻蚀时间,最终导致栅极坡度角不同。B类样品按照15.6HADS产品的工艺流程进行器件制备,在SD电极制备阶段,测试SD膜层经光刻后的光刻胶在台阶处和非台阶处的显影后关键尺寸(Development Inspection Critical Dimension,DICD),然后进行SD刻蚀、光刻胶剥离,再对样品在同样的位置测试电极的最终关键尺寸(Final Inspection Critical Dimension,简称FICD)。在TFT行业,DICD与FICD之差称作Bias或CD Bias,其代表刻蚀程度,该值越大则刻蚀程度越大。对于同一个样品,台阶处和非台阶处的Bias差异代表不同位置的刻蚀程度差异,也即台阶对刻蚀程度的影响;对于不同的样品,栅极坡度角不同,台阶处的Bias差异代表栅极坡度角对台阶处刻蚀影响程度的差异。DICD、FICD与工艺制程的关系如图3所示,台阶处和非台阶处的位置如图4所示,CD1代表台阶位置,下方的CD2代表非台阶位置。

图1 TFT器件结构及制程顺序示意图Fig.1 Diagram of TFT device and process sequence

图2 GI分层(a,b)与覆盖示意图(c)Fig.2 Diagram of GI layer (a,b) and its coverage (c)

图3 DICD和FICD测试在工艺制程中的流程Fig.3 Process flow for measurement of DICD and FICD

图4 SD层关键尺寸测量位置Fig.4 Measuring position of critical dimension for SD layer

完成上述实验,明确栅极坡度角对FGI覆盖性和SD刻蚀差异影响,在此基础上提出栅极坡度角偏大导致GI台阶覆盖恶化,台阶处GI厚度变薄,最终导致腐蚀介质侵入造成栅极腐蚀的假设。将栅极腐蚀样品进行切片,采用SEM进行截面测试,对比腐蚀区域与非腐蚀区域的栅极坡度角差异,对假设进行验证。

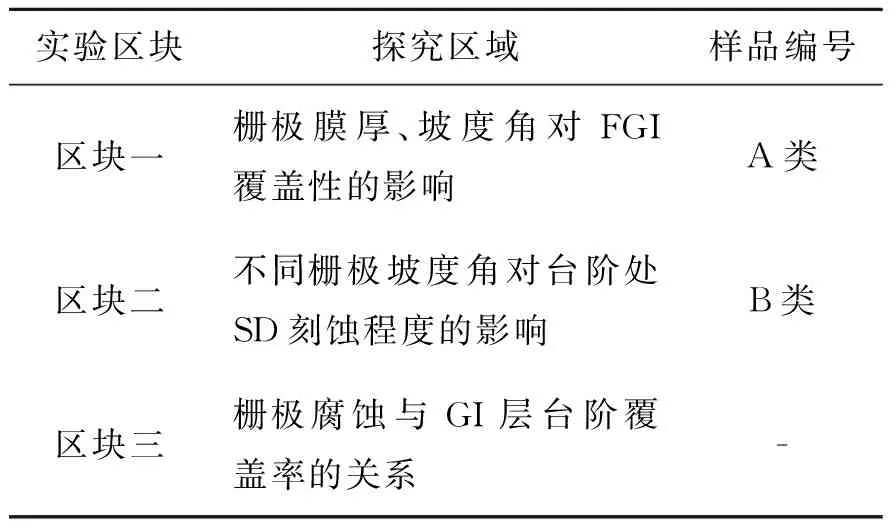

2.2 实验样品

实验共分3部分,如表1所示。对于区块一,通过不同的磁控溅射时间获得栅极膜厚差异,通过变更刻蚀液种类和刻蚀时间获得不同的栅极坡度角。待该组样品完成FGI成膜后,在每个样品上均匀取9个部位,进行SEM测试,用最终的均值反应台阶覆盖率。对于区块二,DICD和FICD,采用TFT产线的HTCD设备进行测试。HTCD设备采用非接触成像与像素分析的技术手段进行测量,每张玻璃基板测试54个点位,并获得54个数据,通过54个数据的平均值反应测试情况。区块三中的样品属于15.6HADS的产品,在实际量产过程中遇到栅极腐蚀的问题,通过重庆京东方的良率管理系统(Yield Management System,YMS)确定腐蚀发生的位置,对这些位置进行标注,并切片取样;同时对未发生栅极腐蚀的位置进行标注并取样;然后对两组样品进行SEM测试,对比栅极坡度角,获得栅极腐蚀与栅极坡度角的关系。

表1 制程实验条件Tab.1 Experiment split of process

3 实验结果及分析

3.1 栅极膜厚和坡度角对GI层台阶覆盖率的影响

栅极是MoNb/Cu复合结构膜层,MoNb作为缓冲层沉积在玻璃基板上,然后Cu再沉积到MoNb上面。MoNb可以增加Cu与玻璃基板的粘附力。当栅极的Cu厚度保持300 nm时,不同栅极坡度角对应FGI膜层台阶覆盖的微观形貌如图5所示,图(a)对应的栅极坡度角比图(b)大,对于台阶位置水平方向上的GI厚度而言,图(b)的水平厚度更大。

图5 FGI覆盖台阶的微观形貌。(a)较大的栅极坡度角;(b)较小的栅极坡度角。Fig.5 Micro-morphology of FGI covering the step. (a) Larger profile; (b)Smaller profile.

在栅极膜厚保持300 nm条件下,栅极坡度角与台阶覆盖率的变化趋势如图6所示。栅极坡度角增加,FGI膜层的台阶覆盖率逐渐下降,且下降的斜率存在阶段性差异,坡度角58°是下降斜率的拐点。如果坡度角不高于58°,台阶覆盖率下降速率快;坡度角高于58°,台阶覆盖率缓慢下降。在坡度角约为55°时,台阶覆盖率接近100%,此时台阶处的FGI膜层水平厚度与竖直厚度持平。

图6 栅极厚度300 nm下坡度角与FGI覆盖率关系Fig.6 Relationship between gate profile and FGI coverage in fixed gate thickness of 300 nm

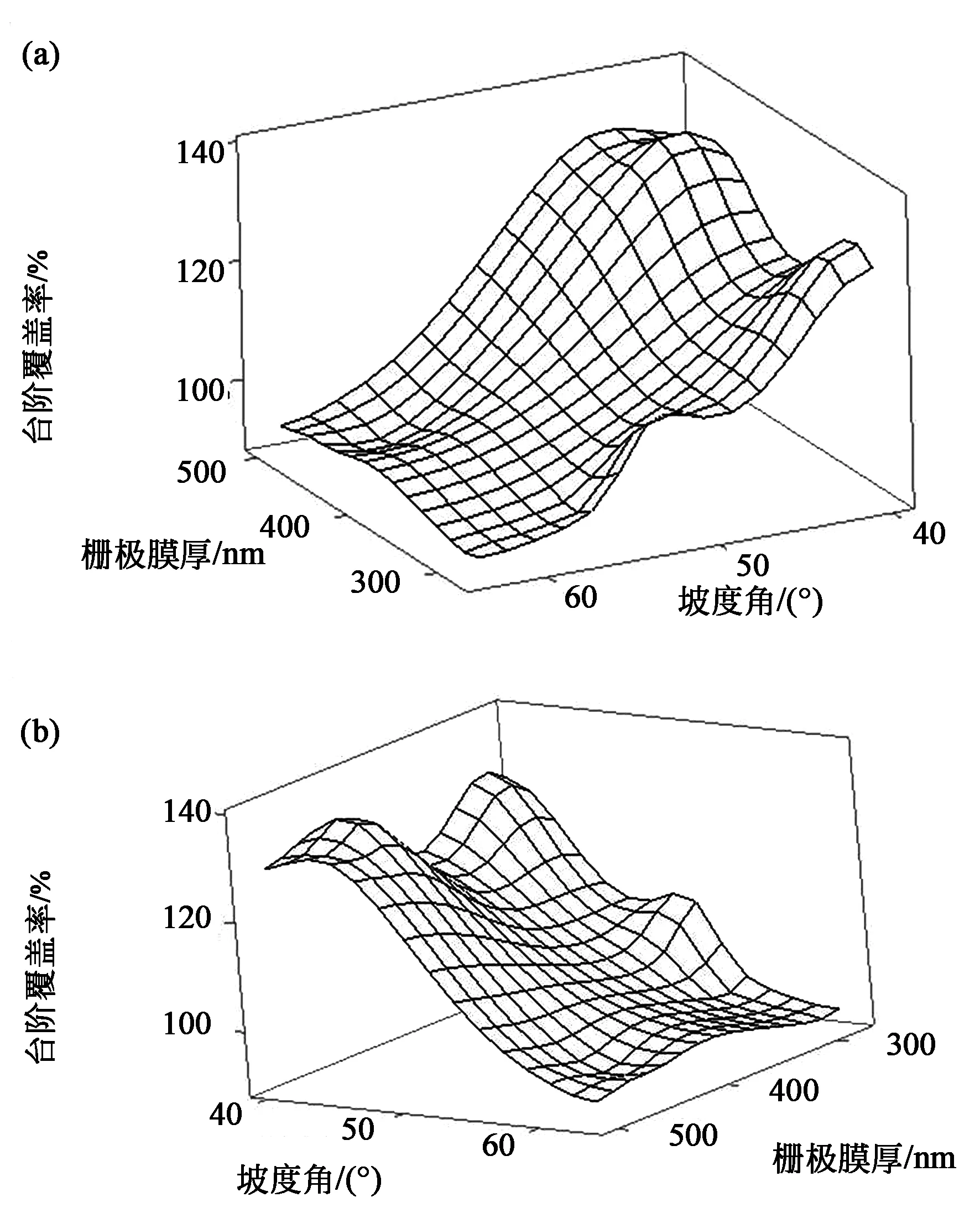

不同栅极膜厚和坡度角样品与FGI层覆盖率对应情况如表2所示。从表中可以看出,当栅极膜厚固定时,栅极坡度角和FGI层覆盖率是负相关关系。将栅极膜厚和坡度角视作自变量,将FGI的覆盖率视作因变量,采用三维做图,情况如图7所示。通过对三维视图进行旋转,可以看出台阶覆盖率随着坡度角的变化而变化,同栅极膜厚并无明显的变化趋势。采用Minitab对上述两个自变量和一个因变量采用主效应分析,明确两个自变量对因变量的影响程度。主效应分析情况如图8所示,可以看出膜厚对FGI覆盖率的影响不超过10%,可以忽略,坡度角的影响程度最大。

表2 不同栅极膜厚、坡度角下的FGI覆盖率Tab.2 FGI coverage in different gate thickness and profile

续 表

图7 不同栅极膜厚(a)、坡度角(b)下FGI覆盖率的三维视图。Fig.7 Three dimension view of FGI coverage in different gate thickness (a) and profile (b)

图8 栅极膜厚、坡度角关于FGI覆盖率的主效应分析。Fig.8 Main effect analysis of gate thickness and profile on FGI coverage

栅极坡度角是影响FGI覆盖率的主要因素,采用线性回归模型对表2中的数据进行分析,并建立单元线性回归模型,情况如图9所示。线性模型可以解释96%的变异,模型有效,该线性模型对栅极膜厚280~500 nm适用。为确保FGI的台阶覆盖率达到100%,将该数值带入图中的方程,计算得到对应的栅极坡度角为58°。为了保证台阶处水平方向上的FGI膜层不减薄,栅极坡度角不应超过58°。

图9 FGI覆盖率关于栅极坡度角的回归方程Fig.9 Regression equation between FGI coverage and gate profile

3.2 栅坡度角对台阶处SD刻蚀的影响

栅极形成台阶,GI层覆盖在栅极上亦形成台阶,SD膜层亦会盖在GI台阶之上。这样,SD层也存在台阶覆盖率,如果台阶的角度偏大,台阶处的SD膜层在水平方向上就会偏薄。该情况如图10所示,竖直方向上的SD膜厚为n,水平方向上的厚度为m。结合图4所示,位置CD1处的SD线下方无台阶,其厚度为n;位置CD3处存在台阶,那么该处的SD膜层在水平方向的厚度为m。

图10 台阶处的SD层覆盖示意图Fig.10 Diagram of SD covering at the step

当台阶坡度角偏大时,台阶处的SD膜层水平厚度m小于竖直厚度n,即SD膜层减薄。当SD膜层减薄之后,在同样的刻蚀条件下,台阶处的刻蚀程度会增加。对于同一个样品,经历的工艺制程相同,同一个样品的台阶与非台阶处的SD CD Bias差异反应出刻蚀程度的差异。如表3所示,在同一个样品前提下,台阶处的SD CD Bias始终大于非台阶处的数值,这表明台阶处的刻蚀程度更大,因同一个样品经历的刻蚀条件一样,可以反推出台阶处的SD膜层因坡度角而减薄了。

表3 台阶处与非台阶处的SD CD Bias情况Tab.3 SD CD Bias at step and non-step position

对于台阶位置处的SD,可以通过降低栅极坡度角的方式减小刻蚀程度。图11所示为不同栅极坡度角对应的台阶处SD CD Bias情况。栅极坡度角分为B4和B5两类,且B4的坡度角为61°,B5坡度角为46°;其中B4类别的样品有3个,B5样品有4个,用B4-1~B4-3表示。B4对应的SD Bias在1.74 μm附近,B5对应的SD Bias比B4样品约小0.1。对于细线化产品(如手机屏幕),因SD线宽度小,台阶处断线(TFT行业称之为step open)发生率高于其他尺寸产品(如笔记本电脑屏幕、电视屏幕)。如果采用变更刻蚀液的方式来降低台阶处断线风险,成本太高;如果不变更刻蚀液而采用降低栅极坡度角的方式降低台阶处的CD Bias,进而规避台阶处断线风险,可提升细线化产品的良率,带来经济收益;同时,台阶处CD Bias降低。这可以使得光刻到刻蚀的等待时间(TFT行业称之为Q-time)适当延长,缓解生产运营的压力。

图11 不同栅极坡度角台阶位置的SD刻蚀程度Fig.11 Etching degree of SD layer at step position for different gate profile

3.3 栅极坡度角与栅极腐蚀的关系

对于TFT器件是Cu电极的产品,在制程中会遇到栅极腐蚀的情况。量产条件下,完成SD电极制程之后进行良率检测(TFT行业称之为Data Test,DT)。当TFT器件制程全部完成后,进行Array Test(AT)。DT检测在AT检测之前进行。如果栅极发生腐蚀,检测中信号加载异常,结合坐标点位便可确定栅极腐蚀发生的位置。对于栅极腐蚀严重的样品,在DT阶段便可检测出来;对于腐蚀相对弱的样品,在AT检测阶段才可检出。

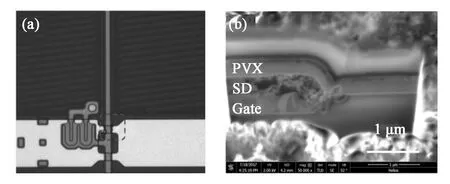

对于量产的某一款产品,在AT阶段检出栅极腐蚀,腐蚀发生的位置如图12所示。图12中,外层最大的矩形代表玻璃基板,也称TFT基板;TFT基板里面的小矩形代表显示屏幕,图中的点代表栅极腐蚀发生的位置。从图中可以看到,栅极腐蚀主要集中在玻璃基板的两侧,而中间位置的栅极腐蚀相对较少。AT检测设备对栅极腐蚀位置的拍图如图13所示,图13(a)中虚线框标注的位置发生栅极腐蚀,且腐蚀发生在台阶处。对腐蚀位置进行FIB测试,如图13(b)所示,栅极形貌不规则,栅极上方的GI层缺失。

图12 TFT基板上栅极腐蚀位置Fig.12 Map of gate corrosion in TFT substrate

图13 栅极腐蚀的检测图片。(a)发生在台阶处的栅极腐蚀;(b)腐蚀位置处的FIB测试。Fig.13 Inspection image of gate corrosion. (a) Gate corrosion at the step; (b) FIB test at the gate corrosion.

对发生栅极腐蚀的样品切片,分别在TFT基板的左、中、右位置取样,然后对3种样品进行SEM测试,测量栅极坡度角,并通过箱线图反应不同位置的栅极坡度角分布。3个位置的栅极坡度角情况如图14所示,可以看到基板的左、右位置处栅极坡度角较大,且部分坡度角已经达到60°;而中间位置的栅极坡度角相对较小,最小的坡度角可达到47°。结合栅极坡度角的分布情况,可以获得这样的结论:栅极坡度角大的位置栅极腐蚀发生率高,栅极坡度角小的位置腐蚀发生率低。

图14 栅极腐蚀样品不同位置的栅极坡度角分布Fig.14 Gate profile distribution at different positions of corrosion samples

对于栅极坡度角偏大与栅极腐蚀的相关关系,推测是GI层微裂纹和Cu扩散所致。如图15所示,当栅极坡度角偏大时,GI膜层覆盖在TFT基板上,台阶处的GI膜厚减薄,且在应力作用下该处的GI层会产生微裂纹,后续制程中伴随着高温工艺制程(如ITO退火、PVX成膜等),裂纹会进一步扩展。后续制程的非晶硅层刻蚀,采用的氯气对Cu有腐蚀作用[9];非晶硅层光刻胶剥离制程的剥离液和H2O均对Cu具有腐蚀作用[10],这些腐蚀介质进入微裂纹并残留在微裂纹中。微裂纹处的GI层更薄,残留的腐蚀介质透过GI层与栅极接触,发生反应。随着工艺制程的进行,微裂纹逐步朝栅极扩展,腐蚀介质逐步与栅极反应,最终造成栅极腐蚀。此外,如果微裂纹扩展至栅极,腐蚀介质将SD电极和栅极连通,形成栅极和SD电极短路(TFT行业称之为Data Gate short,DGS)。这就是栅极腐蚀通常伴随着DGS的原因。

图15 GI层微裂纹和铜扩散示意图Fig.15 Diagram of GI micro-cracks and Cu diffusion

此外,栅极采用Cu材料制得,GI层是SiNx材料,Cu可在SiNx材料中扩散[11-12],在GI成膜的后续制程中,伴随着高温工艺,Cu的扩散程度逐渐加大。如图15中的虚线框所示,栅极台阶处的Cu可向GI层扩散,这会导致GI膜层的有效厚度减小,即对栅极的保护作用减弱;在这种情况下,腐蚀介质就透过减薄GI膜层与栅极接触,形成腐蚀。当然,栅极的Cu扩散造成GI膜层有效厚度减少,使得栅极和SD电极场强增加,有静电击伤(ESD)风险;一旦Cu扩散导致栅极与SD电极导通,就形成短路类型的不良。

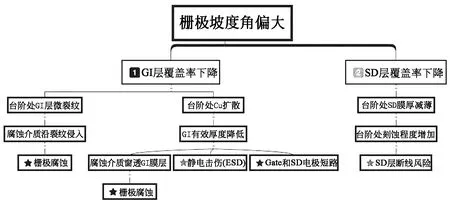

3.4 栅极坡度角偏大对制程影响的汇总

栅极坡度角偏大对工艺制程的影响,结合X-mind思维导图软件将原因、发展过程、逻辑关系、最终的影响等情况采用树状图的形式汇总于图16。栅极坡度角偏大,导致GI层台阶覆盖率下降,可诱发栅极腐蚀、ESD、栅极与SD电极短路等不良。同时,栅极坡度角偏大,形成的台阶造成SD膜层覆盖率偏低,在栅线和SD线交叉的位置容易造成SD线断线。

图16 栅极坡度角对TFT制程影响汇总Fig.16 Influence of gate profile on TFT process

对于GI层台阶覆盖率偏低和SD层覆盖率偏低造成的不良,结合X-mind软件采用逻辑图形式提出解决方案。如图17所示,对于GI层台阶覆盖率偏低,可采用降低栅极坡度角的方法增加其覆盖率:在栅极刻蚀阶段,调整刻蚀液的种类和成分,有效降低栅极坡度角[5,13]。如果栅极坡度角不容易降低,则可以调整GI膜层的成膜参数。GI膜层属于SiNx材料,降低成膜功率、增加基板与CVD设备中电极的间距、调整SiH4/NH3的气体比例,可以获得较大的台阶覆盖率[6]。

图17 GI台阶覆盖率偏低的解决方案Fig.17 Solutions for low step coverage of GI layer

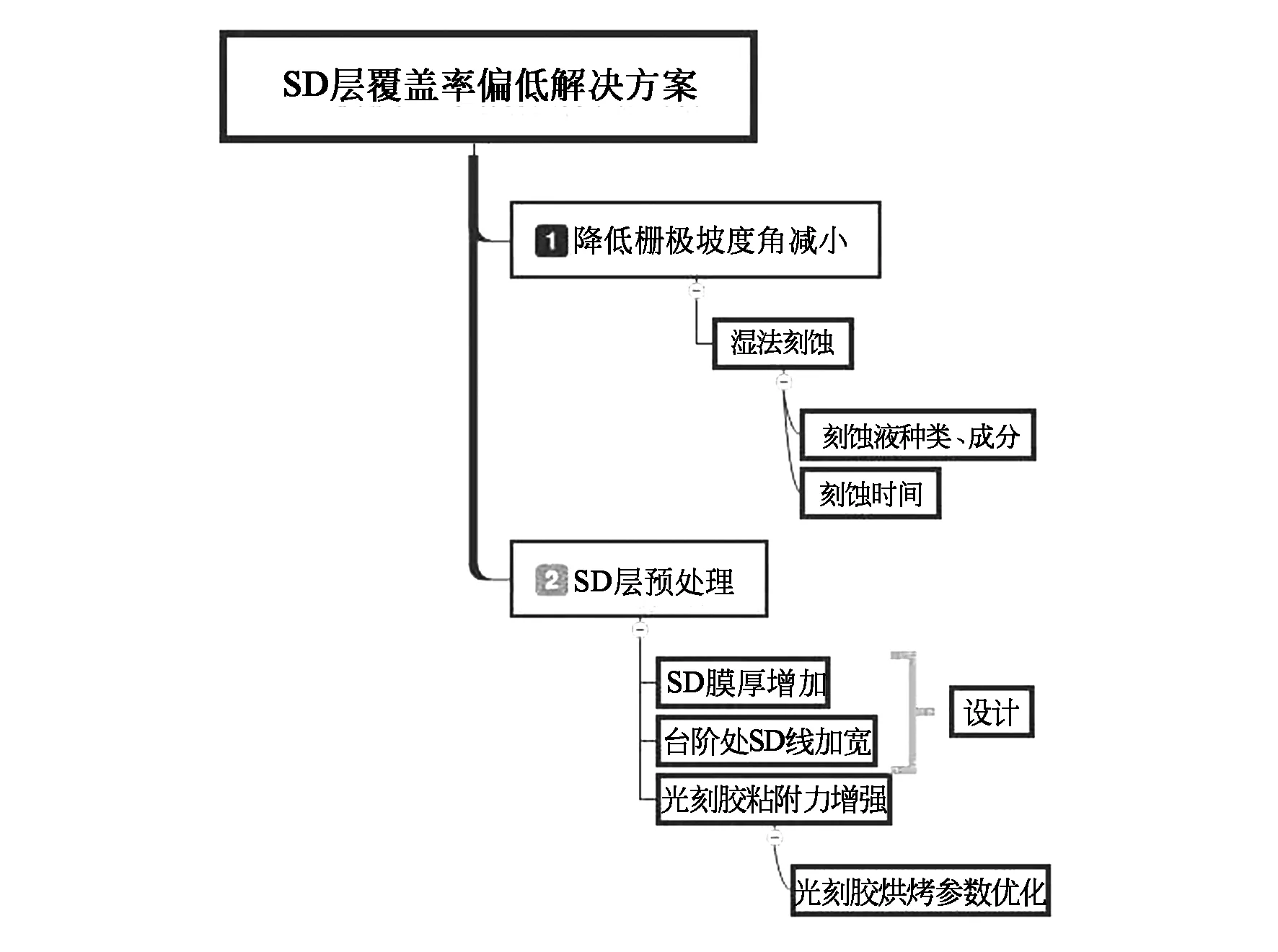

图18给出了SD层台阶覆盖率偏低的解决方案。首先考虑降低栅极坡度角,如果栅极坡度角不容易降低,则整体增加SD层的膜厚来规避台阶处断线的风险。在SD层膜厚不变的前提下,可以将台阶处的SD线设计得宽一下,进而避免该处断线。此外,可以在SD膜层的光刻阶段,调整光刻胶烘烤参数,增加光刻胶的粘附力,这样在后续刻蚀过程中不易形成台阶处断线。

图18 SD层台阶覆盖率偏低的解决方案Fig.18 Solutions for low step coverage of SD layer

4 结 论

实验探究表明,对于栅极形成的台阶,其坡度角对后续膜层的覆盖性有影响,而台阶厚度(280~500 nm)的影响可忽略。栅极坡度角与台阶覆盖率呈负相关关系,膜层的台阶覆盖性对制程和良率均产生影响。

栅极坡度角每增加10°,GI层的台阶覆盖率变下降约0.2,栅极坡度角增加会导致台阶处水平方向的GI膜层逐渐减薄。台阶处GI减薄后,腐蚀介质容易侵入,造成栅极腐蚀;同时,栅极的Cu朝SD电极扩散造成GI厚度进一步降低,栅极腐蚀的风险加大且有ESD或者栅极与SD电极短路的风险。栅极台阶造成该处SD膜层减薄,该处刻蚀程度加大,且栅极坡度角越大该处的刻蚀程度也越大,该处有SD断线的风险。对于栅极坡度角偏大引发GI层覆盖率和SD层覆盖率偏低造成的不良,可以通过降低栅极坡度角的途径进行改善。栅极的光刻、湿法刻蚀等参数调整,可以有效降低栅极坡度角。同时,对于GI覆盖率偏低问题,可以从GI的CVD成膜阶段进行参数优化,获得良好的台阶覆盖率。此外,对于SD层台阶覆盖率偏低的情况,可以通过增加SD膜厚、增加台阶处SD线宽的措施来规避台阶位置SD断线。