金刚石半导体器件的研究进展

2020-10-30王凡生汪建华鲁振海王连忠

王凡生,刘 繁,汪建华,鲁振海,王连忠

等离子体化学与新材料湖北省重点实验室(武汉工程大学),湖北 武汉 430205

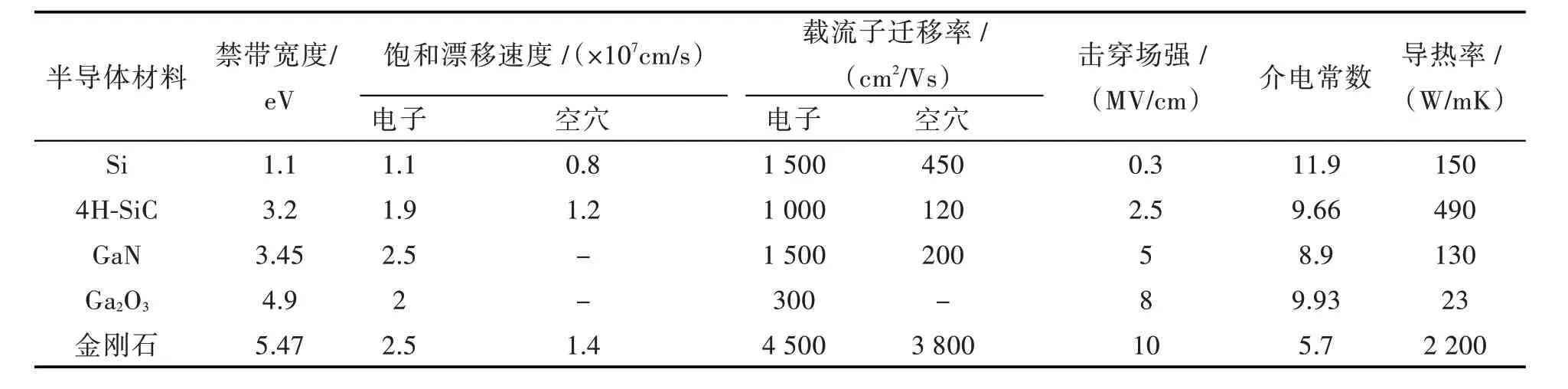

对于提供低功耗和高频操作的下一代电力电子器件,金刚石是一种极有前景的材料。金刚石具有极低的本征载流子浓度,有望实现低泄漏电流与高温操作。表1 比较了Si、4H-SiC、GaN、Ga2O3和金刚石的性能。金刚石具有很高的载流子迁移率(电子和空穴迁移率分别为4 500和3 800 cm2/Vs)[1]、超高的击穿电场(>10 MV/cm)、低介电常数(5.7)[2]和很高的热导率(2 200 W/mK)。因此,人们期望基于金刚石基的功率器件能够显著地减少传导损耗和开关损耗。

近十年来,金刚石生长技术得到了改进与提升,掺杂控制的p 型、n 型金刚石和本征金刚石生长技术已经趋于成熟。因此,这些材料的电学特性不仅可以从理论上进行表征,而且可以用器件结构进行实验研究。例如,用瞬态电流技术估算电子和空穴的载流子速度[3],用飞行时间和霍尔效应测量获得载流子迁移率[4]。通过对平面肖特基势垒二极管(Schottky barrier diodes,SBD)掺杂剖面和击穿电压的分析,得到了9.5 MV/cm 的最大击穿场强[5]。近年来报道了许多金刚石SBD 的性能,如Vmax>10 kV 的击穿电压[6-7]、大于20 A 的大电流操作[8]等。在本文中,回顾了金刚石半导体器件的近期进展。

表1 不同半导体材料的性能Tab.1 Performances of different semiconductor materials

1 金刚石器件

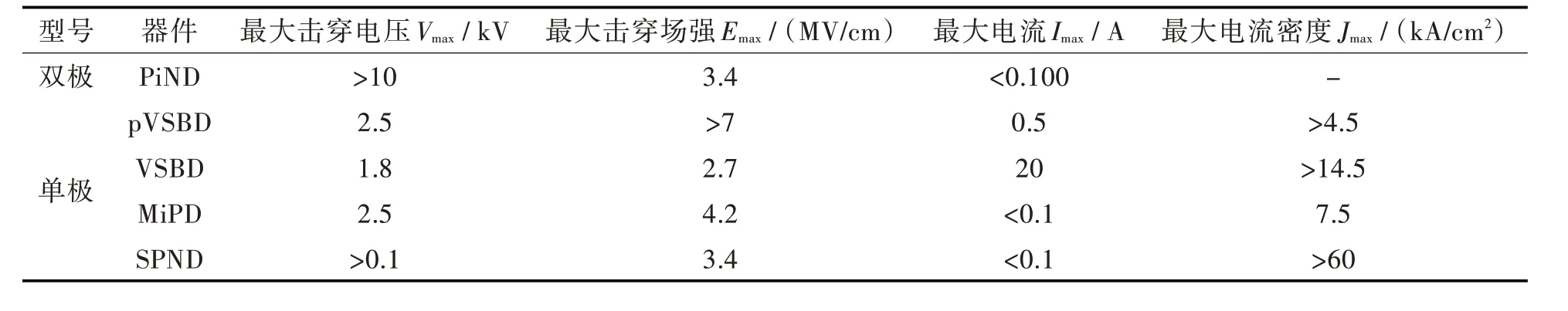

1.1 二极管

单极和双极二极管,如p 型-本征-n 型二极管(p-type-intrinsic-n-typediode,PiND)、SBD、金属本征p 型二极管(metal-intrinsic-p type diode,MiPD)和肖特基pn 二极管(Schottky pn diode,SPND)等具有代表性的器件性能参数已通过实验测量如表2所示,金刚石二极管横截面结构如图1 所示。

1.1.1 PiND 双极PiND 横截面结构如图1(a)所示,Hathwar 等[9]通过无台式结构的PiND 获得了最高大于11.5 kV 的最大击穿电压Vmax。当使用台式结构时,由于泄漏电流增加,导致击穿电压降低。泄漏电流的增加被认为是由于台面刻蚀过程中形成的缺陷所致。双极金刚石器件由于载流子寿命短导致正向电流密度较低。

1.1.2 pVSBD 因为可以利用较高的晶体质量和低成本的半导体衬底,伪垂直肖特基二极管(pseudovertical SBD,pVSBD)结构非常适合金刚石二极管的制备[10-11]。如图1(b)所示,具体制备流程是:首先在半导体衬底上生长出厚度为1~3 μm 的重掺硼p+型层,然后沉积轻掺硼的p-漂移层。p-漂移层经选择性刻蚀后,在p+层上直接形成欧姆接触。在这种结构中,耗尽层垂直延伸到漂移层,然而,正向电流在p+层中横向流动。p+层中载流子的平均自由程随接触的面积增大而增大,相应地,p+的电阻不随接触面积的增加而降低。由于这种影响,pVSBD 目前传输电流的能力被限制在5 A以下[12]。

表2 金刚石二极管的性能Tab.2 Performances of diamond diodes

图1 金刚石二极管截面结构图:(a)PiND,(b)pVSBD,(c)VSBD,(d)MiPD,(e)SPNDFig.1 Cross-section structures diagrams of diamond diode:(a)PiND,(b)pVSBD,(c)VSBD,(d)MiPD,(e)SPND

pVSBD 金刚石的肖特基势垒高度(Schottky barrier height,SBH)具有很大的可控性,是其重要的优点之一。Craciun 等[13]报道了氧终端的p 型金刚石的SBH 为1.2~3.4 eV,这与Si 和SiC 的禁带范围相当。特别是臭氧处理后的表面表现出较高的SBH 和大于2.5 MV/cm 的电场强度[14-15],从而无需边缘终止技术。利用这种处理方法,ZrSBD 器件实现了在6 V 下的高反向阻断电压>1 kV 和高电流密度>1 kA/cm2[16]。由于测试设备的测量限制,未发现该装置的击穿行为。但从p-层掺杂浓度计算,最大击穿场估计大于7.7 MV/cm。

Fiori 等[17]对肖特基界面也进行了一些研究。在正向偏压条件下,金属与氧端金刚石之间的载流子输运可以用热离子发射模型来解释。然而,SBH 与电负性差之间也存在反比关系[18-19]。Muret等[20]报告了势垒的不均匀性对正向和反向特性都有影响并表明界面缺陷或界面电荷的存在取决于氧化方法。

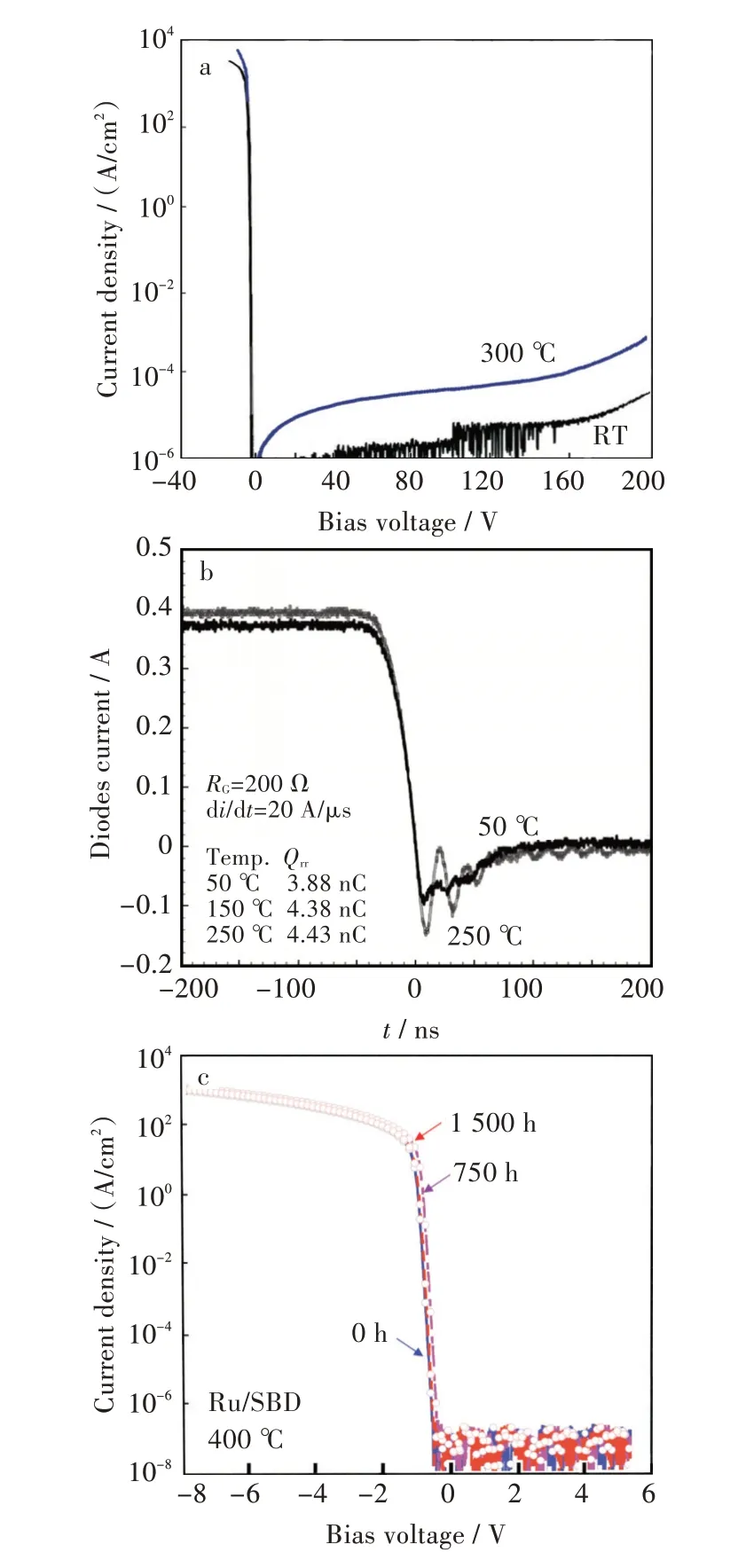

图2(a)为有50 μm 大小肖特基接触的pVSBD的典型正向和反向电流电压特性。用Mo 作为肖特基金属,SBH 为2.2 eV。在肖特基接触电压为-7 V 时,室温(RT)正向电流密度为1 800 A/cm2,在250 ℃时为4 500 A/cm2。尽管未使用边缘终止结构,其反向电场强度依然大于3.5 MV/cm。虽然未观测到这些装置的雪崩击穿,但是由于泄漏电流的增加,截止电压受到了限制。在此衬底上,75%的器件的击穿场强Emax大于3 MV/cm。在考虑阻隔效应的情况下,金刚石SBD 的漏电流可以用热电子场发射来解释,该模型与实测的泄漏电流吻合良好,即使在高温下也是如此[21]。

1.1.3 VSBD VSBD 结构如图1(c)所示,图2(b)显示了双脉冲法测量的VSBD 的典型关断特性[22]。VSBD 安装在为高温高功率器件设计的金属/陶瓷封装上,如图2(b)所示,可以看出关断时间(turn off time,trr)与温度和正向电流密度无关。由于金刚石的介电常数较低,所以耗尽层电荷的反向恢复电荷Qrr小于SiC-SBD。金刚石SBD 的快速开关性能是其应用在高频低损耗电路的优点之一。

Young 等[23]研 究 了VSBD 的 肖 特 基 界 面 在 高温下的长期稳定性,结果如图2(c)所示。当肖特基界面稳定时,在250 ℃处,初始位移出现在1 h 左右;然而,即使在400 ℃、1 500 h 和500 ℃、250 h 之后,Ru/金刚石界面的SBH、RON和理想因子也都未进一步降低。Pt/金刚石和WC/金刚石界面也表现出良好的热稳定性,因为铂族金属需要的活化能极高或者在界面层形成金属碳化物[24]。在10 MJ/kg的X 射线照射下,金刚石VSBD 的耐辐射性也得到了Umezawa 等[25]的证实。

图2 金刚石VSBD 的电学特性:(a)在室温25 ℃和300 ℃时的典型电流-电压特性,(b)50 ℃和250 ℃下的关断特性,(c)在400 ℃退火的电流电压特性Fig.2 Electrical characteristics of diamond VSBD:(a)typical current-voltage characteristics at 25℃and 300 ℃,(b)turn-off characteristics at 50 ℃and 250℃,(c)current-voltage characteristics annealed at 400 ℃

1.1.4 MiPD MiPD 的截面结构图如图1(d)所示,是一种具有潜力的单极性金刚石器件。Brezeanu等[26]使用这种二极管结构实现大于2.5 kV 的关断电压。在正向偏压条件下,p+层注入的空穴在本征层(I 层)中具有高迁移率,而I 层在反向偏压条件下阻断高电压。但是,因为正向电流是由空间电荷限制电流决定的,所以电流密度是有限的,尤其是在高温下[27-28]。

1.1.5 SPND 当硼浓度大于1020/cm3时,与碳相比由于硼的共价半径较大,即使在金刚石中可能存在高硼掺杂浓度,晶格膨胀也不能忽略[29]。Kitagoh 等[30]用X 射线衍射和透射电镜证实了晶格在产生大量位错后发生的弛豫,测定了8×1021/cm3掺硼薄膜的临界厚度为200 nm。Alegre 等[31]估算了(001)生长的临界硼浓度为3.2×1021/cm3,并得出结论:位错的产生是由于邻近效应。因此,在p+/衬底上生长的漂移层(如pVSBD)具有源自缺陷p+层的高密度位错。为了避免这种影响,Nagase 等[32]首先在高质量的半绝缘基片上生长一层p-漂移层,然后生长一层p+接触层,最后从背面蚀刻50 μm 厚的基板,在p 层上制备肖特基接触。利用该结构获得了最大击穿电压Vmax为700 V。

由Makino 等[33-34]报导了SPND,如图1(e)所示,其最高电流密度超过60 kA/cm2。它们在顶部具有肖特基接触的p+接触层上使用轻掺杂n 型漂移层。在正向偏压的条件下,n 型层仍耗尽,使得从p+层注入的空穴通过饱和速度流过n 型层,因此,正向电流密度与n 型层厚度几乎无关,另一方面,阻断电压由n 型层的厚度确定。Makino 等[35]还报告了用trr小于30 ns 的快速关断,这在常规PN结二极管中是不可能的。n 型掺杂浓度随漂移层厚度的增加而减小从而提高Vmax,保持漂移层在正偏压区的完全耗尽状态。

1.2 开关器件

将金刚石用于开关器件的研究始于20 世纪80年代。表3 和图3 分别列出了金刚石开关器件的性能及其典型结构。

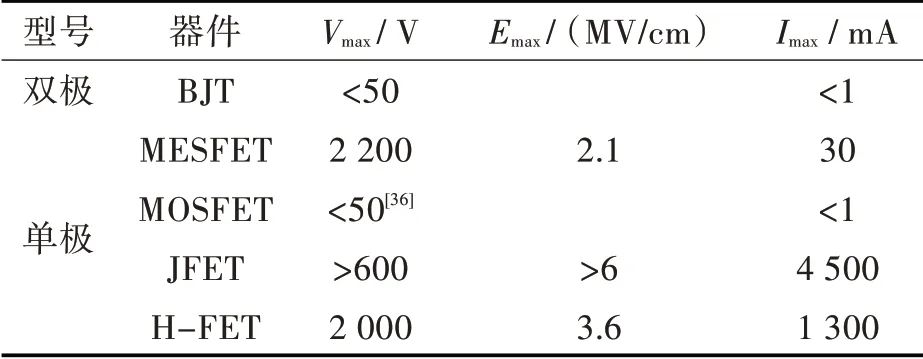

表3 金刚石开关器件的性能Tab.3 Performances of diamond switching devices

1.2.1 BJT Prins[37]首先利用天然p 型金刚石晶体作为具有n 型发射极和通过碳离子注入形成的集电极区域的基极电极来实现双极结型晶体管(bipolar junction transistor,BJT)。然而,由于制造工艺等问题,电流无增益效果。

1.2.2 MESFET 与MISFET 在BJTs 这一发现之后,金属半导体FET(metal-semiconductor field effect transistor,MESFET)[38]和金属绝缘体半导体FET(metal-insulate-semiconductor field effect transistor,MISFET)[39]也在天然金刚石晶体上实现了扩散掺杂或离子注入掺杂。21 世纪初,在化学气相沉积(CVD)外延生长技术建立之后,这种情况发生了巨大的变化。具有可控性很强的SBH 的肖特基接触可以简单地被制造在氧终端的金刚石表面。因此,深耗尽型MESFET 在高温条件下具有高阻断电压和低栅漏电流的工作特性。

1.2.3 MOSFET Pham 等[40]研究深耗尽型金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)表 明,在500 ℃退火,在累积条件下,栅漏电流急剧减小。

1.2.4 JFET 结栅场效应管(junction gate FET,JFET)也是典型的常开器件,其结栅下面通道中的耗尽层由栅极偏压控制[41]。由于金刚石PN 结内建电势大于5 eV,使常关式操作成为可能[42]。JFET 在室温和200 ℃下均能阻断大于600 V 的电压,击穿场强>6 MV/cm。高质量的横向PN 结决定了高电场强度[43-44]。Iwasaki等[45]实现了JFET 的更高的电流密度458 A/cm2的双极运行。

1.2.5 H-FET 氢终端对金刚石表面的电学特性起着重要的作用。金刚石经过化学气相沉积后的典型表面结构为氢终端,会呈现二维p 型表面导电。这个表面导电层具有较高的载流子浓度(>1012/cm2)、较浅的厚度(<10 nm)和较低的活化能,这种表面导电层是场效应晶体管沟道的理想材料[46]。最近,Kitabayashi等[47]对H-FET 的击穿电压进行了表征,与MESFET 类似,通过将提高栅极与漏极的距离到24 μm,H-FET 的Vmax可提高到2 kV,这是金刚石场效应管的最高值。

Matsumoto 等[48]利用OH 终端在(111)面金刚石上实现反型MOSFET。他们用磷掺杂的n 型层作为主体,以通过原子层沉积的Al2O3作为栅极绝缘体,在栅偏压为6.3 V 时形成了p 型反转通道。他们确定反转迁移率为8 cm2/Vs。

由于金刚石的优异特性,它在制备电力电子设备方面具有巨大优势。人们已经成功开发了各种FET 结构,并取得了预期的结果。然而,在高功率晶体管的制备中,寻找合适的栅极绝缘材料仍是亟需解决的问题。金刚石晶体管常用的栅极绝缘材料有:Al2O3,SiO2,CaF2等。然而,这些材料的介电常数很低,无法完全控制金刚石的高空穴密度。另一方面,铁电材料具有极高的介电常数,但是需要合适的过渡层材料来制造高功率金刚石晶体管。因此,选择新的栅极绝缘材料对于制备新的基于金刚石的器件非常必要和紧迫。

图3 金刚石开关器件的典型结构:(a)BJT,(b)MESFET,(c)MOSFET,(d)JFET,(e)H-FETFig.3 Typical cross-sectional structures of diamond switching device:(a)BJT,(b)MESFET,(c)MOSFET,(d)JFET,(e)H-FET

2 金刚石的边缘终止和缺陷

即使金刚石具有优异的材料特性,由于在电位分布变得陡峭的电极边缘处发生击穿,所以也需要边缘终止技术。金刚石器件经常被观察到从电极边缘开始的硬击穿。针对金刚石器件提出的典型的边缘终止技术有:单极器件的绝缘膜;结终端扩展(junction termination extension,JTE)与绝缘多晶硅技术。

2.1 单极器件的绝缘膜

通过在肖特基电极和金刚石表面之间插入绝缘膜,可以使电极边缘的电场松弛。Ikeda 等[48-49]报道了以Al2O3和SiO2为绝缘体的金刚石SBD 的优化绝缘层结构。他们指出,随着FP 的实施,Vmax提高了2 倍以上,Al2O3的最佳厚度约为1.5 μm,是SiO2厚度的1.7 倍。Kato 等[50]通过实验证实了此方式可实现漏电流的减小和Vmax的改善。然而,由于电极边缘的场增强仍然存在,因此无法获得理想的击穿电压。

2.2 JTE

由于通过离子注入或高质量n 型选择区生长,在p 型金刚石表面都难以产生低阻的n 型层,很少有团队认识到JTE 的金刚石结构。Huang 等[51]在VSBD 边缘注入H+离子以获得与JTE 相同的效果,并报告Vmax为3.7 kV。

2.3 半绝缘多晶硅技术

与JTE 相反,表面半绝缘钝化层增加表面欧姆泄漏将提供均匀的表面电位分布,提高击穿电压,这被称为半绝缘多晶硅技术,主要用于高压硅器件[52]。这种技术被证实对金刚石SBD 也具有类似的效果。用绝缘层技术在10 MJ/kg 的X 射线辐照金刚石SBD 后,漏电流略有增加,达到10 μA/cm2。这种漏电流可能是由于通过辐照缺陷在Al2O3中的电荷传输,从而使SBD 的击穿电压提高了20%以上[25]。漏电流可以用弱反偏压区的欧姆传导和强偏压区的热电子发射来解释,因而,击穿仍然发生在电极的边缘。

2.4 器件的缺陷研究

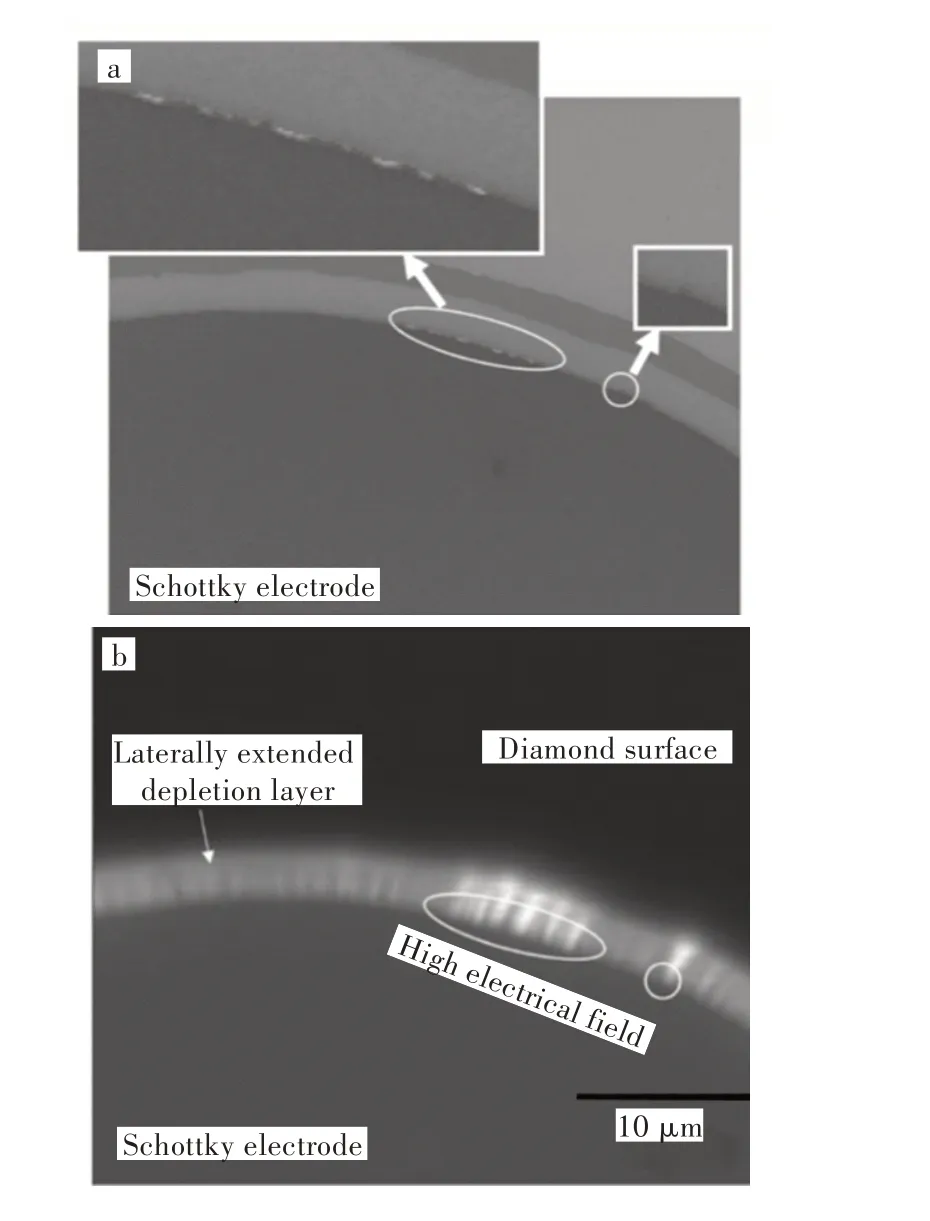

图4 100 V 偏压下的金刚石SBD:(a)SEM 图,(b)EBIC 图Fig.4 Diamond SBD biased at 100 V:(a)SEM image,(b)EBIC image

利用电子束感应电流(electron-beam induced current,EBIC)成像技术可以实现电极边缘场增强的实验可视化[53]。加速电子束辐照金刚石会产生电子空穴对。当反向偏压施加到SBD 时,产生的少数载流子,即金刚石中的电子,被电场加速并在漂移层中成倍增加。在肖特基接触处收集载流子作为电流,使与电子束扫描同步的电流映射对应于电场分布。如图4(a)所示,具有100 V 反向偏压的金刚石SBD 的扫描电子显微镜(scanning electron microscope,SEM)和EBIC 图像,在肖特基接触中心区域,平均电场为1.3 mV/cm。如图4(b)所示,SBD 周围有一个横向延伸的耗尽层,其表现为一个高EBIC 强度区。但是,EBIC 强度在耗尽层和极强信号区、热点区域并不均匀。热点的可能来源是与器件制造相关的结构缺陷,特别是与光刻和提升工艺有关的结构缺陷[54]。

缺陷也会导致器件性能下降。漂移层中的非外延微晶,是从衬底表面的污染物中生长出来的多 晶 粒 子,是VSBD[14]和MESFET[55]中 的 致 命 缺陷。这些微晶大多可以通过控制生长条件和使用基片剥离技术来去除[56]。然而,诸如螺纹位错等晶体缺陷的影响尚未得到解决。

X 射线形貌是表征金刚石晶体缺陷的有力工具[57]。Watanabe 等[58]在高压高温衬底上产生的位错密度估计为104~105/cm2。这些位错是通过化学气相沉积膜传播,以及由表面抛光缺陷产生的附加位错[59]。Kato 等[60]试图用X 射线形貌揭示漏电流与位错类型之间的关系,假设每种类型的位错对漏电流的增加都有其各自的贡献。他们得出结论,边缘和螺纹混合位错对泄漏电流有相似的贡献。Ohmagari 等[61]表征了SBD 的漏电流与阴极发光谱的带A 发射的关系,并得出结论:只有四重对称发光模式的缺陷才会产生漏电流。

3 结 论

自同质外延生长技术和掺杂控制建立以来,金刚石器件的性能得到显著地提高。目前实现了在500 ℃高温下,高正向电流密度并展现出长期稳定性的肖特基势垒二极管;具有低阻耗且阻断能力大于10 kV 的二极管也被实现。在开关器件方面,实现了金属半导体场效应晶体管与金属氧化物半导体场效应晶体管的阻断电压超过2 kV。然而,器件制造技术的缺乏仍然限制了器件的性能。离子注入和选择性区域生长形成边缘终端结构与MOS 结构制备技术一起,成为使金刚石发挥优异性能的必备技术条件之一。但是由于金刚石极好的化学稳定性与极高的硬度,给金刚石微结构处理带来了较大困难,为了提高器件的制造与器件的性能,对表面结构、界面结构和缺陷结构开展更深入的研究是十分必要的。