4K 视频流异构多核的多路分屏方法

2020-10-23吴志忠李毅航张志刚唐俊龙唐立军

吴志忠,邓 敏,李毅航,张志刚,张 宽,唐俊龙,唐立军

(1.长沙理工大学物理与电子科学学院,长沙,410114;2.近地空间电磁环境监测与建模湖南省普通高校重点实验室,长沙,410114)

引 言

近年来,高分辨率图像获取技术的进步为生物医学、天体物理学及地球系统科学等诸多领域的可视化数据分析提供了有力条件。这些可视化数据通常需要采用较大尺寸的显示器来配合高分辨率数据的展示,以达到在整幅画面下观察图像局部细节的目的[1]。然而可视化数据在显示分辨率方面的需求超过了单屏显示系统的能力,即在单显示器上无法以全分辨率显示整幅画面[2]。为解决此问题,一般通过多台投影机或液晶显示器组成显示矩阵,采用多屏幕拼接显示的方式扩大显示系统的整体分辨率和尺寸以满足可视化数据显示的需要。因此,随着可视化数据分辨率和尺寸需求的不断增长,所需的同屏显示设备数量也在不断增加,为显示控制系统带来了巨大挑战。

为了实现对多台显示器的控制和管理,国内外诸多学者和研究机构针对多屏显示技术开展了相关理论研究和应用技术开发,并取得了优秀的研究成果。例如,普林斯顿大学设计的Display Wall[3]系统以及伊利诺大学芝加哥分校提出的SAGE[4]和SAGE2[5]系统,在该领域均有良好的表现。Nirnimesh 等提出的Garuda[5]多屏显示系统,可以在无需修改下呈现任何基于开放场景的程序应用。Ueda 等针对常见多屏显示系统配置要求高、多运行在Linux 系统下且操作难度大的问题,开发了基于Windows 系统的多屏显示软件Tenmads[6],通过简单操作实现多屏显示管理。美国夏普实验室的Deshpande 等针对多用户拼接屏幕共享使用场景提出了SharpWall[7]拼接显示系统,实现了4K 视频流的传输和桌面的远程连接。日本三菱公司的Kanda 等提出了一种超高分辨率显示系统的多终端同步显示方法,使图形在显示器之间的显示延时小于0.5 帧[8]。石溪大学的Papadopoulos 等设计并建造了世界上第1 个10 亿像素分辨率的全封闭式显示器Reality Deck[9],为超大拼接显示在沉浸式系统中的应用做出了典范。

国内在多屏显示技术上也做了许多研究工作。例如,卢如西[10]提出了一种多输出通道显示单一完整桌面的计算机结构,可实现4×4 个显示单元的控制整体分辨率可达4 096 像素×3 072 像素@30 Hz。然后卢如西[11]针对超高分辨率图像处理的需求,设计了一种分布式并行处理架构,实现了分辨率为76 800 像素×8 000 像素超大规模的显示系统。陈绍林等[12]基于SAGE 和VizRoll 大屏显示技术,构建了4×5 的高分辨率并行显示阵列。刘伟俭[13]利用高速PCI-E 接口和FPGA 阵列,实现了支持64 路外部输入的总分辨率为15 360 像素×4 320 像素@60 Hz 的4×8 矩阵显示,单屏分辨率1 920 像素×1 080 像素@60 Hz 达到了较为领先的水平。此外,国内相关研究人员还提出了低成本、轻量级的分屏显示系统。例如,霍伟[14]设计了基于FPGA 的视频分割系统,实现了1 280 像素×960 像素分辨率图像的4 路720 像素×480 像素分辨率分割显示。李宗德[15]设计了输入分辨率为1 920 像素×1 080 像素@60 Hz 的4 通道DVI 接口分屏显示系统。苏健渊[16]基于ARM+FPGA 的嵌入式构架搭建了多屏图像联合显示系统,可将存储在U 盘中分辨率为10 240 像素×8 192 像素的超大图像内容读出并在4 个显示器上分屏显示,但无法实现视频显示功能。

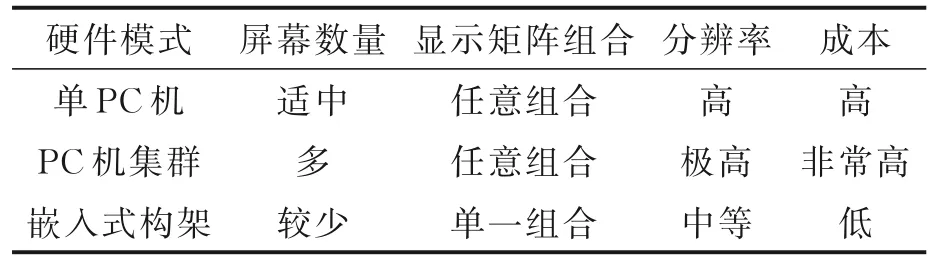

综上所述,现有多屏显示系统主要有3 种硬件实现模式:单PC 机模式、PC 机集群模式和嵌入式构架模式,如表1 所示。其中,单主机模式可控屏幕的数量取决于PC 机显卡的数量及性能;PC 机集群模式除了需要高速网络互联外,每台显示设备均需要配备独立终端PC 机,大大增加了多屏显示系统的使用成本;嵌入式构架模式最大分辨率受制于分屏装置的性能,允许输入的最大分辨率普遍低于单PC 机和PC 机集群模式,且分屏形式较为单一,通常仅支持1×2 或2×2 的显示阵列,不能实时改变分屏的路数和分辨率等参数的配置。

表1 不同硬件模式对比Table 1 Comparison of different hardware modes

为了实现高分辨率、灵活组合的多屏显示系统,本文以4K 视频多路分屏显示为目标,研究视频流传输、转换、处理及分屏显示过程,探索基于异构多核的4K 视频流多路分屏方法。此方法可提升嵌入式构架模式多屏显示系统的最高分辨率,达到3 840 像素×2 160 像素@60 Hz 的最高输入分辨率,并根据输入分辨率的行列数量自适应匹配包括1×2,1×3,1×4 和2×2 在内的多种显示矩阵组合,有效提升分屏显示系统性能。

1 视频流多路分屏传输方案

1.1 视频流高速数据传输链路

多屏显示系统是视频信号从信号源到每台显示设备的必经传输链路,多屏显示系统的数据带宽是制约系统最高分辨率的主要因素之一。因此,为系统选择恰当的视频输入、输出接口和数据缓冲区以满足传输的速率要求至关重要。本文以系统的最高输入分辨率为参考,确定系统数据带宽,保证系统的可行性。

每秒60 帧的4K 分辨率(3 840 像素×2 160 像素)视频以常规8 位色深的完全取样YUV444 像素格式进行传输时,其像素时钟为594 MHz,数据带宽可达17.82 Gb/s[17]。因此,文献[14-16]所使用的DVI或VGA 接口均无法满足系统带宽要求。为了满足系统输入、输出带宽,本文采用1.2 版本的DisplayPort(DP)接口作为系统输入接口,最高带宽可达21.6 Gb/s[18]满足系统输入要求;采用1.4 版本的HDMI 接口作为系统输出接口,最高带宽可达10.2 Gb/s[19]满足系统分屏输出要求。选用带宽可达25.6 Gb/s 的DDR3L-1600 型第三代随机存取器作为数据缓冲区,保证缓冲区带宽满足链路要求。

1.2 异构多核的多路分屏控制方法

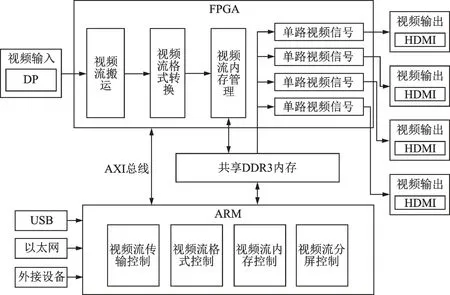

嵌入式构架的多屏显示系统,多采用FPGA 或ARM+FPGA 相结合的方式实现视频分割、处理和传输的功能。采用单FPGA 方式时,受FPGA 工作原理的影响通常仅能实现单一的分屏显示组合;ARM+FPGA 方式中,由于两者缺少有效的高速数据链路,系统整体性能受到严重制约,无法处理高分辨率视频输入。为了克服以上系统结构的缺点,本文利用全可编程的ARM+FPGA 异构多核片上系统设计多屏显示系统,实现多路分屏控制方法。

全可编程的异构多核片上系统构架有利于发挥ARM 处理器与FPGA 各自的优势,实现优势互补。该构架通过片上高速AXI 总线实现ARM 与FPGA 间的快速数据交换[8]。ARM 通过FPGA 中IP 核的基地址,利用AXI 总线读写IP 核的寄存器数据,对参与运算的数据和参数进行灵活配置;FPGA 负责高速、大规模数据处理保证运算速度。嵌入式构架的分屏显示系统结构如图1 所示。在ARM 处理器上利用PetaLinux 工具定制适用于多屏显示的专用Linux 操作系统,进行多屏显示系统的顶层设计,使片上FPGA 与多核ARM 处理器实现协同工作。通过一级引导程序对系统进行初始化配置、加载逻辑电路固件;生成的U-boot 固件引导Linux 内核启动,读取设备树文件,挂载多屏显示相关IP 核驱动,使应用程序可以控制底层硬件[20]。内核模块分配内存地址空间运行多屏显示组件,实现FPGA 与ARM 的内存共享,从而实现两者间的高速数据交换。

图1 分屏显示系统结构Fig.1 Structure of a split-screen display system

2 视频流多路分屏传输技术

2.1 视频流高速数据传输技术

一般情况下,FPGA 采用直接存储器访问(Direct memory access,DMA)方式访问内存进行交换,然而DMA 方式的传输带宽大约在750 Mb/s[21],无法满足4K 视频流的传输需求。因此,需要设计适用于视频访问的专用高速视频直接存储器访问(Video direct memory access,VDMA)模块进行数据交换。VDMA 支持多字节数据访问,接口宽度最高可达1 024 b,存取频率可达200 MHz,数据带宽上限可达200 Gb/s,可较好地满足4K 视频数据的访问。VDMA 结构框图如图2 所示。视频流在存入内存之前,先传入最多可以缓冲32 行视频数据的异步行缓冲区,完成视频帧速率与内存工作频率之间的动态匹配。设计基于AXI 总线的控制和状态寄存器连接,实现ARM 处理器对异步行缓冲器的控制,进行像素数据临时保存操作;实现VDMA 模块的数据接口宽度与访问频率等参数的在线调整,实时改变VDMA的数据操作数量,满足行列数自适应匹配的多种显示矩阵组合。建立独立的全双工数据读写通道,对内存地址进行映射,通过地址偏移访问未对齐内存区域,实现缓存区以内存任意地址为起始位置的读写,防止因地址对齐造成的内存溢出或数据丢失。VDMA 采用全双工异步通信模式,视频流的输入、输出均与外部输入的独立时钟源同步,保证了模块的独立工作状态,使其不受处理器端的制约,以发挥其最大能效。

图2 VDMA 结构框图Fig.2 VDMA structure

2.2 视频流像素数据格式的转换

通常摄像头或者其他设备采集的原始视频信号多为RGB色彩模型格式的像素,而人眼对色彩细节的分辨率比对亮度细节的分辨率要差。因此,为了进一步提高显示系统的最高分辨率与刷新频率,需要将RGB格式的像素数据转换成亮度色度格式(YUV),并对色度分辨率进行适当压缩,减少数据量以达到增加有效显示像素数量、提高显示刷新频率的目的。

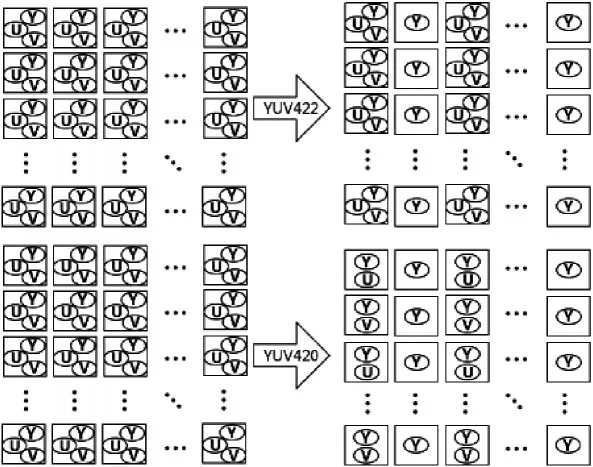

YUV格式中Y代表图像的亮度,U和V代表图像的色相和色饱和度。本文所设计的分屏显示系统所支持的像素格式为YUV422 和YUV420,其中422 和420 分别代表像素点按照2∶1 的水平方向重采样、1∶1 的垂直方向重采样和水平、垂直方向全部采用2∶1 的重采样。通过RGB到YUV422(420)格式的重采样转换,实现视频流数据的压缩。

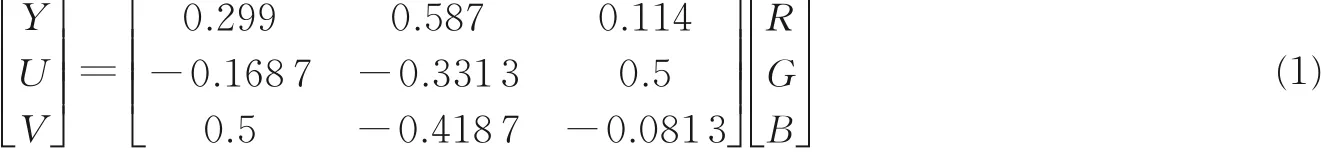

像素数据从RGB到YUV422(420)格式的转换时,需要先把RGB转换为YUV444 格式,再进行重采样压缩,RGB与YUV间的转换方程为[22]

转换后的YUV444 像素格式,进行重采样降低U和V的分辨率,实现YUV422 或YUV420 格式。

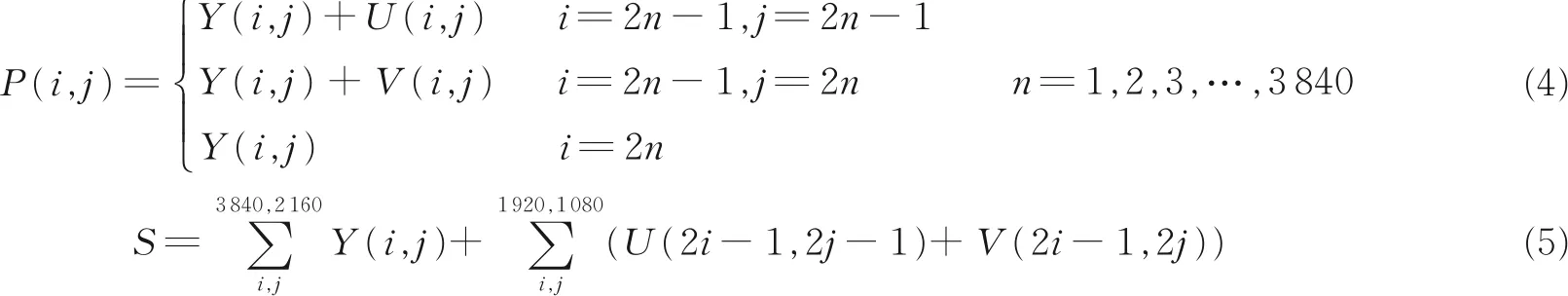

设Y(i,j),U(i,j),V(i,j)分别为第i行j列像素点的Y,U,V的值,P(i,j)为1 个像素所包含的YUV信息,S为1 帧图像包含的YUV值。

当YUV采样比为4∶2∶2 时,每行像素中间隔1 个像素剔除U和V的信息。

当YUV采样比为4∶2∶0 时,1 行像素中剔除所有V信息保留U信息,间隔1 列剔除所有U信息保留V信息,同时每行像素中间隔1 个像素剔除U或V的信息。

由S构成的视频流便可在内存中进行下一步分割重组。YUV压缩变换示意如图3 所示。

2.3 视频流分屏数据的内存管理

图3 YUV 压缩变换示意图Fig.3 YUV compression transformation diagram

多屏显示系统以4K 视频图像每帧的完整画面作为一个数据单元进行处理,通过将存储的有效帧图像数据的内存地址进行重新映射,转换为多组不同分辨率的图像,以4 组1080P 的视频图像为例,命名为P1,P2,P3,P4。传输的4K 视频流是采用逐行扫描方式,图像的首行起始地址映射为P1的起始地址之后依次储存;当地址偏移1 920 个存储单元后,将地址映射到P2的起始地址,再依次储存1 920 个存储单元。按照上述方式,把第1~1 080 行的视频数据存储到P1,P2,把第1 081~2 160 行的视频数据存储到P3,P4。若P(i,j)为1 帧4K 视频图像i行j列的像素点,P1,P2,P3,P4为重组的4 组1080P 视频图像,其原始数据重组关系为

重组完成的4 组1080P 视频图像进行下一步单路视频信号再现。

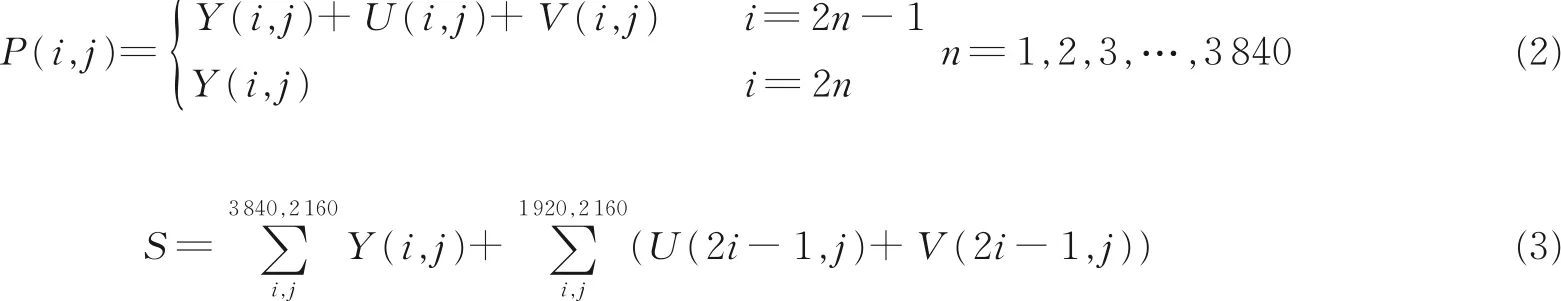

2.4 视频信号再现

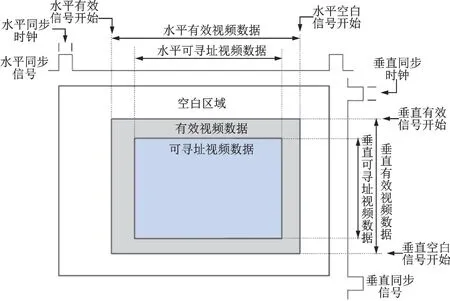

在视频显示技术中,视频信号不仅包含有效的像素信息,还包括时钟信号DCLK、行同步信号HS、场同步信号VS,数据选通信号DE,这些信号构成的视频流包含了空白区域、有效视频数据以及可寻址数据。视频信号的不同决定着输出显示视频的格式,如分辨率和帧率等。图4 为1 帧视频图像框架。

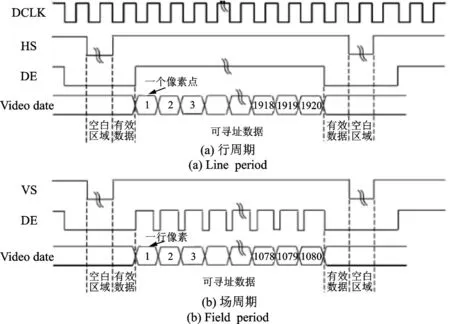

ARM 通过IIC 接口读取显示器的扩展显示器识别数据(Extended display identification data,EDID),包含了显示设备的特性,其中第35~37 字节数据,确定显示器能输出显示的视频格式。ARM 通过改变视频时钟频率,行、场同步信号参数,控制FPGA 输出多路与之对应的视频流,经过高清多媒体接口发生器转换成HDMI 接口的视频流进行分屏显示。图5 为1080P 视频信号再现示意图。每个时钟上升沿传输1 个像素点数据,当HS 为低电平时传输数据无效,HS 上升沿时意味着1 行像素开始传输,DE为高电平时传输内存中可寻址像素,每行像素传输同理,由VS 信号决定一帧图像的传输。

图4 1 帧视频图像框架Fig.4 A frame diagram of a video image

图5 视频信号再现示意图Fig.5 Video signal reconstruction shows timing

3 测试及结果分析

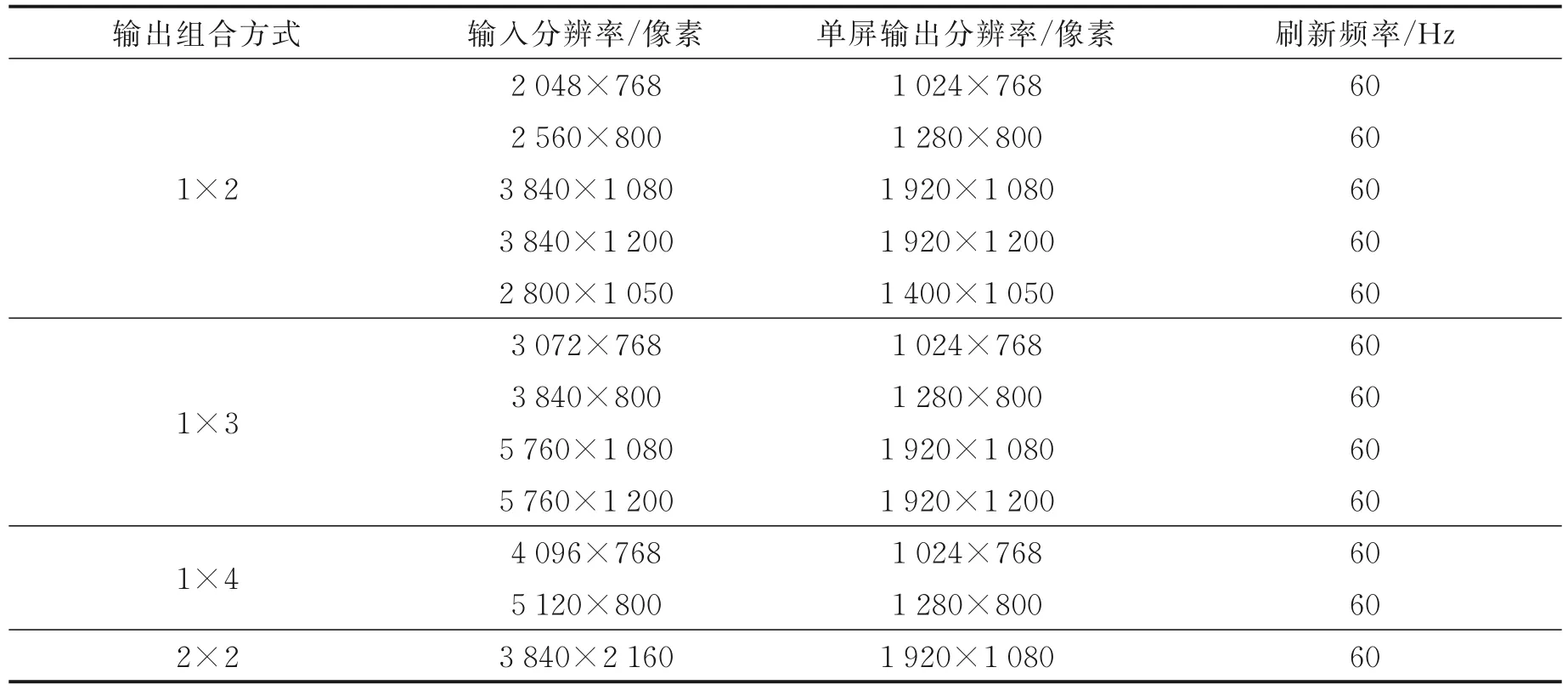

本文采用Zynq UltraScale+MPSOC XCZU7EV 多核异构处理器开发平台对技术进行验证。分别对系统所支持的二分屏、三分屏和四分屏(2×2 组合和1×4 组合)下不同分辨率显示输出进行了验证测试。不同输出组合方式下的输入、输出分辨率如表2 所示。

表2 屏幕组合方式及分辨率Table 2 Screen combination mode and resolution

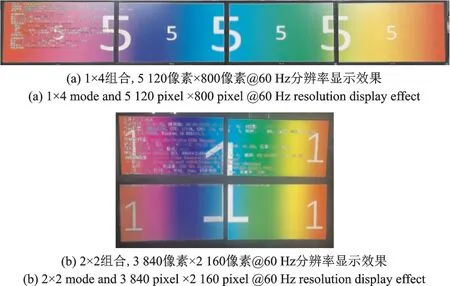

图6 分别为1×4 组合5 120×800@60 Hz 分辨率、2×2 组合3 840×2 160@60 Hz 分辨率的显示效果。输出端连接4 台分辨率为2 560×1 440 的显示器(型号:272B8QJNB),图像清晰,四端口显示顺序正确,无错位现象。

图6 不同组合方式显示效果Fig.6 Display results in different combinations

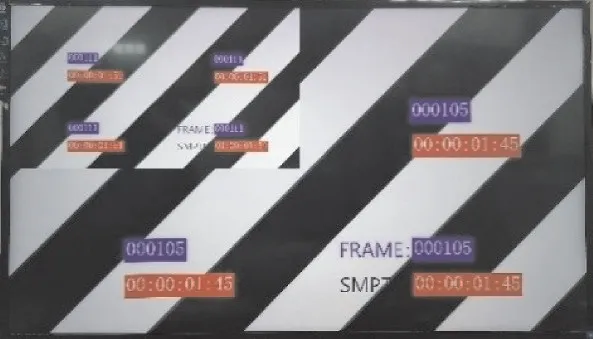

采用支持多视窗技术的显示器( 型号:PHILIPS-BDM4350UC),进行信号延时、丢帧检测。显示图像如图7 所示,第1 路(左上角)由信号源直接输入原始“斑马纹”测试视频信号(分辨率为3 840×2 160@60 Hz);其余3 路为分屏后输出的第2~4路信号。信号无卡顿、丢帧现象,显示顺序正确。原始信号与分屏后输出信号相差6 帧,分屏传输时延为100 ms,传输时延较低,可较好满足应用要求。

图7 传输延时测试结果Fig.7 Transmit delay test results

4 结束语

本文提出了一种基于异构多核构架的视频流多路分屏传输方法,搭建了VDMA 模块对视频流进行高速搬运,保证了超高清视频流的传输可靠性与稳定性;通过嵌入式Linux 系统使分屏显示更具灵活性,实现了多种不同输出组合方式下的多种分辨率的自适应分屏显示。与传统嵌入式构架的多屏显示系统相比,异构多核构架多屏显示系统在高清视频流分屏显示上具有一定优势,可实现最高3 840 像素×2 160 像素@60 Hz 分辨率的视频流分屏传输。在同等分辨大小的情况下,屏幕刷新率与现有同级别多屏显示系统相比提升了一倍,且传输时延仍然保持在较低水平。该方法的传输速率与播放效果能较好地满足4K 超高清视频流分屏显示的应用要求。但是本文仅研究了视频流的分屏传输技术,下一步将继续研究分屏传输过程中屏幕边框对显示效果的影响,探索多种屏幕组合下视频流的边框过度方法,以改进当前分屏显示系统的性能。