Effect of microstructure of Au80Sn20 solder on the thermal resistance TO56 packaged GaN-based laser diodes

2020-10-22HaoLinDeyaoLiLiqunZhangPengyanWenShumingZhangJianpingLiuandHuiYang

Hao Lin , Deyao Li, Liqun Zhang, Pengyan Wen, Shuming Zhang, Jianping Liu, , and Hui Yang

1School of Materials Science and Engineering, Shanghai University, Shanghai 201900, China

2Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Suzhou 215123, China

Abstract: Au80Sn20 alloy is a widely used solder for laser diode packaging. In this paper, the thermal resistance of GaN-based blue laser diodes packaged in TO56 cans were measured by the forward voltage method. The microstructures of Au80Sn20 solder were then investigated to understand the reason for the difference in thermal resistance. It was found that the microstructure with a higher content of Au-rich phase in the center of the solder and a lower content of (Au,Ni)Sn phase at the interface of the solder/heat sink resulted in lower thermal resistance. This is attributed to the lower thermal resistance of Au-rich phase and higher thermal resistance of (Au,Ni)Sn phase.

Key words: Au80Sn20; laser diodes package; thermal resistance

1. Introduction

With the rapid evolution of semiconductor laser technology, the optical power of laser diodes (LDs) keeps increasing,and the joule heat induced by series resistance increases.The joule heat needs to be dissipated effectively otherwise will adversely affect LD performance and reliability[1]. Therefore, packaging techniques with a low thermal resistance are needed. The total thermal resistance of LD packaging is limited by the portion with the highest thermal resistance. The solder layer, which bonds LD chips and heat sinks, is the portion with lowest thermal conductivity in the GaN-based LD package. Therefore, it has a significant effect on the total thermal resistance[2]. To improve the optical power, decreasing the thermal resistance of the bonding layer is effective[3,4].

As the material connecting the LD chips and the heat sink, solder plays an important role in the thermal packaging system. Au80Sn20 alloy has good thermal and electrical conductivity. As a hard solder with high melting point, Au80Sn20 alloy has good creep resistance and mechanical properties,and thus it can be used in LDs, power electronics, MEMS sensors, and other applications[5−8]. Due to the big difference of electronegativity between Au (2.3) and Sn (1.8), Au80Sn20 alloy tends to form a stable intermetallic compound (IMC)rather than solid solution. The IMCs in Au80Sn20 alloy play a key role in the mechanical and thermoelectric properties[9,10].

In this paper, the thermal resistance of GaN-based blue laser diodes packaged in TO56 cans were measured by the forward voltage method. The microstructures of Au80Sn20 solder were then investigated to understand the reason for the difference in thermal resistance. It was found that the microstructure with higher content of Au-rich phase in the center of the solder and lower content of (Au,Ni)Sn phase at the interface of the solder/heat sink resulted in lower thermal resistance.

2. Experimental details

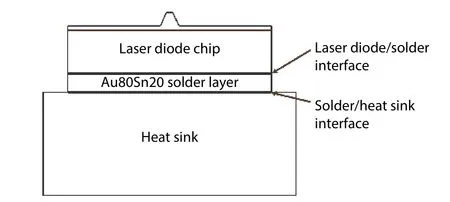

The packaged LD samples studied here are from the same epitaxial wafer and chip processing but different packaging processing, and the chip size of both is 200 × 400μm2.The results shown in this paper are from typical samples of each batch named E09 and Y00. These two samples have a similar structure, and the schematic diagram of the structure is shown in Fig. 1. The Au80Sn20 solder bonds the LD chip and heat sink, and there are two solder layer interfaces.

We first measured the thermal resistance of TO56 packaged GaN-based LDs using the forward voltage method,which was reported by us previously[11]. It is based on the linear relation between the junction temperature (T) and the forward voltage (Vf). When the injection current is a constant[12−15], the relation can be fitted as follows:

whereTis the junction temperature of the LD, andAandBare the fitting parameters. We first measured the value of the temperature-sensitive parameterA. Next, by changing the injection current from an operation current to a very low current at which joule heat is negligible, we measured the voltage variation (ΔV) of the LD caused by the variation of the junction temperature (ΔT) using a MDO4104-3 mixed domain oscilloscope. The ΔTcan be calculated by the following equation:

whereVftis the forward voltage of the LD at high injected current. As the joule heat dissipates rapidly, the decrease of junction temperature will cause the forward voltage to increase[16].Vf0is the forward voltage of the LD when the junction temperature decreases to room temperature. The thermal resistance (Rth) of the LD can be expressed as[15]:

Fig. 1. The schematic diagram of structure of packaged laser diodes.

Fig. 2. (Color online) The P–I curve of sample E09 and Y00.

whereIHis the injection current, whileVHandPoptare the voltage and optical output power of the LD under the corresponding injection currentIH.

For IMCs analysis, the scanning electron microscope(SEM) and energy dispersive X-ray spectroscopy (EDS) have been carried out. We selected FEI quanta FEG 250 to perform SEM, which has EDS subassembly named EDXX Apollo XP. In order to observe the IMCs in the solder joint clearly, the packaged LDs were polished into cross-sectional samples.

3. Results and discussions

Fig. 2 shows the power–current (P–I) curves of two LD samples. E09 has a lower threshold current and a higher slope efficiency than Y00. It is suggested that the difference of optical power between these two LD samples is caused by the different thermal resistance.

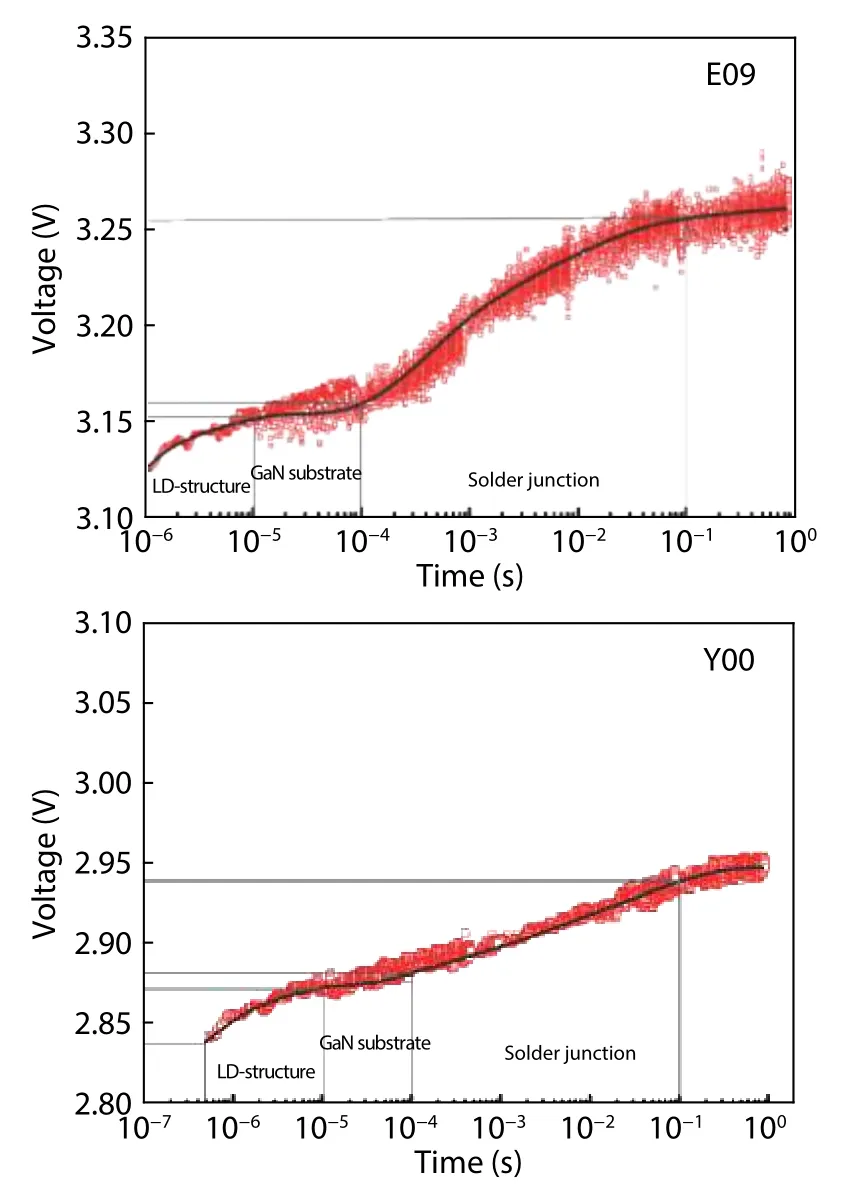

In order to verify the effect of thermal resistance on optical power, we then measured the thermal resistance of the two samples. From theI–Vcurves under different measured temperatures, the relation between the junction temperature and the forward voltage was fitted with Eq. (1), and the temperature-sensitive parameterAwas thus calculated to be 4.33 mV/K for E09, 2.66 mV/K for Y00. We then measured the time-resolved voltage variation of these two samples. In the working state, after the LD samples reached a steady-state,we measured the working currentIH, voltageVHand optical output powerPopt. In the measuring state, we measured the variation of forward voltage from the very beginning of the measuring state to room temperature. According to our previous simulation and experimental work[11,17], the time-resolved voltage curve of a LD can be distinguished by the slope and the time scale. When the current injected into a LD was reduced to a very low value, the heat generated in the LD chip dissipated to the heat sink. During this process, the temperature at different positions of the LD change over different time scale and different rate. The time scale of the heat dissipation of a LD chip and solder junction were 0–10–4s and 10–4–0.1 s, respectively. Fig. 3 shows the first two periods of the voltage variation with time. The first period is caused by heat dissipation in the LD chip, and the second period is caused by heat dissipation in the solder layer.

Fig. 3. (Color online) The time-resolved voltage variation during the measurement.

Table 1. Parameters of thermal resistance calculation.

Fig. 4. Gold-rich portion of the Au–Sn phase diagram.

Fig. 5. Cross-sectional SEM of the two samples. The red crosses are the EDS measure points.

Table 2. EDS results of the points marked in Fig. 5.

The voltage variation of the solder layer (Vf0–Vft) is 85.37 mV for E09 and 59.05 mV for Y00. Table 1 shows all the parameters of thermal resistance calculation. According to Eqs. (2)and (3), the thermal resistance was 41.95 K/W for E09 and 65.29 K/W for Y00. The total thermal resistance of a LD is determined by chip structure, bonding materials and microstructure, and heat sink. In our study, the chip structure, the heat sink, and the bonding materials are the same, and therefore we focused on the microstructure of the solder layer, as follows.

The gold-rich portion of the Au–Sn phase diagram is shown in Fig. 4[18]. The IMC phases of interest in solder areβ(Au10Sn),ζ’(Au5Sn) phase,ζ(Au5Sn)phase andδ(AuSn) phase.From the phase diagram, the Au80Sn20 alloy system consists ofζ’phase andδphase at room temperature. In practice, however, the nonequilibrium solidification usually results in the formation of primaryζphase. In addition, Teoet al. have also foundβphase in Au80Sn20 solder joint[19]. The eutectic point at 280 °C and 29.0 at.% Sn has the reactionL↔ [ζ+δ]. There is a peritectoid reaction at 190 °C and 16.0 at.% Sn,ζ’↔ [ζ+δ]. Prior to this reaction, it is believed that the reaction at 190°C and 18.5 at. % Sn isζ↔ [ζ’+δ]. Theζ-Au5Sn phase emerges from the peritecticζ↔ [β+L] 9.1 at.% Sn at 521 °C to 17.6 at.% Sn at 280 °C, and 13.9 at.% Sn at 190 °C. The composition of Sn in the hexagonal structureζ’phase is 16%,where it remains until the temperature reaches 190 °C. Theζphase has a Mg-type close-packed hexagonal structure. As the Sn concentration increases, the volume ofζphase per atom will increase. Theδ(AuSn) phase is a hexagonal structure intermetallic compound with a melting point of 419.3 °C.Theβphase is considered as a kind of commercial gold solder which is used as Au-protected surfaces[20–22].

Fig. 5 shows the cross-sectional SEM images of the solder layer in these two samples. The EDS results and the possible phase of the marked points are shown in Table 2. The thickness of solder layer is roughly 4μm. The a1, a2, b1, b2 points are at the LD chip/solder interface region. From the EDS results, it can be found that theδphase is in the same region. Because Sn-rich phase such asδhas a lower surface tension than Au-rich phase,δphase tends to coalesce at the surface[23,24]. During the packaging process, Pt diffused from the LD electrode and coalesced at the LD chip/solder interface. As the EDS data shows, there is Pt–Sn phase in the region around points a1, a2. Also, the solder/heat sink interface has an analogous phenomenon. Under the effect of thermal diffusion, Ni in the heat sink coalesced at the solder/heat sink interface. In these regions, Ni replaced Au in AuSn phase to form (Au,Ni)Sn phase[25]. The gray line on the left part of the interfacial layer at the bottom side of E09 is void, which could be induced during the SEM sample preparation. In the center of the solder layer, the bright phase is Aurich, and the dark phase is Sn-rich. It is notable that most of the Sn-rich phase in sample E09 distributes in the form of spheroidized structure. On the other hand, most of the Snrich phase in sample Y00 is lamellar structure. The hard and brittle nature of the primaryζ’phase which has a dendrite microstructure leads to difficulties in the manufacture of Au80Sn20 solder. According to the phase diagram, Au80Sn20 alloy consists ofζ’phase andδphase at room temperature.The reason for the difference of morphology between two samples may be the different cooling rate. At a fast cooling rate, the dendrite growth ofζ’phase will be suppressed. Furthermore, the suppressed growth results in refined microstructure and metastable phases. At the same time, the dendrites ofζ’phase will generate more fractions. A mass of branches from the fractions are intertwined. The intertwining process divided the lamellar Sn-rich phase into a spheroidized structure. This structure transformation has a good effect on the mechanical properties of the solder[26].

It is suggested that the main reason for the higher thermal resistance in sample Y00 is the lower content of the Au-rich phase. Au-rich phases in the center are the primary phase ζ’ and metastable phase. The Au-rich phase not only has a good mechanical property, but also has a lower thermal resistance. As the content of Au-rich phase in E09 is much higher than that in Y00, E09 has a lower thermal resistance. In addition, the interface also has a great effect on thermal resistance. In this case, the LD/solder interfaces of the two samples are analogous to some extent. However, the content of Ni in the solder/heat sink interface has a remarkable difference. It is believed that Ni comes from the heat sink by thermal diffusion. Since (Au,Ni)Sn is harmful to thermal resistance improvement, the decrease of (Au,Ni)Sn phase in E09 ensures a good thermal contact[27,28].

4. Conclusion

In summary, the thermal resistance of GaN-based blue laser diodes packaged in TO56 cans were measured by the forward voltage method. The microstructures of Au80Sn20 solder were then investigated to understand the reason for the difference in thermal resistance. It was found that the microstructure with higher content of Au-rich phase in the center of solder and lower content of (Au,Ni)Sn phase at the interface of the solder/heat sink resulted in lower thermal resistance. This finding will help improve the packaging processing in the future.

Acknowledgements

This work was supported by the National Key Research and Development Program of China (Grant Nos.2016YFB0401803, 2017YFE0131500, 2017YFB0405000), National Natural Science Foundation of China (Grant Nos. 61834008,61574160, 61804164, and 61704184), Natural Science Foundation of Jiangsu province (BK20180254), China Postdoctoral Science Foundation (2018M630619).

杂志排行

Journal of Semiconductors的其它文章

- S uppression of oxygen and carbon impurity deposition in the thermal system of Czochralski monocrystalline silicon

- Wireless communication and wireless power transfer system for implantable medical device

- A 0.5–3.0 GHz SP4T RF switch with improved body self-biasing technique in 130-nm SOI CMOS

- Defect levels in d-electron containing systems: Comparative study of CdTe using LDA and LDA + U

- A snapback-free and high-speed SOI LIGBT with double trenches and embedded fully NPN structure

- 4H-SiC trench MOSFET with an integrated Schottky barrier diode and L-shaped P+ shielding region