应用于AMOLED源极驱动的具有DAC功能的输出缓冲器设计

2020-09-10邓红辉

孙 蕊,邓红辉*,张 俊,权 磊,贾 晨

(1.合肥工业大学 微电子设计研究所,安徽 合肥 230009;2.深圳清华大学研究院,广东 深圳 518057)

1 引 言

近些年来,由于AMOLED显示面板的各项优势和应用需求日益凸显,用于AMOLED显示的驱动芯片成为大规模数模混合设计领域的研究热点[1]。源极驱动电路是AMOLED驱动芯片的重要组成部分,它将图像数据转换成可以加载在面板像素电容负载上的不同灰阶电压。它包括图像数据转换和输出缓冲,其中使用DAC将图像数据转换为相应的灰阶电压。要使AMOLED面板显示达到较高的分辨率和精度,输入图像数据通常为10 bit数据,所对应的DAC也需要有10 bit的分辨率。综合考虑到10 bit的DAC需要对面积、功耗和精度等进行折中考虑,通常把10 bit的DAC分为两级来实现。一种结构是两级电阻分压DAC结构[2],该结构精度好,面积和功耗适中。另一种DAC实现方式是第一级采用电阻分压DAC,第二级采用插值运放DAC,合理分配两级DAC精度,可以达到芯片面积、功耗、精度之间的折衷。文献[3]采用了7 bit电阻分压DAC加上3 bit插值运放DAC的结构实现。文献[4]采用了6 bit电阻分压DAC加上4 bit插值运放DAC的方式实现。文献[3]的方式实现的DAC误差较小,但芯片占用面积较大;文献[4]方式实现的DAC误差虽然比文献[3]稍大,但芯片占用面积较小。此外,由于AMOLED像素电路的负载对于驱动能力有一定的需求,仅依靠DAC的驱动能力不足以将灰阶电压推送至面板,所以需要输出缓冲器增强驱动能力[3]。

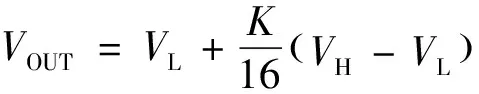

本文采用了文献[4]中6 bit电阻分压DAC加上4 bit插值运放DAC的两级结构,应用文献[3]中的插值运放原理,针对AMOLED源极驱动电路,设计了一种带有4 bit DAC功能的缓冲器,实现4 bit DAC功能和输出缓冲两个目的,达到小面积、高精度和低功耗的设计。

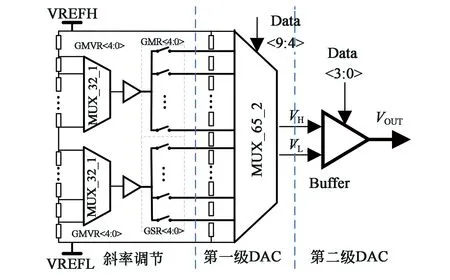

2 源极驱动电路中DAC结构及原理

源极驱动电路作用就是将图像数据转换为灰阶电压。由于显示设备亮度与输入电压的非线性关系以及人眼对于亮度变化的非线性感官,需要进行GAMMA校正。本设计使用10 bit非线性图像数据配合线性DAC,来实现GAMMA校正和源极驱动功能。如图1所示,采用斜率调节单元产生GAMMA校正曲线的两个电压调节点,使输出曲线贴合GAMMA曲线,线性DAC第一级采用6 bit的GAMMA校正电阻串DAC结合第二级4 bit的插值运放DAC来实现功能[5]。第一级的电阻串DAC采用64个阻值相等的电阻分压结合一个65选2的多路选择器构成。高6 bit的图像数据选出第一级DAC的输出电压VH、VL,输出到第二级。本文设计的第二级DAC是带有DAC功能的输出缓冲器。

图1 提出的整体DAC结构Fig.1 Structure of proposed overall DAC

3 电路设计

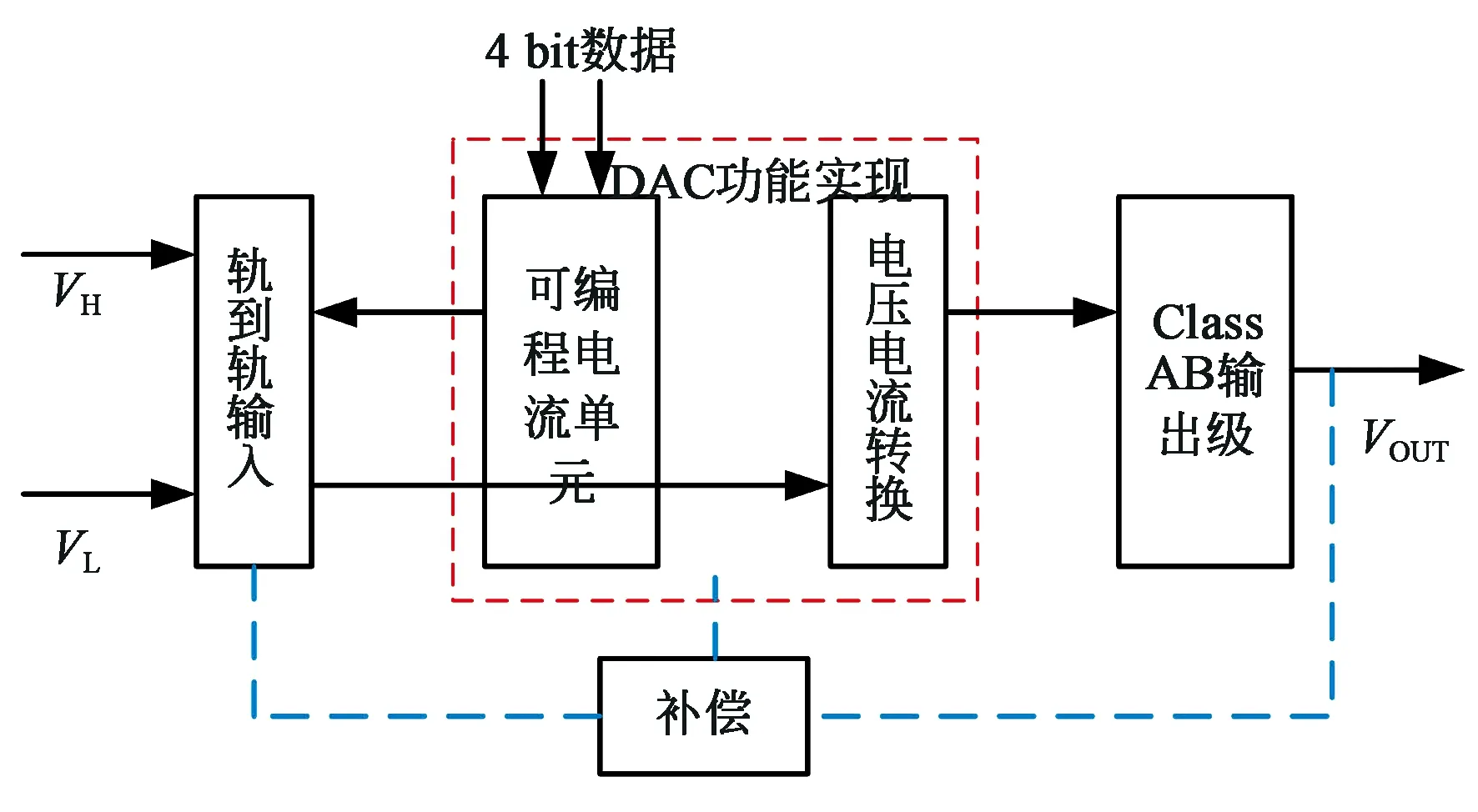

3.1 整体结构设计

所设计的输出缓冲器整体结构示意图如图2所示,由输入级、输出级、可编程尾电流单元以及增益级构成。考虑显示面板所需要的输出电压范围为0.3~6.3 V,电压范围接近电源到地,要求缓冲器能够支持全摆幅范围的输入输出,因此采用轨对轨结构的输入级和输出级。考虑到缓冲器需要有DAC的功能,本设计利用运放差分对管工作在亚阈值区,跨导和电流成线性关系,通过尾电流可编程实现线性插值。考虑输出电压10 bit输出精度的要求,输出电压偏差(<±3 mV)需要比较小,需要缓冲器具有较大的开环增益,增益级采用Cascode结构,通过提高输出阻抗,来提高开环增益,并通过频率补偿电路提高稳定性。此外,考虑实际显示面板上有众多通道,需要减少每一个缓冲器的静态电流。

图2 输出缓冲器系统原理图Fig.2 Block diagram of output buffer system

3.2 缓冲器主要指标

输出缓冲器需要驱动30 pF的电容负载和10 kΩ的电阻负载,并且在一个行扫描周期内完成对像素电路存储电容的充电。由于第一级DAC的驱动能力很小,需要输出缓冲电路来提高灰阶电压的驱动能力。输出缓冲器采用单位增益运放结构,为了提高驱动能力、满足输出电压误差小于±3 mV,要求缓冲器开环增益要达到65 dB以上。本设计应用于1 080×2 160分辨率的AMOLED显示面板,每一行的扫描时间为1/60/2160=7.7 μs,去除第一级DAC建立时间以及预留的时间裕度,输出缓冲器的建立时间应在5 μs以内。由于每个输出通道都对应着一个输出缓冲器,为了降低功耗,输出缓冲器的静态电流应当尽量小。

3.3 输入级设计和DAC功能实现

为了使输入范围尽可能达到电源到地,输入对管使用NMOS对管和PMOS 管并联实现[6]。

NMOS对管和PMOS对管两者并联之后的输入级的输入共模范围为:AVSS≤Vcm≤AVDD,保证了输入级的轨到轨要求。

由于采用互补的PMOS对管和NMOS对管,轨对轨输入运放的输入级等效跨导会随着共模输入电压的变化发生变化,电路的直流增益、带宽和相位裕度会随着等效跨导的变化而变化。轨对轨输入级结构如图3所示。但本文的缓冲器仅用于灰阶电压的建立,并且可以从下文的输出与输入关系得出缓冲器电路输出的灰阶电压与等效跨导之间没有关联性,加入恒定跨导结构[7]会不可避免地增加MOS数目,加大芯片面积,所以不需要加入恒定跨导结构以节省功耗和面积。

图3 轨对轨输入级结构Fig.3 Rail to rail input structure

本文设计的DAC功能的实现单元使用插值运放结构实现[8],如图4所示,包括电压-电流转换器、可编程电流单元和输出级。图4以NMOS差分输入对管为例,阐述4 bit DAC功能实现。

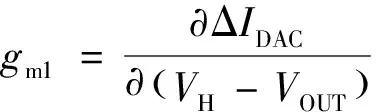

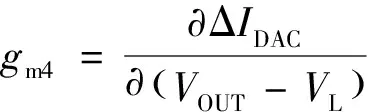

图4 DAC功能实现原理图Fig.4 Principle of DAC function implementation

图4中M1、M2和M3、M4为两对NMOS输入差分对管,M5、M6、M7、M8、M9为尾电流源,可以通过4位数据控制接入电路的尾电流大小。VH、VL是需要插值的高低电压,分别连接M1和M4的栅端,将输出电压VOUT连接到M2和M3的栅极,形成闭环负反馈的单位增益缓冲器。两个差分对大小相同,都被偏置在亚阈值区,差分对管M1和M2尾电流为IBH,差分对管M3和M4尾电流为IBL。尾电流IBH和IBL的大小由电流源M5、M6、M7、M8、M9决定,并通过4位数据D0、D1、D2、D3及其反相信号D0’、D1’、D2’、D3’控制。M5的电流为IU,M6~M8分别产生2IU、4IU、8IU的电流,通过4位数据控制的IBH和IBL,和为16IU,即若IBH=KIU,则IBL=(16-K)IU。两个差分对的电流IDAC施加到电压-电流转换电路和输出级。由于两个差分对工作在亚阈值区,对于差分对等效跨导与输出电压VOUT的关系可以表示为:

(1)

(2)

对于处于亚阈值的MOS管的表达式为:

(3)

由式(1)、(2)联立可知:

gm1(VH-VOUT)=gm4(VOUT-VL),

(4)

又:gm和漏源电流是线性的关系,若IBH=K·IU,则IBL=(16-K)IU,带入式(4)中,可得:

K(VH-VOUT)=(16-K)(VOUT-VL),

(5)

化简后可得:

(6)

K取1,2,3…16。根据图像数据从0000到1111变化选取出16个不同的电压值,具体数值分配见表1。

表1 输入数据与输出电压对应关系Tab.3 Correspondence between input data and output voltage

尾电流源采用电流镜结构实现。通过尾电流源晶体管尺寸的比例关系精确镜像基准电流,确保由D3、D2、D1及D0分别控制的8I、4I、2I及1I电流的精准比例关系,进而保证输出缓冲器插值的精确度。

3.4 输出级电路设计

本文在设计输出级时主要考虑3点:(1)输出电压需要达到轨对轨的要求,因为AMOLED像素电路的驱动灰阶电压范围通常是模拟驱动电路的电源到地;(2)输出瞬态的充放电电流要足够的大,因为输出级需要驱动的等效负载比较大,需要足够大的电流达到快速建立的目的;(3)尽量小的静态偏置电流。综合考虑后,本文采用了前馈式Class AB作为输出缓冲器的输出级。如图5所示,M1和M2组成浮动电压源,二极管连接的M3~M4和M5~M6分别为浮动电压源M1、M2的栅极提供偏置,两个同相信号Iin1和Iin2直接驱动输出管M7和M8,M7和M8漏极相连,负载为容性负载,形成轨对轨输出[9-10]。

图5 Class AB输出级结构Fig.5 Class AB output stage structure

浮动电压源、偏置管及输出管形成两个跨导线性环 M1、M3、M4、M7和M2、M5、M6、M8,形成AB类输出。跨导线性环确定了输出管M7、M8的静态电流,控制两输出管的栅源电压,输出管M7、M8呈推挽式输出,输出电压范围可达电源到地。同时,浮动电压源保证了当一个输出管的电流较大时,另一个输出管的电流能保持一个最小值,从而防止MOS管进入截止状态产生交越失真。

3.5 补偿设计

由于缓冲器应用于显示驱动芯片,需要连接的负载是大电容和电阻的串联,电路的主极点会比较靠近原点,这会带来稳定性问题,需要采取一定的补偿方案。

如图6所示,本文使用了Cascode Miller补偿技术[11-12],将补偿电容置于共源共栅器件的源极和输出节点之间。传统Miller补偿要求在输出管的栅漏两端分别接入补偿电容,由于电容的前馈通路,会引入一个右半平面的零点,该零点减小了相位裕度,限制了单位增益带宽。Cascode Miller补偿在保留了传统Miller补偿极点分离效果的同时,避免了传统Miller补偿引入的右半平面零点,用较小的补偿电容实现了频率补偿。同时,负载电阻的大小为10 kΩ,将负载电阻作为零点补偿电阻可以起到很好的频率补偿作用,进而减小补偿电容CC的值。

图6 带补偿的缓冲器结构Fig.6 Compensated buffer structure

3.6 整体电路设计

整体电路结构图如图7所示。MP1、MP2、MP3、MP4、MN1、MN2、MN3、MN4为输入对管,输出连接反向输入端构成单位增益负反馈结构,悬浮电流源MP10、MN10设置为与悬浮电压源MP11、MN11相同的结构,呈现对称互补结构,这种结构匹配性较好。同时运放的补偿采用Cascode Miller补偿,使用较小的电容就能达到补偿效果,频率特性好,使缓冲器工作在稳定状态。由于输入对管都是工作在亚阈值区,静态电流较小,实现低功耗。同时,将DAC和缓冲功能集中在一个电路上,节约了大量的芯片面积。

图7 整体电路结构图Fig.7 Overall circuit structure diagram

4 电路版图和仿真结果

采用了UMC80 nm的工艺对整个1 080×2 160分辨率的AMOLED源极驱动电路进行了设计,其中包含2 160个源极驱动单元,每个驱动单元都有一个带有DAC功能的低功耗输出缓冲器,带有DAC功能的低功耗输出缓冲器版图(包含偏置电路)如图8所示。

图8 输出缓冲器版图Fig.8 Output buffer layout

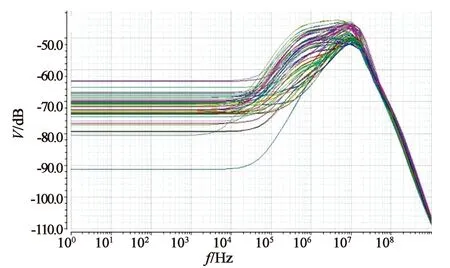

输出缓冲器输入输出电压范围都为0.2~6.3 V,面板等效负载R=10 kΩ,C=30 pF。在电源电压为6.5 V条件下,对输出缓冲器进行PVT仿真,其幅频和相频特性曲线如图9和图10所示。可以看出,在输入电压范围内,输出缓冲器的直流增益在70 dB以上,相位裕度在60°以上,可以保证输出缓冲器闭环环路的稳定性。在典型工作的3.3 V左右时,增益可达129 dB,相位裕度75°,增益带宽9.4 MHz,增益满足设计要求、稳定性高。

图9 输出缓冲器幅频曲线Fig.9 Output buffer amplitude frequency curve

图10 输出缓冲器相频曲线Fig.10 Output buffer phase frequency curve

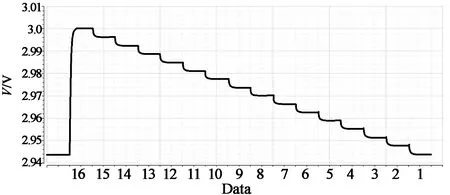

在中压输入范围内使用两个相差60 mV的输入(3~2.94 V)时,将4 bit图像数据从1111到0000依次跳变可以得到输出缓冲器的输出结果如图11所示,可以看出,缓冲器实现了4 bit DAC功能。

图11 输出缓冲器DAC功能实现Fig.11 Output buffer DAC function implementation

对输出结果进行采点取值并与表1所得的理论值进行比较,可以得到输出结果的误差如图12所示。在中压输入范围内,通过插值得到的电压与理论值之间的最大误差为0.255 mV,误差均值0.153 mV。对于低压和高压输入范围同样进行上述仿真,可以得到低压输入(80 mV)情况下最大误差为0.640 mV,误差均值为0.406 mV;高压输入(100 mV)情况下最大误差为2.041 mV,误差均值为0.941 mV。仿真结果表明本文的插值缓冲器实现的DAC满足误差小于3 mV,并且符合本设计的三段式DAC曲线在中压范围精度最高、低压其次、高压精度最低的要求,在0.2~6.3 V的宽输入范围内均具有良好的精度和线性度。

图12 输出缓冲器DAC误差Fig.12 Output buffer DAC accuracy

对输出缓冲器的电源抑制比进行了仿真,如图13所示。低频时,电源抑制比为70 dB;1.6 MHz时,电源抑制比依然有50 dB。对输出缓冲器的建立时间进行了仿真,如图14所示,达到精度90%时,从0.2 V到6.3 V的建立时间为1.49 μs;达到精度99%时,建立时间为2.49 μs;达到精度99.9%时,建立时间为3.5 μs。

图13 输出缓冲器电源抑制比Fig.13 Output buffer power supply rejection ratio

图14 输出缓冲器建立时间Fig.14 Output buffer settling time

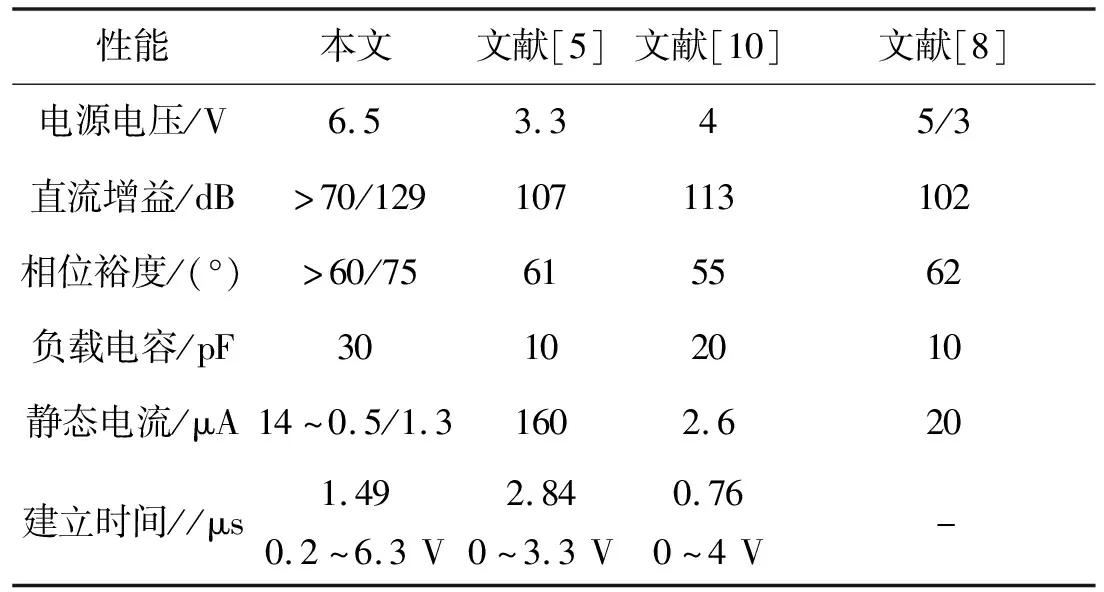

表2列出了其他输出缓冲器设计中轨对轨缓冲器的性能,通过对比可以看出本文的轨对轨缓冲器在宽输入电压范围内建立时间快、静态电流小。

表2 本文缓冲器性能与其他设计比较Tab.2 Comparison of buffer performance with other designs

5 结 论

本文基于UMC80 nm的CMOS工艺,设计了一种应用于AMOLED显示驱动芯片的带有DAC功能的高性能输出缓冲器。本文设计的缓冲器在整个输入共模电压范围(0.2~6.3 V)内增益大于70 dB、相位裕度都在60°以上,静态电流较小,还具有高精度4 bit DAC性能,误差小于指标要求的3 mV,满足了1 080×2 160分辨率AMOLED源极驱动电路对于输出缓冲器的要求。