一种星载可配置输出频率的X波段载波源

2020-09-03谌德军梁显锋

谌德军,宋 嵩,梁显锋

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院大学,北京 100190;3.Synopsys(北京)有限公司,北京 100086)

0 引言

目前,应用于星载数传发射机的载波源主要采用整数分频锁相环的方案[1],载频的频点较固定,一旦卫星发射便无法实现载频的灵活可变。文献[2]提出了一种星用X波段数传发射机,其载波源输出频点是由本地恒温晶振产生的基频信号经整数分频锁相环倍频65倍而获得。萤火一号火星探测器的X波段发射机载波源采用环内混频的整数锁相环方案,频率步进为1.359 8 MHz[3]。上述频率合成方案产生的载频频点基数小,间隔大,难以满足科学实验卫星在其他频点的数据传输通信试验。对此需考虑一种小步进输出频率的载波源方案,通过地面站发送遥控指令,星地数传通信载波频率便可实现重新配置,为我国后续开展相关空间科研活动奠定基础。频率合成技术的实现方案主要有两种:

1) 利用锁相环(PLL)技术的间接频率合成方案。

2) 利用直接数字频率合成(DDS)技术的直接频率合成方案。

第1)种方案具有输出频率范围宽及频谱纯度高等优点,但是频率分辨率较低;第2)种方案可实现极高的频率分辨率,但通常适用于输出频率较低的应用且杂散抑制度较差[4-6],将DDS和PLL技术进行综合应用可优势互补。由于我国宇航级DDS芯片技术还不成熟,难以适应空间辐射环境,设计一种替代专用DDS芯片功能的电路意义重大。

采用现场可编程门阵列(FPGA)和数模转换器(DAC)芯片实现DDS电路,与整数分频PLL集成应用,提出了一种应用于星载数传发射机的输出频率可配置的载波源方案,并采用商业芯片研制了载波源样机。对载波源的核心参数指标进行了分析及测试,满足设计指标要求,证明了方案的可行性。

1 总体方案

星载可配置输出频率的X波段载波源关键技术指标为8.025~8.4 GHz,频率步进100 Hz,相位噪声小于-60 dBc/Hz@100 Hz、-70 dBc/Hz@1 kHz、-80 dBc/Hz@10 kHz、-90 dBc/Hz@100 kHz、-110 dBc/Hz@1 MHz,杂散抑制小于-65 dBc,超过了国军标GJB2207-94关于卫星数据传输系统载波源指标的要求[7]。

方案中系统功能模块主要包括DDS模块、PLL模块、稳压电源模块、低通滤波模块及FPGA控制模块,系统框图如图1所示。图中,LPF表示低通滤波器,VCO表示压控振荡器,PD表示鉴相器,OCXO表示恒温晶振,SPI表示串行外设接口。采用OCXO作为DDS的参考时钟,用于获得优异的频率稳定度和相位噪声性能。由于专用DDS芯片无法适应空间应用环境,采用FPGA和DAC芯片搭建电路实现DDS功能,通过改变FPGA中只读存储器(ROM)波形查找表的内容及频率控制字参数产生所需波形。但是DDS几乎由数字部件组成,杂散抑制能力较差,因此,抑制DDS输出杂散成为需解决的重要难题。OCXO输出频率通过DDS方式得到高精度可变信号,经滤波后作为PLL的参考频率,FPGA通过SPI串口配置PLL中PD的鉴相频率,使载波源输出8.025~8.4 GHz的中心频点。

图1 星载可配置输出频率的X波段载波源系统框图

2 实现方案

2.1 DDS电路设计

DDS电路由Spartan-6系列的FPGA芯片、数模转换芯片AD9744、100 MHz恒温晶振MDF28S2S及相关外围电路组成,选用纹波系数小的低压差线性稳压器(LDO)为芯片提供工作需要的二次电源。Spartan-6系列芯片是Xilinx公司的低功耗、低成本的FPGA芯片,AD9744是ADI公司的14-bit高速数模转换器芯片,最大采样速率达到210 MS/s。在DDS电路设计中,FPGA芯片内嵌锁相环将OCXO产生的100 MHz参考信号倍频至200 MHz,其中一路通过缓冲器后作为AD9744的差分时钟信号,另一路作为相位累加器的采样时钟,在频率控制字的控制下,相位累加器输出相应的相位码,ROM波形查找表将相位码信息转化为波形量化采样值,通过14路并行数据线驱动AD9744生成相应频率的差分正弦模拟信号,由变压器ADTT1-1转化成频率为38.2~40 MHz时的任意频点正弦模拟信号。

DDS在FPGA内的实现主要包括ROM查找表的设计和相位累加器的设计。由于正弦波具有对称性,仅需将1/4周期正弦函数的数据存储在ROM中,通过象限和符号补偿即可生成剩余3/4周期波形数据,并将相位累加器输出的高10位相位码设置为ROM查找表地址,节省了ROM空间。利用ISE软件自带ROM的IP核实现ROM的设计,在MATLAB中编写所需正弦波的代码并生成ROM初始化文件.coe文件,由于DAC无法输出负电压,因此需将正弦波的负值部分抬升到0~1之间,最终将.coe文件导入ROM中,完成ROM查找表的设计。相位累加器的位数决定了DDS的频率分辨率。假设相位累加器的位数为N,频率控制字为K,系统时钟为fSYSCLK。那么DDS的频率分辨率为

Δf=fSYSCLK/2M

(1)

DDS的输出频率为

(2)

FPGA芯片内部的相位累加器位数为32位,即M=32,理论上K是介于1~(231-1)之间的任意整数。由式(1)可知,在fSYSCLK=200 MHz时,Δf=0.047 Hz。由式(2)可知,改变K的大小可控制DDS的输出频率。根据DDS所需输出频率值可推算出K值,对程序中K值进行更改,通过JTAG接口将程序下载到FPGA,实现DDS输出频率的灵活配置,FPGA的SPI配置方式如图2所示。同时,将程序固化至通过串行外设接口进行操作的闪存芯片(SPI Flash),下次断电重启便可由闪存芯片(Flash)自动配置程序。

图2 FPGA的SPI配置方式

载波源输出信号杂散主要来源于DDS固有杂散,是由DAC非线性、幅度及相位截断误差等因素造成的,其中DAC的非线性因素起主导作用[8]。DDS的参考信号与输出信号发生交叉调制,从而形成自身固有杂散。杂散分量满足下式,即

fs=αfc±βfo

(3)

式中:fs为DDS输出信号杂散分量频率;fc为DDS输入参考频率;fo为DDS输出信号频率;α和β为阶数。α和β的值越大,则DDS输出信号杂散分量越小。实际应用中,基本只考虑三阶。如本方案中DDS的参考频率为200 MHz,DDS的最大输出频率为40 MHz。式(3)中,当α=1,β=3时,杂散信号频率为80 MHz,距离40 MHz频点最近。

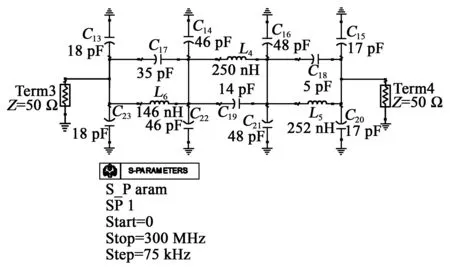

为获得纯净的DDS输出信号,需在DAC的输出端增加无源低通滤波电路,实现平滑滤波功能。与巴特沃斯滤波器和切比雪夫滤波器相比,椭圆滤波器的过渡带更窄、更陡峭,且在相同阻带抑制条件下,椭圆滤波器要求的阶数最低。根据上述分析,使用ADS软件设计了一款椭圆滤波器。

经多次调整优化,所得椭圆滤波器的拓扑结构和仿真结果如图3、4所示。由图4可知,该滤波器的通频带为0~46 MHz,阻带抑制度大于60 dB,能很好地抑制带外杂散。

图3 椭圆滤波器拓扑结构图

2.2 PLL电路设计

PLL电路由频率合成器芯片ADF5355及相关外围电路组成,选用纹波系数小的LDO芯片ADM7150提供工作需要的二次电源。ADF5355是ADI公司集成VCO的微波宽带频率合成器芯片,可输出54 MHz~13.6 GHz的信号,片内寄存器可通过三线SPI串口进行配置。通过FPGA芯片的SPI串口配置ADF5355的鉴相频率等于输入参考频率,并设置分频系数为210,环路锁定后,VCO的输出经片内2倍频输出8.025~8.4 GHz的中心频点。由于PLL起到210倍的倍频作用,因此,载波源的频率分辨率为DDS频率分辨率的210倍,即9.87 Hz。

环路滤波器的性能好坏决定了PLL的环路稳定性、锁定时间及输出信号的相位噪声和杂散抑制度等参数[9]。相位裕度和环路带宽是衡量环路滤波器性能的关键参数。相位裕度表征闭环系统的相对稳定性,一般为45°~60°。环路带宽表征环路对噪声的抑制作用,对输入参考信号的相位噪声表现为低通滤波特性,对VCO的相位噪声表现为高通滤波特性,需折中选取环路带宽。ADF5355的电荷泵输出电压能满足VCO的调谐电压,并且有源环路滤波器会因运算放大器等有源器件恶化PLL输出相位噪声,因此,采用无源滤波器进行设计。

环路滤波器的阶数越多,滤波器的过渡带越窄、越陡峭,性能越接近理想滤波器,但系统的稳定性会变差,通常采用三阶环路滤波器进行设计。本设计由ADIsimPLL软件来完成,设置环路滤波器的相位裕度为53°,环路带宽20 kHz,滤波器阶数为三阶,经仿真优化后所得环路滤波器电路如图5所示。

图5 环路滤波器电路图

载波源相位噪声根据PLL环路滤波器带宽可分为两种:

1) 频率偏移量小于环路滤波器带宽的相位噪声称为带内相位噪声。

2) 频率偏移量大于环路滤波器带宽的相位噪声称为带外相位噪声。带内相位噪声主要取决于输入参考信号的相位噪声、鉴相器引入的鉴相噪声及电荷泵引入的1/f噪声等因素,带外相位噪声主要取决于VCO自身相位噪声。下面主要分析偏离载波频率1 kHz处的带内相位噪声。

ADF5355芯片内部集成了鉴相器功能电路,在整数分频模式,归一化本底噪声Ffloor=-223 dBc/Hz,闪烁噪声本底噪声Fflick=-256 dBc/Hz。

经过计算可知,鉴相器对PLL的噪声贡献为

PNpd=Ffloor+10lgfpd+20lgN=

-106.7 dBc/Hz@1 kHz

(4)

式中:fpd为鉴相器频率,与输入参考频率相等;N为分频系数。

闪烁噪声对PLL的噪声贡献为

PNflick=Fflick-10lgfoffset+20lgfVCO=

-93.87 dBc/Hz@1 kHz

(5)

式中:foffset为频率偏移量;fVCO为VCO的输出频率。

输入参考信号对PLL的噪声贡献为

PNref=PNDDS+20lgN=

-86.4 dBc/Hz@1 kHz

(6)

式中PNDDS为DDS输出频率相位噪声。

由测试结果可知,DDS在输出频率为38.5 MHz时,其PNDDS约为-116.95 dBc/Hz@100 Hz、-126.81 dBc/Hz@1 kHz、-129.13 dBc/Hz@10 kHz,则总相位噪声为

-85.65 dBc/Hz@1 kHz

(7)

由于VCO输出需倍频获得8.085 GHz信号,即相位噪声会恶化6 dB,因此,系统最终相位噪声约为-79.65 dBc/Hz@1 kHz。

综上所述可知,载波源输出频率为8.085 GHz时偏离载波1 kHz的相位噪声约为-79.65 dBc/Hz。同理,可计算出载波源输出频率为8.085 GHz时偏离载波100 Hz和10 kHz的相位噪声分别为-69.77 dBc/Hz和-82.5 dBc/Hz。

2.3 可靠性设计

DDS模块电路与PLL模块电路分别在两块PCB上实现,并通过屏蔽盒进行物理隔离,FPGA通过穿心电容对PLL寄存器进行配置,用于降低数字信号与微波信号间的相互干扰。为提高载波源的集成度,将DDS模块及其二次电源电路、低通滤波器集成在一块PCB上,选取FR4板材,采用4层板设计,板厚1.6 mm。FPGA与DAC间的并行数据线走线保持等长,确保各个数据线上的延迟接近。PLL模块的PCB选取损耗系数小的微波板材Rogers6010,采用双面板设计,板厚0.64 mm。微波板相关电路走线均在顶层完成,底层为大面积金属地,与屏蔽盒接触,并多打接地过孔,实现良好接地。

3 测试结果

根据上述载波源方案完成了星载可配置输出频率的X波段载波源的研制,实物照片如图6所示,尺寸为200 mm×70 mm×30 mm,整机功耗为3.8 W。

图6 X波段载波源实物图

利用安捷伦N9030A频谱分析仪对载波源的DDS模块性能及载波源整机性能进行了测试。其中,DDS模块主要性能指标如表1所示。整机的相位噪声测试结果如图7所示。

表1 DDS电路模块主要性能指标

图7 输出频率为8.085 GHz的相位噪声测试图

由图7可知,载波源在8.085 GHz频率处的相位噪声为-67.03 dBc/Hz@100 Hz、-75.87 dBc/Hz@1 kHz、-81.37 dBc/Hz@10 kHz 、-98.19 dBc/Hz@100 kHz、-121.41 dBc/Hz@1 MHz。

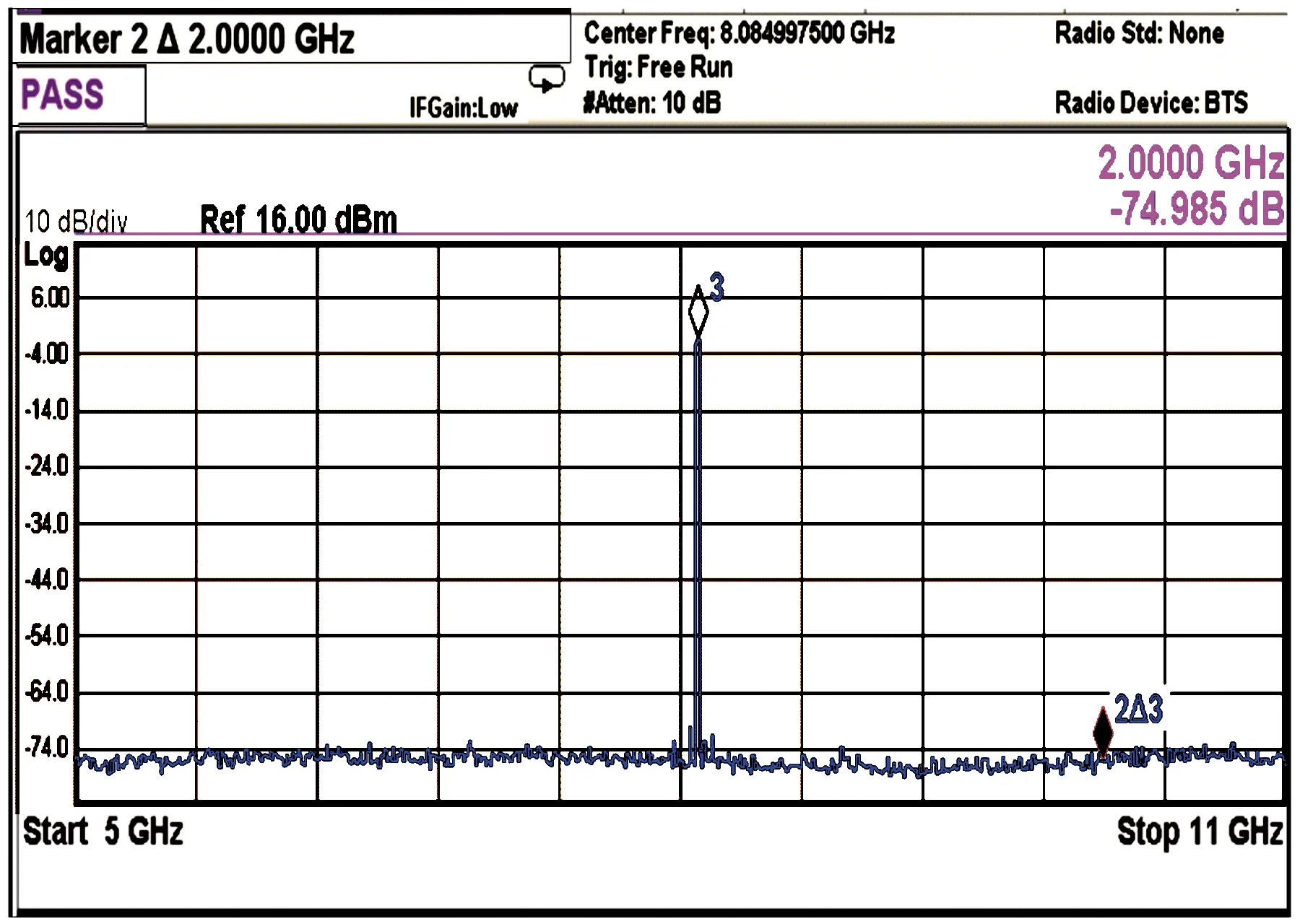

与理论计算结果相比,实测结果与理论值相差约2 dB。这是因为理论值是在理想条件下计算获得的,而实际应用中的电阻、电容等元器件会引入热噪声,以及电源引入的噪声也会恶化相位噪声。杂散抑制测试结果如图8所示。在频谱分析仪的显示带宽设置为6 GHz时,频率源的远端杂散抑制度接近-75 dBc。

图8 输出频率为8.085 GHz的杂散抑制频谱图

4 结束语

在FPGA结合DAC实现DDS的基础上,激励整数分频PLL实现了星载可配置输出频率的X波段载波源样机的设计,载波源兼顾小型化、低杂散、小步进等优点,测试结果满足设计指标要求,验证了载波源方案的可行性,为卫星数传发射机提供了一套可灵活配置频率的载波源方案。采用相位噪声性能更好的DAC芯片可设计出相位噪声更低的DDS电路模块。通过选取合适频段的PLL,该DDS电路模块方案还适用于S、Ku及Ka波段星载数传发射机,具有通用性。