K波段超低杂散捷变频频率合成器的设计

2020-08-26于忠吉张兴稳

于忠吉,张兴稳,孙 彪

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

频率合成器是无线电系统中的核心部件,被广泛应用于通信、雷达、电子对抗等领域,直接影响着整机的性能。随着无线系统的要求逐渐严格以及电子、工艺等行业的发展,原先频率合成器在指标上已逐渐不满足应用需求,尤其是当多个无线系统同时工作时,存在着严重的电磁干扰现象,即一个无线系统的输出杂散会影响到另一个无线系统的接收指标。因此具备超低杂散性能的细步进、宽带捷变频频率合成器已经逐渐成为一个研究热点。

本文根据需求,提出了一种基于混合频率合成的设计方案,对其进行了理论分析与ADS建模仿真,并采用该方案完成了一款K波段频率合成器的设计与制作。该频合器具有杂散低、带宽广、跳频快等优点,其主要指标如下:

(1) 杂散小于等于-75 dBc;

(2) 切换时间小于150 ns;

(3) 功率大于15 dBm;

(4) 带宽4 GHz;

(5) 20 GHz处的相位噪声优于-100 dBc/Hz@1 kHz。

1 频率合成器原理方案

1.1 方案设计

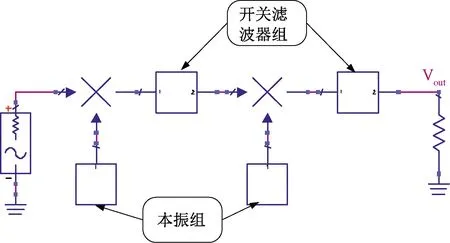

频率合成技术可以分为以下4种[1-2]:直接模拟合成(DAS)、模拟锁相式合成、直接数字合成(DDS)[3]与混合频率合成技术。直接模拟频率合成技术的主要优点是频率切换快、相噪低,但其成本高且体积大;锁相环频率合成技术具有成本低、切换频率方便等优点,缺点是切换时间比较长;直接数字合成技术的优势是分辨率高、频率切换速度快,缺点是输出频率低、相噪高。结合以上几种合成方案的优缺点以及指标要求,本文提出了一种基于DDS+DAS的混合频率合成方案,如图1所示。

图1 毫米波频率源设计原理图

该方案中的射频电路主要分为5个部分:DDS、一次本振组、一次混频及滤波放大、二次本振组、二次混频及滤波放大。DDS输出100 MHz(200~300 MHz)带宽低杂散中频信号,经过第1次混频后输出1 GHz带宽低杂散射频信号,滤波放大后再次上混频至K波段,同时带宽扩展为4 GHz。该频合器的设计难度在于同时满足百ns级宽带捷变频要求与-75 dBc的超低杂散要求。

1.2 关键技术分析

1.2.1 超低杂散DDS技术

一般情况下,DDS 由相位累加器、相幅转换器、数模转换器和低通滤波器组成。相较于传统的直接频率合成与间接频率合成[4-5],DDS采用了数字结构,具有以下特点:

(1) 频率分辨率极高,DDS的输出频率如下式所示:

(1)

式中:WFT为频率调谐字(FTW),是介于0 和(2N-1) 之间的整数;N为相位累加器位数。

当K=1时,输出频率即为DDS的最小步进,一般小于1 Hz。

(2) 相对带宽较宽,工程上DDS的输出频率范围一般为DC~40%×fclk。

(3) 频率切换时间短,一般在100 ns左右。

以上特点决定了它是宽带细步进捷变频频合器中的重要组成部分,但同时其数字结构带来的杂散问题也制约着输出杂散性能。DDS杂散的主要来源有:

(1) 相位截断误差:指由于查表时N位的相位累加器低B位被忽略,导致相位值产生的误差。主信号Sc与相位截断产生的最大杂散Sspur比值范围可表示为:

(2)

从上式可以看出,有效寻址位数每增加1位,杂散性能约提高 6 dB。

(2) 幅度量化误差值:实际只读存储器(ROM)的正弦波幅度量输入到数模转换器(DAC)进行波形重建时,与理想幅度值之间的误差叫做幅度量化误差,可用输出信号量化噪声比(SQR)来衡量:

RSQ=1.76+6.02B+10 lg(fclk/f0)

(3)

式中:B为幅度量化位数。

由式(3)可知,通过增加幅度量化位数与参考频率fclk可以减小幅度量化误差。

(3) D/A转换非理想性误差:实际的DAC存在不同程度的非线性,导致输出的信号中出现谐波杂散叫做D/A转换非理想性误差。

本文选取了ADI公司的AD9914芯片。该芯片是一款带12位DAC的直接数字频率合成器,具有16位相位调谐分辨率,12位幅度调整,宽带无杂散噪声动态范围(SFDR)<-50 dBc等特点,其本身D/A转换非理想性误差较小,且DAC位数高,引起的幅度量化误差也相对较小,具有业界领先的杂散抑制性能。经过DDS评估板实测结果确认,在输入参考频率3.4 GHz、输出200~300 MHz中频信号时,其近端杂散小于-76 dBc,满足本文使用要求。

1.2.2 低杂散频段扩展技术

因为受限于DDS输出绝对带宽窄,所以需要进行带宽扩展以实现宽带性能指标。常用的带宽扩展方案有2种:

(1) 倍频扩展方案,如图2所示。直接对DDS输出频率倍频,电路结构简单,但是会引起杂散与相位噪声的恶化,步进也会变宽。

图2 倍频扩展方案

理想倍频器的输出相噪可表示为:

Lout=Lref+20lgN

(4)

式中:Lout为输出信号相位噪声;Lref为输入参考信号相位噪声;N为倍频系数。

即倍频后信号相位噪声恶化20lgN(dB),杂散恶化程度与此一致。

(2) 混频扩展方案,如本方案图1所示。不同的本振频段可以混出不同的射频频段,以达到带宽扩展的目的,同时产生的高阶交调与本振泄露可通过后级开关滤波器组滤除,即通过合理配置本振点及滤波器,频段扩展后的射频信号杂散不会恶化,步进也不会变化。此外,对于理想混频器,其输出信号相位噪声为2个不相关的输入信号相噪相加:

L(f)=10lg(Sφ1(f)+Sφ2(f))

(5)

本方案中的杂散指标要求极高,采用直接倍频,或者混频加倍频的方案都会引起杂散恶化,无法达到指标。在本方案中,对于DDS输出信号,第1次变频时选取5个本振点,滤出上下变频信号,实现10倍带宽扩展,达到1 GHz。在二次变频时,选取4个本振点,将带宽扩展至4 GHz,同时信号上变频至K波段。

1.2.3 快速频率切换技术

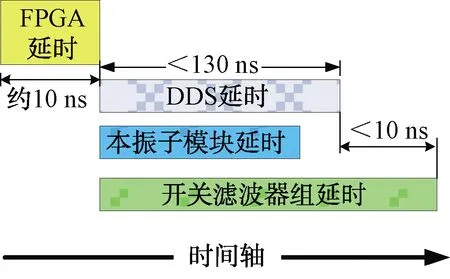

影响整机频率切换的时间主要为:DDS延时、开关滤波器组延时与本振频点切换延时。

开关滤波器组的原理图如图3所示,包括开关延时与滤波器延时。开关延时与DDS延时并行,仅滤波器延时会叠加在总延时中。所选取的带通滤波器延时在10 ns以内。

图3 开关滤波器组原理框图

同时,为达到100 ns以内的本振频点切换时间,本振子模块采用射频开关切换多个点频锁相环(PLL)电路的方案实现,其电路原理图与图3类似。该电路的时延仅受限于射频开关,可以控制在50 ns以内。

综上,该频合器切换时间可参照图4计算:现场可编程门阵列(FPGA)延时约10 ns,DDS延时约130 ns,开关滤波器组中的滤波器延时小于10 ns,最大延时可控制在150 ns以内。

图4 频率切换时间图

2 仿真验证

2.1 PLL电路仿真与计算

本振子模块由多个点频PLL组成,PLL的相噪与杂散严重影响着最终的输出相噪和杂散。对于锁相环输出信号,在环路带宽以内的相位噪声可采用以下公式近似计算:

L(f)≈L(1 Hz)+10lgFp+20lgN

(6)

式中:L(1 Hz)为鉴相器的基底噪声;Fp为锁相环鉴相频率;N为倍频系数。

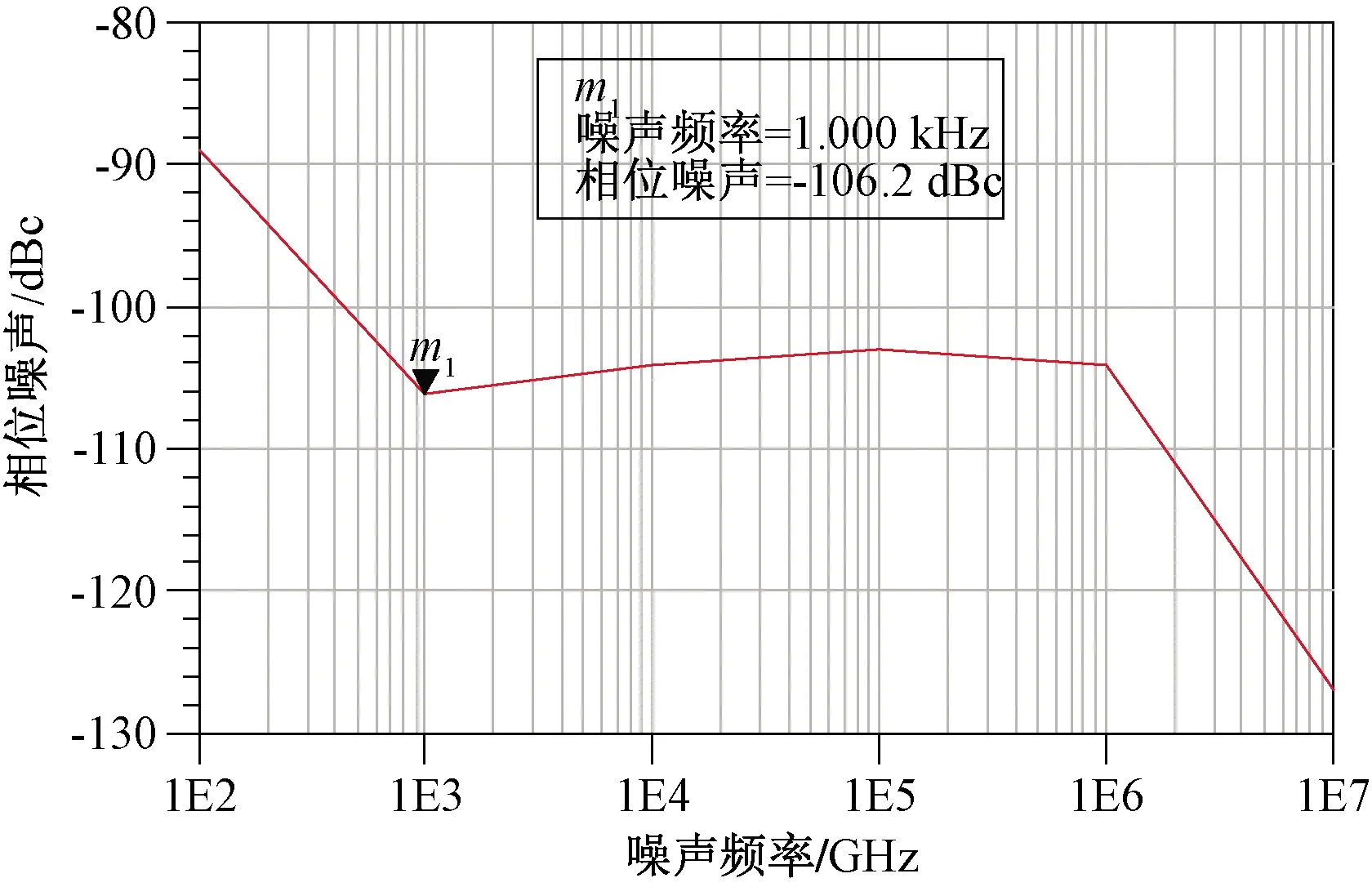

由上式可知,为减小二次本振的相位噪声,可以通过提高鉴相频率,减小倍频系数的方法来实现。使用ADIsimPLL对低频PLL电路仿真,鉴相芯片为HMC704Lp4,鉴相频率为100 MHz,环路带宽1 MHz,输出频率2.7 GHz。仿真结果如图5与图6所示。

图5 PLL电路相位噪声仿真结果

图6 PLL电路杂散仿真结果

从图中可以看出,2.7 GHz的相位噪声小于-110 dBc/Hz@1 kHz,杂散小于-100 dBc。而DDS在3.4 GHz参考频率下,200~300 MHz输出频点的相噪小于-130 dBc/Hz@1 kHz,根据公式(5)可得,一次混频输出相噪近似为一次本振相噪-110 dBc/Hz@1 kHz。二次本振的鉴相器选用HMC698LP5,提高鉴相频率,仿真得到环路带宽内相噪约-107 dBc/Hz@1 kHz,最终K波段信号相噪约为-106 dBc/Hz@1 kHz。

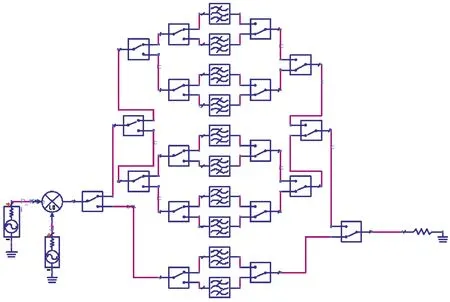

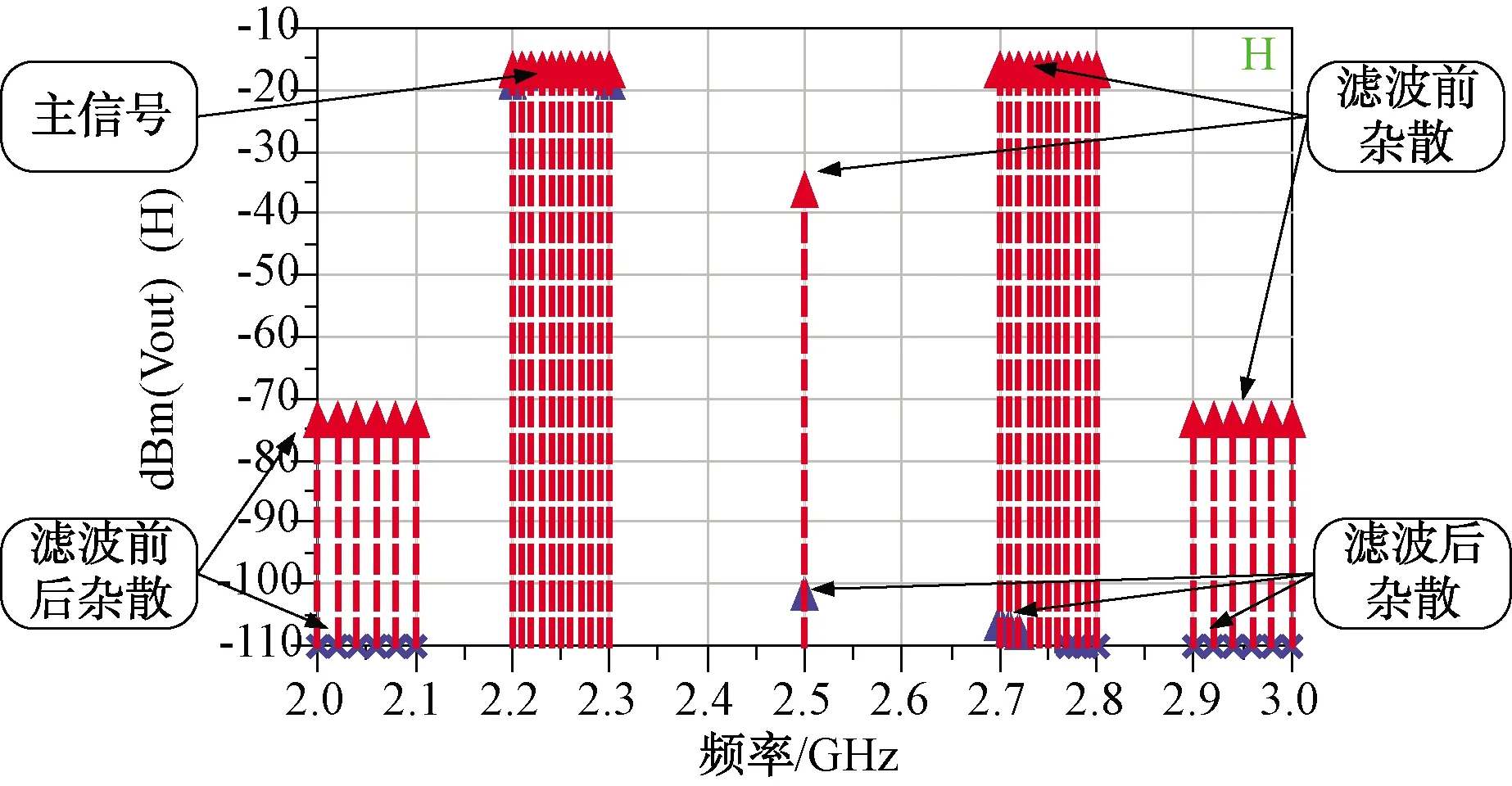

2.2 开关滤波器组仿真结果

本方案通过二次混频的方法来扩展射频带宽,其输出杂散、镜像信号、本振泄露等与输出频段存在重叠,严重影响输出信号的杂散指标,需采用开关滤波器组对信号分段滤波[6-7]。

图7所示为低频开关滤波器组ADS仿真电路模型,图8是经过开关滤波器组前后信号频谱的对比图。图8中2.2~2.3 GHz为其中一个通道的主信号,2.5 GHz为本振泄露,2.7~2.8 GHz为镜像频段,其余为混频交调杂散。滤波前本振泄露约为-15 dBc,交调杂散约-50 dBc,经滤波后,所有杂散信号均降低至-80 dBc以下。高频开关滤波器组电路与此类似。

图7 低频开关滤波器组仿真电路图

图8 开关滤波器组输入输出信号对比

2.3 电路联合仿真

在ADS中将两级开关滤波器组与两级本振电路封装成模块后进行仿真,电路图如图9所示。

图9 频合器ADS仿真模型

图10为19.9~20 GHz频段杂散仿真结果,输出最大杂散为两次混频的本振泄露信号,最差约-85 dBc。图11为20 GHz载波相位噪声仿真结果,约-106 dBc/Hz@1 kHz,仿真结果与理论分析相符,满足使用要求。

图10 部分频段输出杂散

图11 20 GHz载波相位噪声

3 测试结果

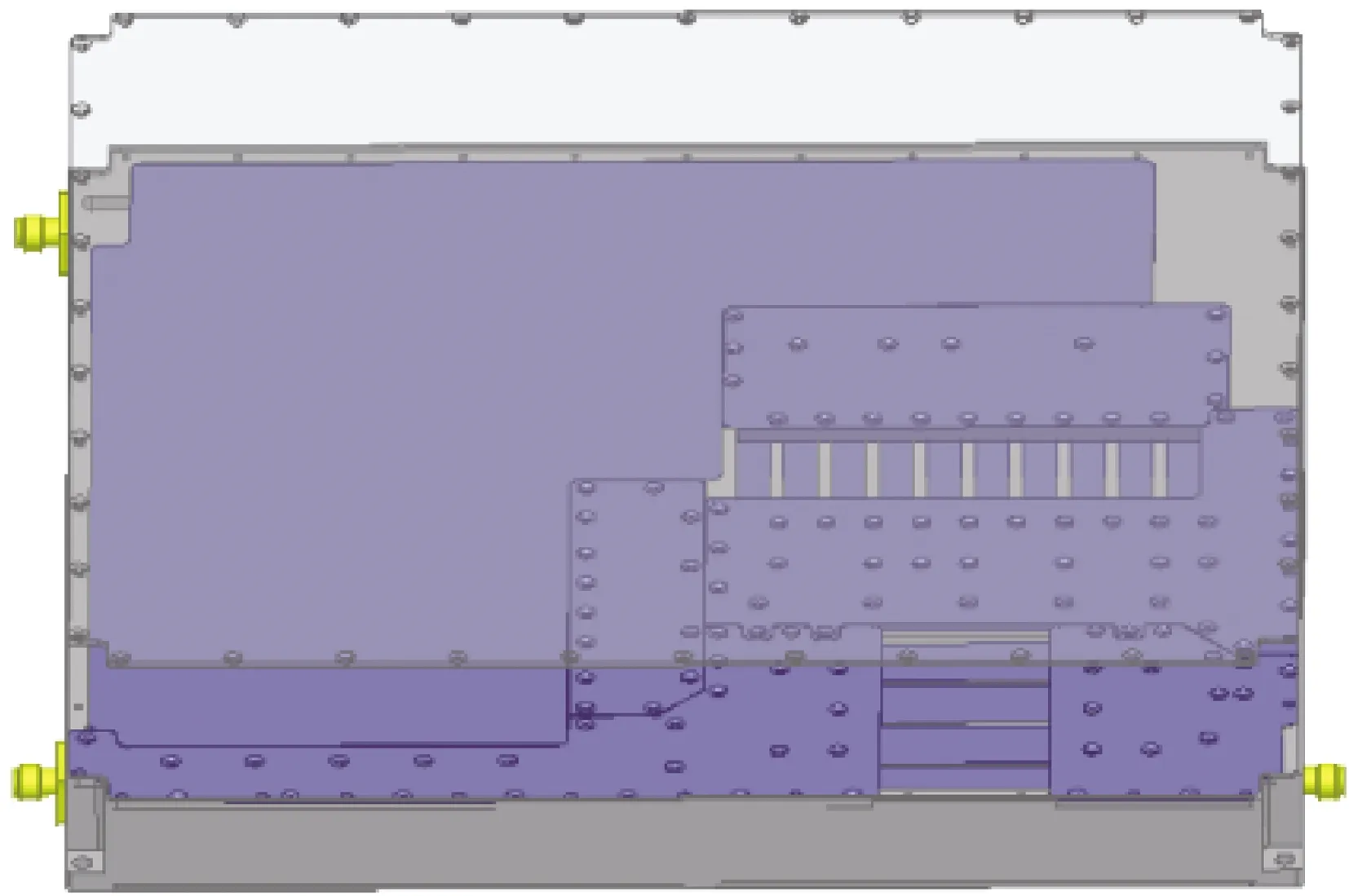

根据上述分析与仿真模型设计电路,制作出一款频合器。该组件的三维模型图如图12所示,其尺寸为200 mm×220 mm×20 mm。

图12 频合器三维模型

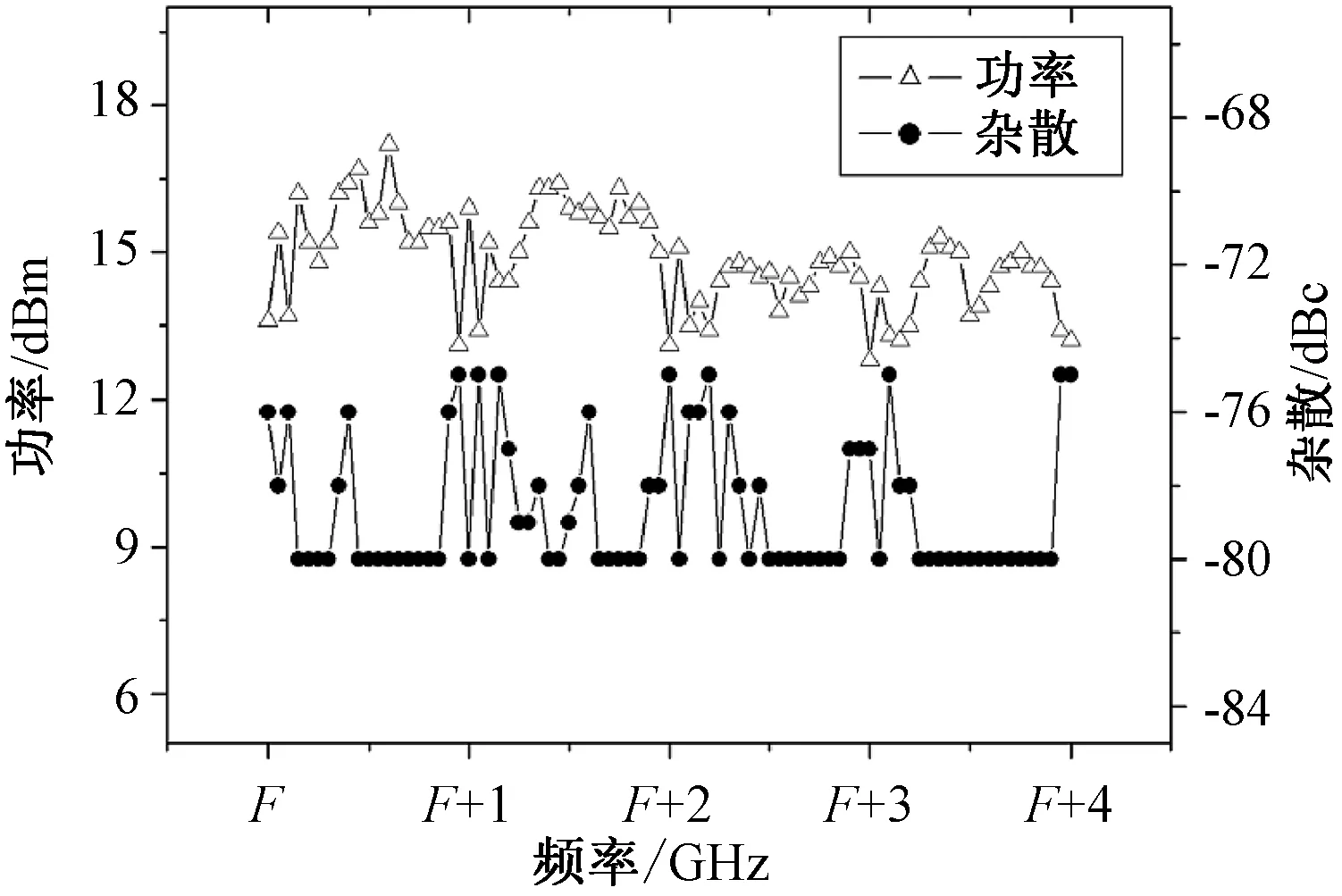

图13所示为功率与杂散测试结果:输出功率范围为15±2 dBm,扣除线损后,所有频点功率均>15 dBm;所有杂散≤-75 dBc,其中5%频点接近-75 dBc。杂散的指标比仿真结果略差,其原因是:(1)通道间隔离度与开关隔离度不够理想,导致滤波器实际性能与理论相比略差;(2)滤波器带内不平坦,导致部分频点主信号功率较低,杂散相对值变大。从图13中可以明显看出,功率较低点与杂散较差频点相吻合。

图13 杂散与功率实测结果

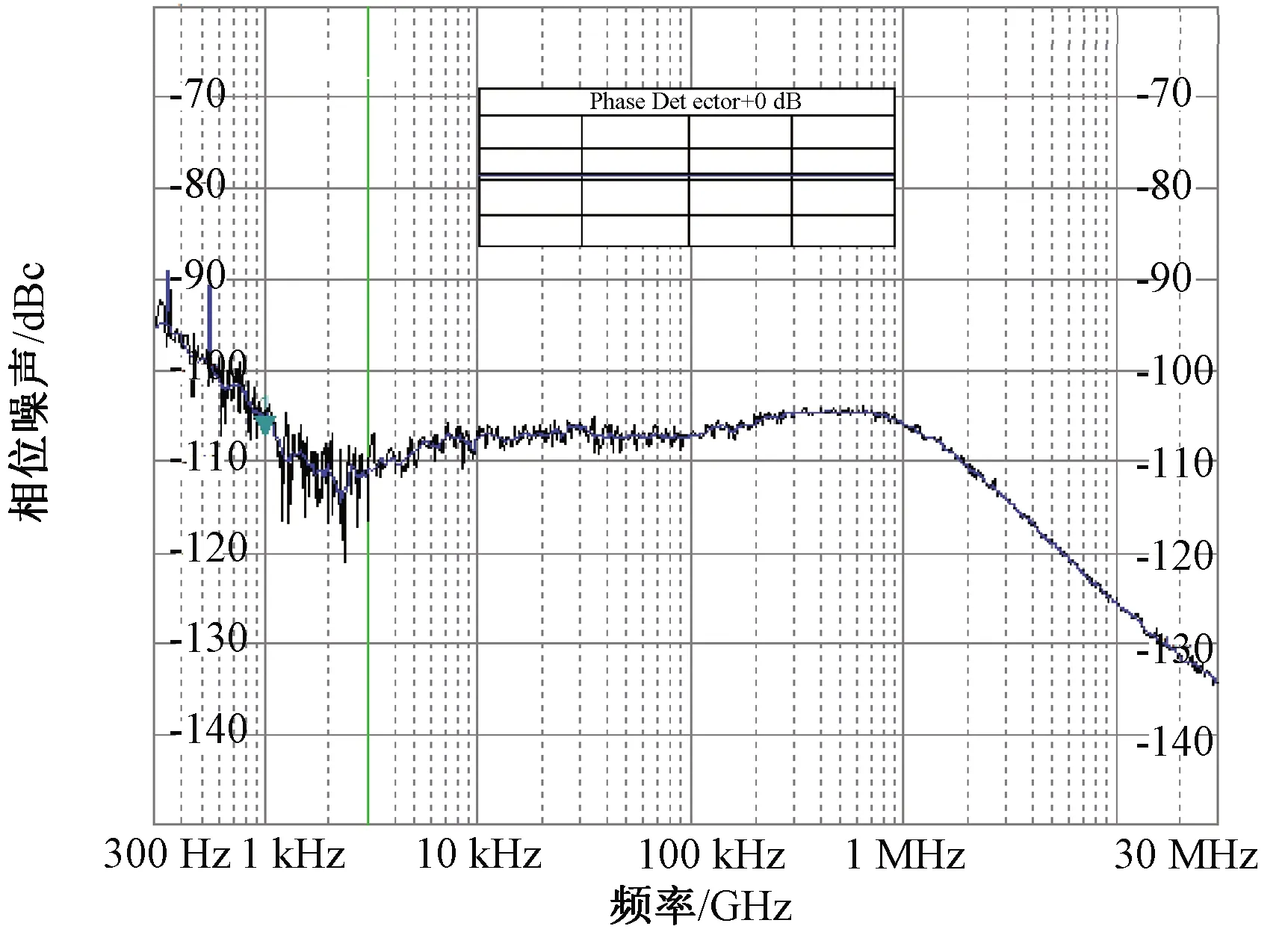

图14所示为20 GHz载波处相位噪声,其输出曲线与仿真接近,约-104 dBc/Hz@1 kHz。

图14 相位噪声实测结果

图15所示为频率切换时间测试图,从逻辑电平同步信号上升沿50%到输出检波信号上升沿50%处的时延约150 ns,扣除检波时间延时后,满足指标要求。

图15 频率切换时间实测结果

4 结束语

本文提出了一种K波段超低杂散捷变频频合器的设计方案,该方案通过2次上变频,将DDS输出的低杂散中频信号上变频至K波段,同时总带宽扩展为4 GHz。在组件设计过程中,利用ADIsimPLL软件仿真了本振电路的杂散与相噪,并使用ADS软件仿真了整级射频链路的功率、杂散、相位噪声情况。实测结果与仿真结果相近,满足对应设备的使用要求。

与其他同类宽带捷变频频合器相比,本文在杂散控制方面具有优势,达到-75 dBc,带宽为4 GHz,频率切换时间小于150 ns。此类基于DDS+DAS技术的频合器,既能作为宽带快速本振应用于无线系统中,也能实现各种数字化的调制方式,其在雷达、对抗、通信等领域得到了广泛应用。