基于FPGA 的无人机遥控及图传信号采集系统设计

2020-08-25谢跃雷

蒋 平, 谢跃雷

(桂林电子科技大学认知无线电与信息处理省部共建教育部重点实验室,广西桂林541004)

0 引 言

随着无人机技术的高速发展,民用无人机得到了普及,给人们生活带来了便捷,但同时因为无人机未经许可随意飞行的“黑飞”事件屡屡发生,对民航机场、敏感目标以及涉密区域的安全保障带来了严重隐患[1]。针对这种“黑飞”现象,必须要进行管控[2-3],对于管控首先要对无人机进行有效的探测。探测主要分为无源探测及有源探测,有源探测主要是通过雷达探测方式,对于低、慢、小型无人机往往达不到探测目的[4]。相比之下,无源探测方式更适用于探测低、慢、小型无人机。

无源探测方式主要分为光学探测、声学探测和无线电频谱监测,其中光学探测受天气影响较大,声学探测探测距离近,而无线电频谱监测方式距离远,且有利于目标定位,通过无线电频谱监测实现无源探测更加有效[5]。

本文基于无线电频谱监测方式,设计了一套以FPGA为硬件平台的无人机遥控及图传信号的采集、存储、传输系统[6-7],该系统解决了因AD9361带宽范围最大为56 MHz而无法对存在于2.3 ~2.5 GHz、5.7~5.9 GHz双频段无人机遥控及图传信号的采集问题以及MIG IP无法多通道防冲突异步传输的缺陷[8],此外该系统通过FPGA采用UDP协议对千兆网芯片进行驱动,解决了采集数据的高速传输问题。能够有效地完成对低、慢、小民用无人机遥控及图传信号的采集、存储、传输。

1 系统总体设计

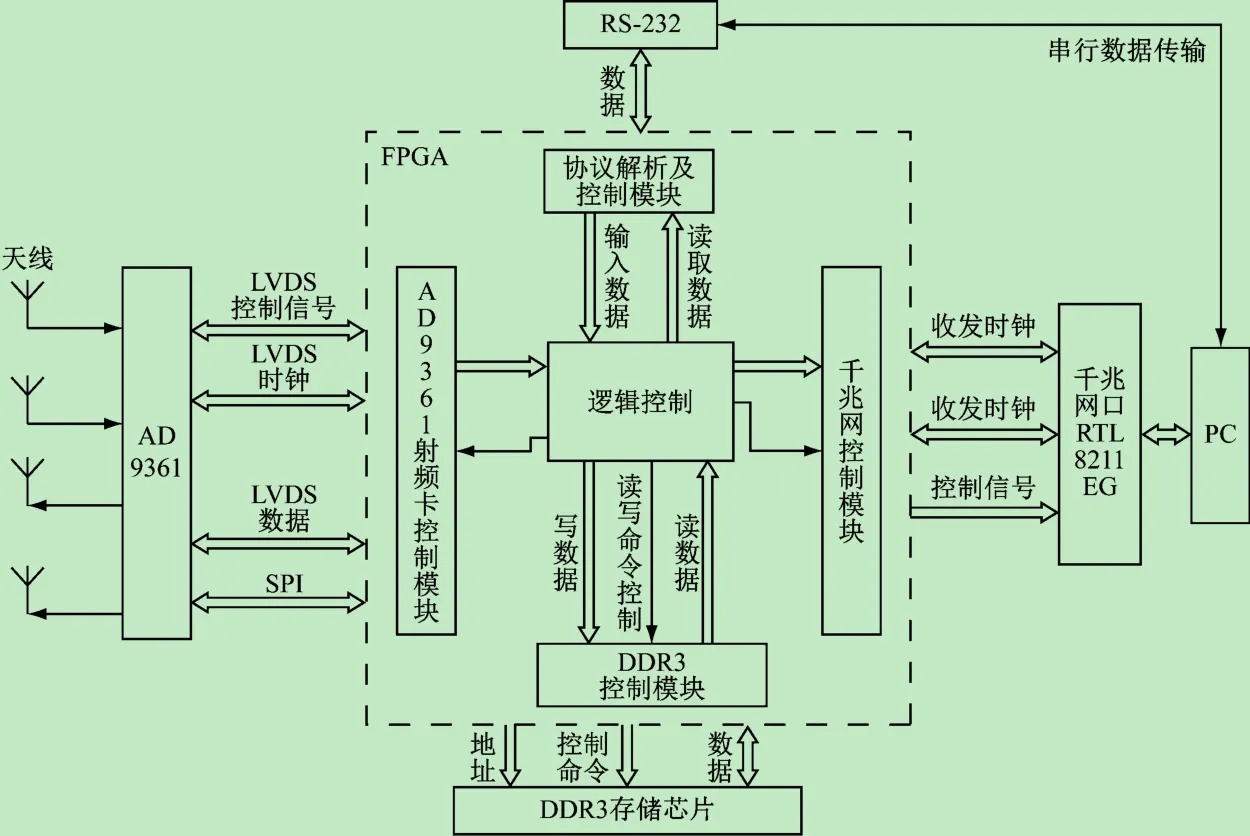

本设计主要由FPGA主控模块、AD9361射频板卡、协议解析、DDR3和千兆网等控制模块组成[9]。

基于FPGA的无人机遥控及图传信号的采集、存储、传输系统的总体设计框图如图1所示。FPGA主控模块实现对整个系统各个模块的控制及采集数据的高速处理;AD9361射频板卡控制模块对存在于2.3~2.5 GHz、5.7 ~5.9 GHz的无人机遥控及图传信号进行双通道宽带扫频采集,并对采集信号进行低噪声放大、混频、模数转换、滤波以及下变频,实现零中频接收机架构;协议解析及控制模块通过对用户自定义通信协议的解析完成上位机对下位机的软件控制以及对整个无人机遥控及图传信号的采集、存储、传输系统的运行状态进行查询;DDR3模块控制DDR3存储芯片实现对AD9361射频采集板卡采集数据进行缓存并且实现了采集数据的多通道异步防冲突读写功能;千兆网控制模块对数据进行跨时钟处理并对传输数据进行打包,通过采用UDP协议方式进行数据的高速传输[10]。

图1 系统总体设计框图

2 模块设计及FPGA实现

2.1 FPGA主控模块

本系统FPGA采用XC7K325T芯片,芯片具有326 080个逻辑单元、50 950个查找表,满足系统硬件设计要求。整个系统通过Vivado 2018.1软件进行系统级开发并由逻辑分析仪进行功能验证。

FPGA硬件程序采用自顶向下的设计架构,对系统中的各个模块进行实时控制以及高速并行处理[11]。如图2所示为系统的逻辑资源消耗图,LUT消耗14%,FF消耗9%。DSP消耗2%,由此可知该FPGA芯片完全满足设计要求,且剩有大量逻辑单元以及DSP,益于后期无人机检测与识别算法在FPGA平台上的研究及验证。

图2 系统逻辑资源消耗图

2.2 AD9361射频板卡控制模块

系统采集部分采用AD9361作为射频采集芯片,该系统通过FPGA对AD9361进行寄存器配置,完成信号的低噪声放大、混频、滤波、下变频操作,实现整个零中频接收机架构[12]。

AD9361模块分别对AD9361进行寄存器配置以及对无人遥控及图传信号的采集。其中由于AD9361采集带宽范围最大为56 MHz,而常用的无人机遥控及图传信号存在于2.3 ~2.5 GHz、5.7 ~5.9 GHz频段范围内,故本设计为了解决该问题采用内部ROM模块循环加载的方式实现了快速扫频采集操作。

如图3所示,系统上电,初始化寄存器轮询输出,通过SPI时序完成寄存器配置,完成AD9361基本功能的初始化。协议解析通过协议解析模块传来的上位机命令进行采集,扫频范围则通过该命令进行选择,命令一共分为3 种,一种是2.3 ~2.5 GHz、5.7 ~5.9 GHz双频段扫频,另一种是2.3~2.5 GHz频段扫频,最后一种是5.7~5.9 GHz频段扫频。当选择好扫频范围过后,便对预先存有频率寄存器的ROM模块进行轮询输出,通过SPI完成寄存器配置,待配置完成,返回协议解析状态并等待命令。

数据采集部分按照AD9361时序通过LVDS转单端的方式完成数据的采集处理,数据分为双通道,每一通道分为IQ两路。其中A/DC采样率为640 MHz、差分时钟DATA_CLK_P与DATA_CLK_N 为160 MHz。

2.3 DDR3 控制模块

图3 AD9361寄存器操作流程图

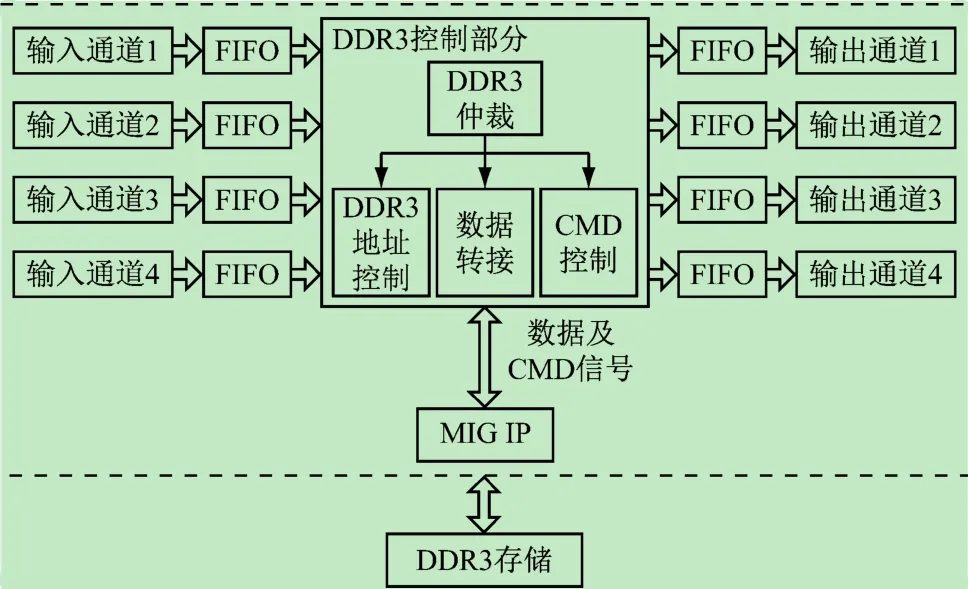

图4 DDR3控制模块框图

DDR3控制模块主要是实现大规模数据的缓存,因MIG IP只能满足物理层的数据传输,不适用于本设计的多通道数据缓存及异步读写。基于现有的不足,设计了该模块。模块框图如图4所示,数据共有4通道输入,通过FIFO进行数据跨时钟处理,FIFO数目根据输入通道数进行分配[13]。DDR3控制部分分为仲裁、地址控制、数据转接、CMD控制,DDR3地址控制可对每一通道所使用的DDR3内存容量进行选择性分配,数据转接则是完成输入、输出数据与MIG IP的内部传输[14],CMD控制部分负责MIG IP的读写控制,DDR3仲裁则对整个控制部分进行管控。输出数据分为4通道并实现跨时钟处理。

整个DDR3控制模块实现了数据并行实时输入、输出,且各个通道皆具有跨时钟处理功能,满足了多通道异步防冲突实时读写要求。

2.4 千兆网控制模块

千兆网模块采用UDP协议实现数据的高速传输,该模块主要由发送端、接收端、CRC校验、数据组包以及发送及接收状态机构成[16-17]。千兆网控制模块图如图5所示。

图5 千兆网控制模块图

数据组包模块负责对输入数据进行逐个打包,每包有效数据长度为1 280 Byte。千兆网控制部分负责对输入、输出数据进行传输、接收和发送状态机的控制,其中控制信号由DDR3内存空、满状态确定。发送状态机按照UDP协议方式通过接收组包数据及CRC校验数据进行轮询输出。接收状态机按照UDP协议逐个解析数据并存储。

3 系统测试及分析

3.1 采集模块测试与分析

本系统选用4Pro无人机进行测试,通过使用Vivado在线逻辑分析仪对系统采集模块数据进行Debug[17],并用Matlab 软件进行频谱分析。

如图6所示为实测数据频谱图,其中左侧圈内为无人机跳频信号,每一跳频信号带宽大约1 MHz。右侧箭头为图传信号,频率为2 441~2 451 MHz,带宽为无人机所设置的图传带宽10 MHz。

图6 实测数据频谱图

通过FPGA内部控制,AD9361扫频采集中每一个频点周期设置大约为0.55 ms,对于整个带宽范围为400 MHz的无线信号需要10个频点,周期大约为5.5 ms。逻辑分析仪不便于直观的对接收端进行观测,利用AD9361发射与接收皆是通过相同方式实现扫频,即扫频发射与扫频接受,故通过对AD9361发射端进行扫频测试,亦可证明AD9361芯片本振频率处于跳变状态。通过范围为2.3~2.9 GHz手持式频谱仪对AD9361发射频率进行测试。发射端通过对AD9361寄存器设置5个频点并且发射信号为单音信号,接收扫频同样设置为5个频点,且以每一个频点为中心频点,即为零频点,范围为上下带宽20 MHz。

如图7所示,频谱热力图中共有5个最高频点,且5个频点通过扫频方式不断变化。因此可证,接收端同样以5个中心频点不断刷新,扫描带宽为200 MHz,同理,上位机设置2.3 ~2.5 GHz、5.7 ~5.9 GHz,即可得出总扫频范围为400 MHz,因此证明该系统具有宽带扫频功能。

图7 扫频频谱热力图

通过以上测试可知,本系统具有快速扫频采集功能,扫频总带宽为400 MHz,周期为5.5 ms。满足无人机慢速跳频遥控信号以及定频图传信号采集要求。

如图8所示为系统采集实物图。

图8 系统采集实物图

3.2 存储模块测试与分析

通过使用Vivado在线逻辑分析仪对系统存储模块进行验证。

图9(a)为DDR3控制模块多通道输入波形图,该模块共4通道输入,其中当每一个通道输入有效信号置高,数据便输入,如图中ad_0_vld为第1路输入信号,ad_0_data_in为第1 路输入数据,其他3 路依次类推。DDR3控制模块多通道输出波形如图9(b)所示,该模块共4通道输出,其中当每一个通道输出有效信号置高,数据便输出,如图中rd_0_en代表第1路输出信号,ad_0_data_ou代表第1路输出数据,其他3路同理。

图9 DDR3控制模块波形图

3.3 传输模块测试与分析

通过使用Vivado的逻辑分析仪对千兆网发送端内部状态机及控制信号进行分析。通过Wireshark软件对千兆网传输模块进行抓包分析,并测试千兆网传输速度。

如图10所示为系统千兆以太网口控制部分波形图,图10(a)为接收数据波形图,其中信号tx_state为状态机状态信号,tx_vld为组包信号共20个,每一个包含64 Byte数据,共1 280 Byte。图10(b)、(c)为接收数据波形放大图并附有相应解释与说明。

如图11所示为通过Wireshark软件对系统千兆网部分进行的抓包测试图,其中抓取10 000个包耗时0.107 155 s,每包有效数据1 280 Byte,根据计算,可得本系统千兆网传输速度大约为911 Mb/s。

图10 千兆网口控制部分波形图

4 结 语

随着民用无人机的普及,民用无人机“黑飞”现象也常有发生,对于无人机的检测、识别、反制等需求日益上升。本文基于无人机无源探测方式,设计了一套无人机图传及遥控信的采集、存储、传输系统。

该系统具有3大功能,分别为采集、存储、传输功能。采集功能针对AD9361带宽范围对设计需求的不足,而采用FPGA对AD9361进行控制实现快速扫频采集功能,可满足对2.3 ~2.5 GHz、5.7 ~5.9 GHz的无线电信号采集。存储功能基于MIG IP无法满足设计需求,而设计的基于DDR3多通道异步防冲突读写存储模块,该存储模块完成了系统对多通道数据同时传输、存储的需求。传输功能因系统对传输速度的需求,故采用UDP协议实现千兆网传输,通过测试验证可知,速度可达911 Mb/s。通过实际测试,可以证明该系统可实现对无人机遥控及图传信号的快速扫频采集、对DDR3存储器的多通道防冲突异步读写、对采集数据的千兆网高速传输,为下一步无人机检测与识别算法研究提供了高效稳定的硬件系统[18]。