高效率PLB2AXI总线桥的设计与验证

2020-08-19魏敬和

张 浩,魏敬和,2

(1.江南大学 物联网工程学院,江苏 无锡 214122; 2.中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 概述

片上系统(System on Chip,SoC)主要采用第三方的IP核进行设计,其将不同功能的IP核集成到一个芯片上,以此来实现系统级的功能。因此,实现系统中不同IP核之间的高效通信成为集成过程中的关键问题[1]。在SoC中,不同模块通过总线进行通信,对此,各种总线协议相继被提出,如AMBA协议[2]、Core Connect协议等[3]。然而,每一种总线协议都有其优势和不足,为提高系统的整体性能,研究者往往会权衡不同协议的优缺点并加以结合,设计高能效的多总线系统。多总线系统中的协议转换是通过总线桥来实现的,一方面将两种总线的不同接口信号进行转换,另一方面对两种总线信号的时序进行调整[4]。

面向总线桥性能要求较高的应用场景,本文设计一种从PLB总线到AXI总线的桥,用以高效完成两种总线之间的协议转换和信息传递。该设计支持流水传输、读写重叠传输以及高带宽的数据传输,能够实现两种协议的精确转换,并且满足SoC系统对于带宽和传输速率的要求。

1 PLB与AXI总线

1.1 PLB总线

PLB总线的读写数据通道相互独立,支持读写重叠传输和突发传输。一个完整的PLB总线传输包括地址周期和数据周期2个部分[5]。其中,地址周期分为请求、传输和地址应答3个阶段,数据周期分为传输和数据应答2个阶段[6]。

分立的PLB地址数据总线不但允许地址周期与数据周期重叠,而且还允许写数据周期与读数据周期重叠[7]。同时,PLB协议允许地址和数据总线拥有不同的主设备,这使得系统的灵活性得到显著增强,极大地提高了数据吞吐能力。

1.2 AXI总线

与PLB总线相比,AXI总线具有以下3个特点:

1)AXI总线分为5个独立的信息通道,即读地址通道、写地址通道、读数据通道、写数据通道和写响应通道。这样的总线结构有2个优点:(1)设立独立的数据和地址通道便于对每一个通道进行单独优化;(2)独立的读写数据通道使AXI总线上的读数据和写数据可以在同一时间进行传输,带宽得到显著提高[8]。

2)AXI总线每个通道中的信息流都以单方向进行传输,彼此的信息传输互不干扰[9]。

3)AXI总线上的主设备与从设备在进行通信时采用的是Valid/Ready握手机制。主设备通过Valid信号来指示通道中的信息何时有效,从设备通过Ready信号来指示是否已准备好接收这些信息。只有当Valid信号和Ready信号同时有效,主从设备握手成功,通道中的信息才能正确传输[10]。

2 PLB2AXI总线桥设计

2.1 PLB/AXI总线系统

本文设计的PLB2AXI总线桥是单向的,只允许PLB总线上的主设备对AXI设备进行读写,而AXI设备无法发起针对PLB总线的传输。PLB2AXI桥在PLB/AXI系统中的位置如图1所示。

图1 PLB/AXI系统架构Fig.1 PLB/AXI system architecture

因为总线桥同时挂接在两条总线上, 所以拥有PLB与AXI 2种接口。在设计桥的过程中,本文将其分为读模块和写模块2个部分来分别实现,然后根据读写选择信号PLB_RNW对2个模块进行片选。

2.2 写模块实现

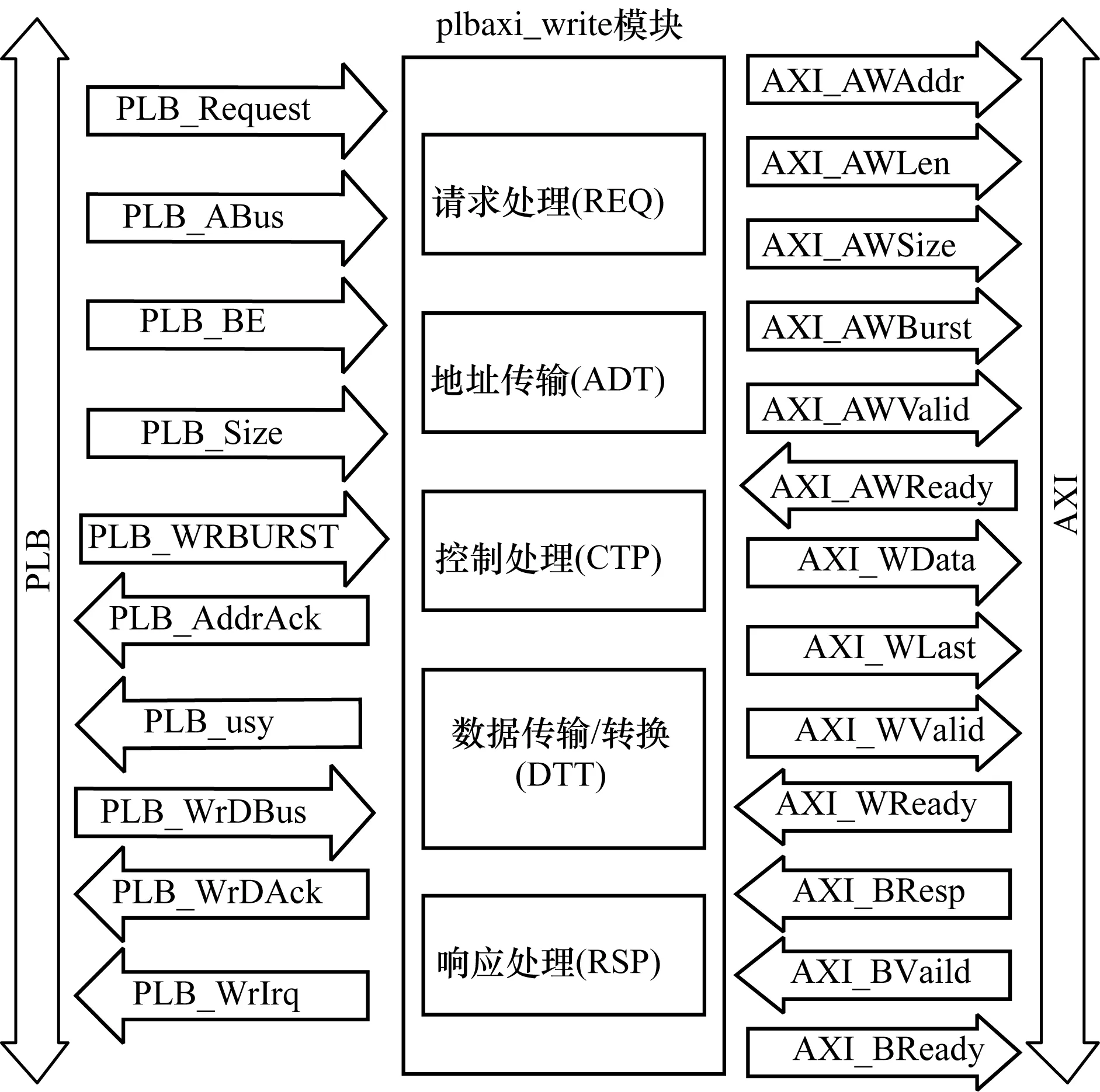

PLB2AXI总线桥中写模块由请求处理(REQ)、地址传输(ADT)、控制处理(CTP)、数据传输/转换(DTT)、响应处理(RSP)5个功能模块组成,如图2所示。

图2 写模块架构与信号接口Fig.2 Write module architecture and signal interface

2.2.1 请求处理模块

在传输地址时,请求处理模块首先要完成AXI地址传输通道的握手。PLB总线上的主设备在发起跨总线传输时会发出PLB_Request信号,请求占用总线资源进行地址和控制信号的传输。如果此时总线空闲且地址传输模块流量允许,则当前传输的写地址有效,AXI_AWValid信号被断言;如果AXI上的从设备就绪,则AXI_AWReady信号即被断言。此时地址通道Valid/Ready握手成功。

2.2.2 地址传输模块

地址传输模块是控制流水线传输的重要部分,该模块中设有地址信息存储单元。在请求处理模块完成握手后,开始传输第1个地址[11]。当该地址传输完毕,地址应答信号PLB_AddrAck有效,这标志着从设备已经成功接收地址,地址传输周期结束,数据传输周期开始。此时,无需等待上一个数据传输周期结束,主设备就可以发起下一次传输请求,并将相关地址数据写入地址信息存储单元直至存储单元满[12]。待总线允许发送下一个地址数据时,再将存储单元中的地址信息转换并发送到AXI总线上,通过此方式实现流水线传输。

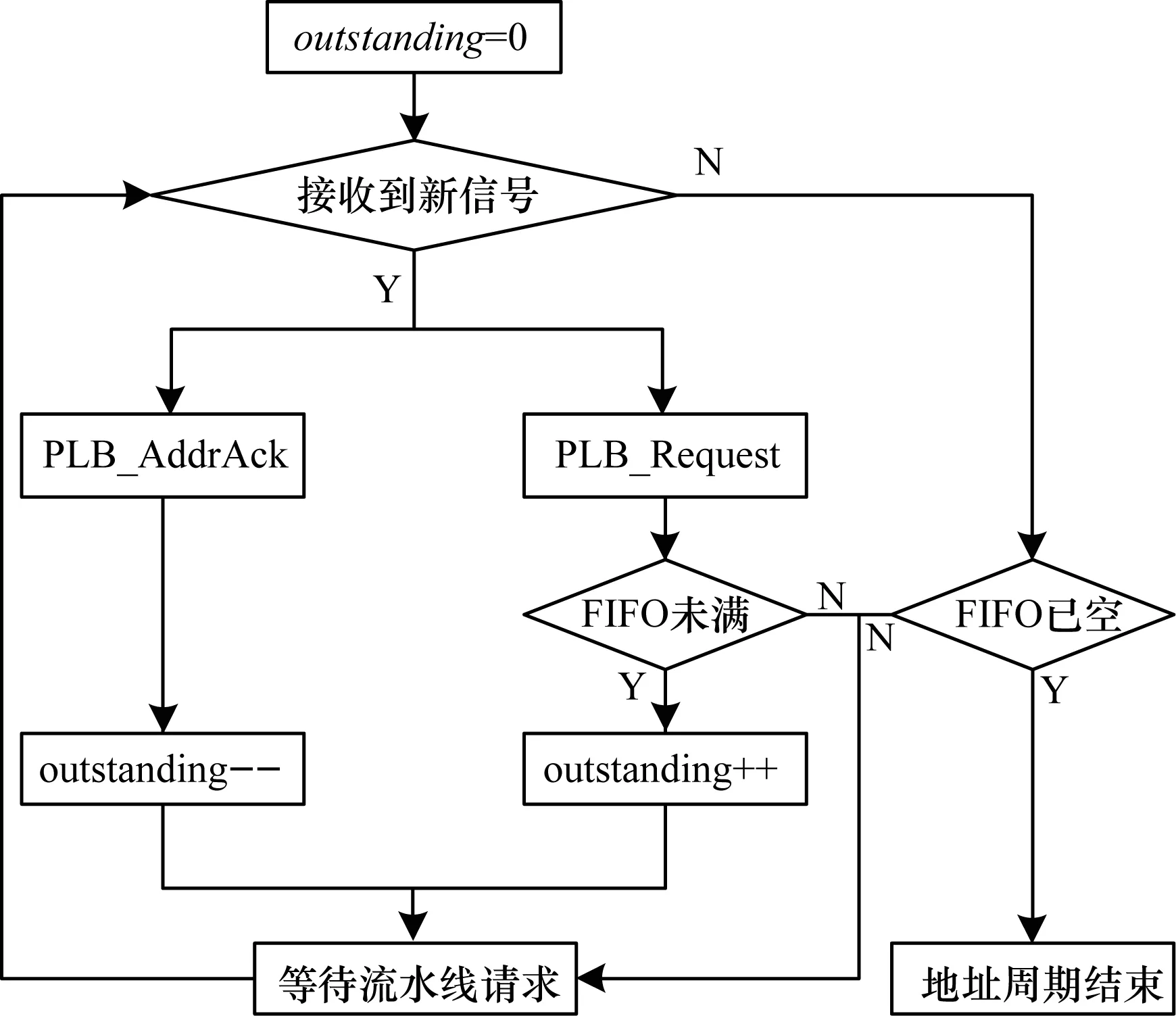

如图3所示,PLB_AddrAck信号对于地址传输模块的流水线控制具有十分重要的意义。在该模块中设置一个初值为0的寄存器变量outstanding,以此来表示存储单元中待传地址的数目。若PLB_Request有效,则意味着一个新的传输被发起,待传输的地址数outstanding加1;若PLB_AddrAck信号被断言,则意味着地址已被从设备成功接收,outstanding的值减1。只要待传地址数目小于存储单元容量,主设备就可以发起新的传输请求。

图3 流水线控制机制工作流程Fig.3 Work flow of pipeline control mechanism

2.2.3 控制处理模块

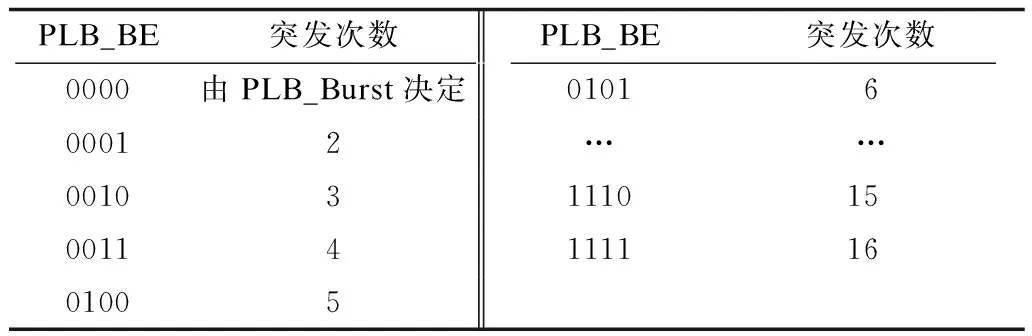

控制处理模块的主要功能是对与Burst传输有关的控制信号进行转换。如果PLB_Wburst有效,则当前传输为Burst传输。在本文设计中,控制处理模块的AXI_Wburst信号恒为2’b10,因此,突发类型被设置为地址递增的Burst传输。与突发长度(即突发次数)和突发尺寸有关的控制信号PLB_BE与PLB_Size被转换为AXI_ALen与AXI_Size,具体编码方式如表1和表2所示[13]。

表1 PLB_BE编码Table 1 Coding of PLB_BE

表2 PLB_Size编码Table 2 Coding of PLB_Size

2.2.4 数据传输/转换模块

本文设计中的数据传输/转换模块需要完成3个基本任务:1)实现数据传输通道的Valid/Ready握手;2)完成数据的大小端转换(PLB总线上的数据按照大端模式进行传输,在传到AXI总线时数据要由数据传输/转换模块转换成小端模式);3)根据控制信号进行数据传输。

数据传输方式分为突发传输和非突发传输,这些控制信息都由控制处理模块指定。当接到响应处理模块发出的PLB_WrDAck信号时,说明该数据已被AXI从设备成功接收。

2.2.5 响应处理模块

在AXI从设备成功接收地址和数据后,传输进入应答反馈阶段。响应处理模块首先完成响应通道的握手,然后对AXI从设备发来的应答信号AXI_BResp进行处理,最后将其转换为PLB应答信号反馈给主设备。

1)处理应答信号AXI_BResp:如果应答信号AXI_BResp为“OKAY”(2’b00),说明从设备成功接收地址和数据,响应处理模块分别将PLB_AddrAck和PLB_WrDAck断言并发送给主设备,以此作为本次传输的应答;如果应答信号AXI_BResp为不是“OKAY”,说明地址或数据传送出现错误,响应处理模块将PLB_WrIrq信号拉高作为本次传输的应答。

2)如果总线正在进行传输,响应处理模块会将PLB_Busy发送给主设备,这意味着数据通道正在被占用。

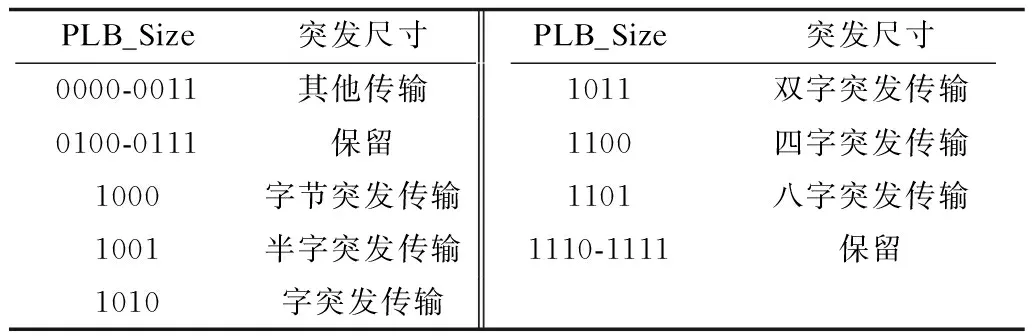

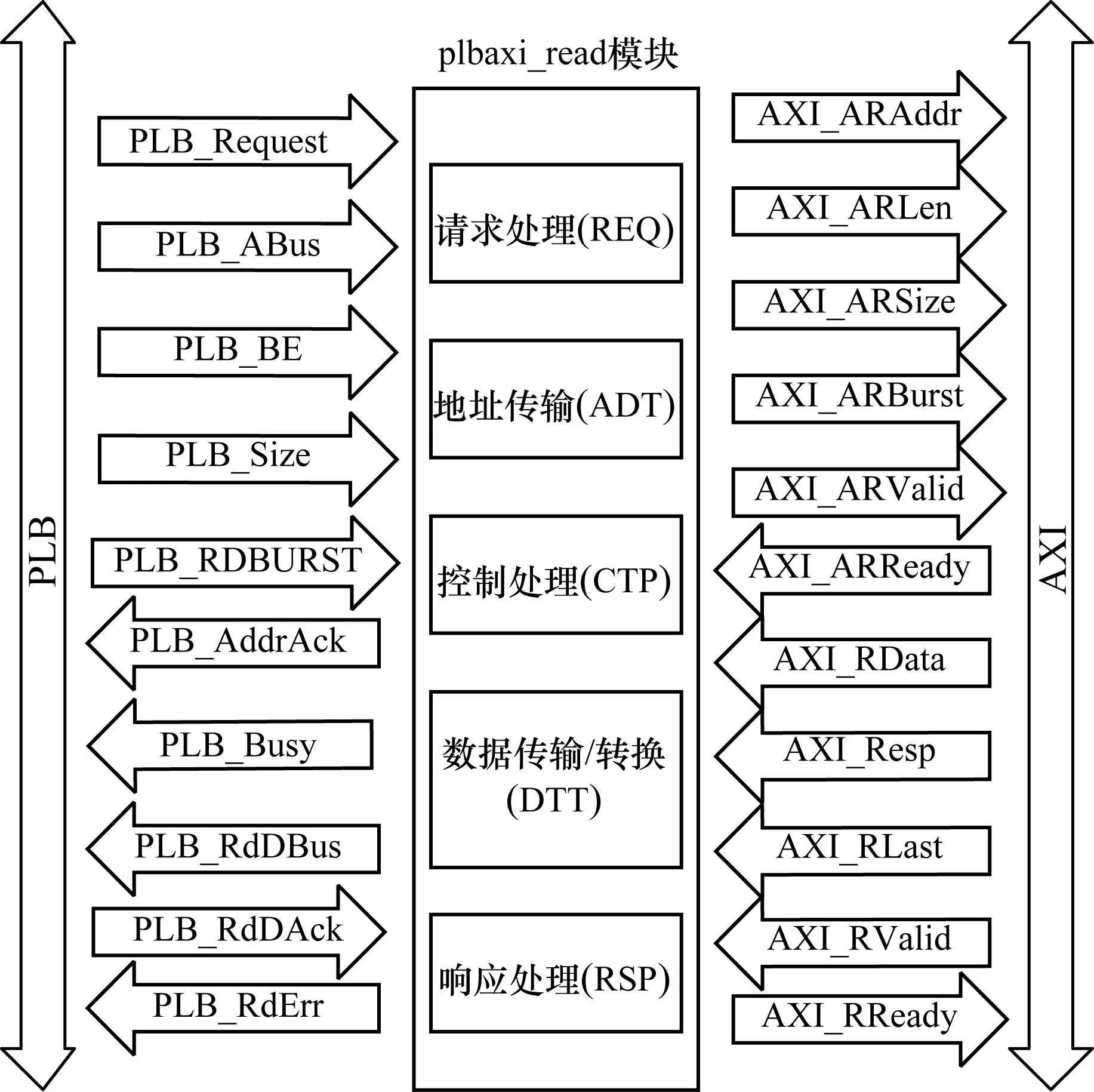

2.3 读模块实现

如图4所示,本文中读模块与写模块的架构基本相同。

图4 读模块架构与信号接口Fig.4 Read module architecture and signal interface

两者的主要区别为:

1)数据传输方向不同。写模块中的数据是从PLB发往AXI总线的,而读模块中的数据传输方向是从AXI到PLB总线的。因此,读模块中的数据传输/转换模块需要对数据传输方向进行相应调整,而且数据应从AXI总线的小端模式转换为PLB总线的大端模式。

2)读模块没有响应通道。读模块中的响应信息是伴随着数据一起从AXI发往PLB总线的,无需设立专用的“读响应通道”。因此,在读模块中无需进行AXI_BValid与AXI_BReady的握手,而是直接由AXI总线将反馈信息AXI_Resp发送给读响应处理模块进行处理。

2.4 高效率策略分析

本文设计充分利用了高性能总线PLB和AXI的性能优势,通过采用流水线传输和实施PLB与AXI协议所支持的读写重叠传输来提高总线桥的转换和传输效率。

传统总线桥的数据通道和地址通道之间存在相互等待反馈的问题。在图5(a)所示的传统总线桥设计中,必须等待上一次的地址和数据传输完成后,下一个地址数据才能开始传输,这无形中增加了各环节的等待时间,降低了系统的效率[14]。在图5(b)所示的流水线总线桥设计中,主设备可以连续向从设备发送多个访问请求,在进行一个访问的同时也可以发布新的访问请求,直至暂存地址数据FIFO满[15]。本文设计的总线桥不仅支持流水线传输,还充分利用了PLB与AXI总线读写数据通道分离的结构优势,加入了读写重叠传输机制。在图5(c)所示的设计中,主设备向从设备连续发起多次读写操作请求,各个读写地址依次进行传输,在进入数据周期后,读写数据分别利用各自的读写数据通道进行传送[16],读数据传输和写数据传输可以并发执行而无需相互等待,此读写重叠机制可在流水线传输的基础上进一步缩短传输时间,大幅提高带宽利用率和系统传输效率。

图5 总线桥高性能策略Fig.5 Bus bridge transmission performance strategy

3 PLB2AXI总线桥验证

3.1 总线桥的功能仿真

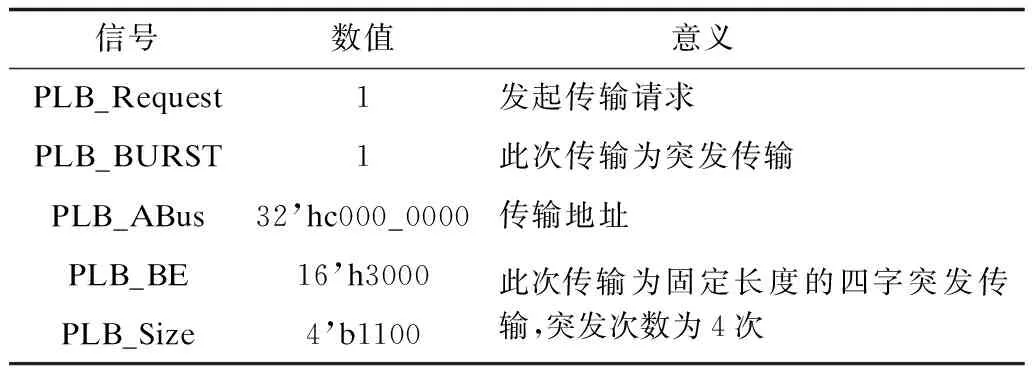

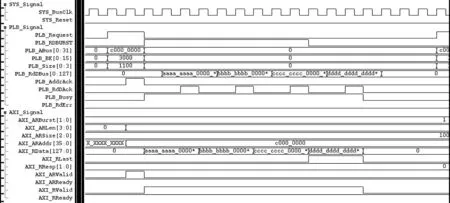

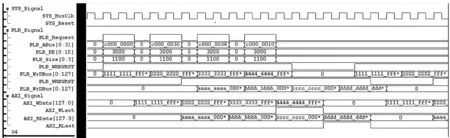

本文使用Synopsys公司的VCS工具对PLB2AXI桥进行功能仿真,然后通过Verdi工具对得到的波形进行处理和查看。写突发传输、读突发传输以及流水线与重叠传输波形分别如图6~图8所示。地址周期开始后,总线桥开始进行表3所示地址与传输控制信号的传输。

表3 地址与传输控制信号Table 3 Address and transmission control signals

在AXI端成功接收相关信号后,地址应答信号PLB_AddrAck被拉高,地址周期结束,数据周期开始,数据在经过大小端转换后,通过128位数据总线PLB_WrDBus/AXI_WData开始依次传输[17]。每成功接收到一个数据,PLB_WrDAck信号都被拉高一次。在写突发传输中,完成数据接收的从设备会在写响应通道握手后发送反馈信号“OKEY”[18];而在读突发传输中,数据应答伴随读数据一同发往PLB主设备。在图6与图7中,完成写突发共用16个时钟周期,完成读突发共用18个时钟周期。

图7 读突发传输波形Fig.7 Read burst transmission waveform

图6 写突发传输波形Fig.6 Write burst transmission waveform

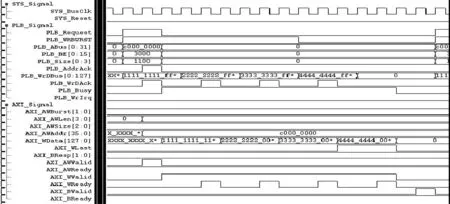

在图8中,总线桥通过流水线和读写重叠的方式进行传输,PLB端总共发起4次读写请求,分别是“写”-“读”-“写”-“读”请求。PLB_BURST信号为“1”说明本次传输为突发传输。4次读写操作的地址分别为32’hc000_0000、32’hc000_0030、32’hc000_0038和32’hc000_0010,并且PLB_BE和PLB_Size为16’h3000和4’b1100,说明此次传输为固定长度的四字突发传输,突发次数为4次。在上一次地址传输完毕之后,无需等待数据周期结束即可进行下一个地址的传输,每次地址传输间隔一个时钟周期。在每个地址传输完成后,读写数据分别通过读写传输通道并发传输,读写数据周期相互重叠,大幅缩短了数据的传输时间[7]。第1次读写数据传输完成后4个时钟周期,第2次读写数据的传输并发进行,读写数据周期仍然重叠,完成4次读写操作共需要37个时钟周期。

图8 流水线与重叠传输波形Fig.8 Pipeline and overlap transmission waveforms

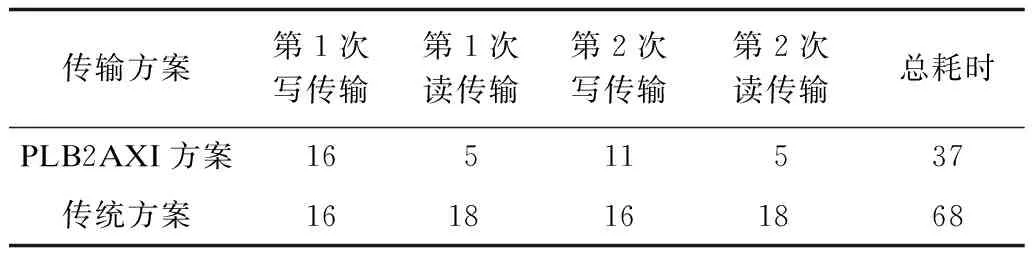

本文设计的PLB2AXI总线桥与传统不进行流水线传输和重叠传输的总线桥的对比如表4所示。可以看出,引入流水线传输和重叠传输的PLB2AXI方案总耗时仅为传统方案的54.41%,验证了PLB2AXI总线桥的优越性。

表4 不同传输方案的耗时对比Table 4 Time consuming comparison of different transmission schemes ms

3.2 总线桥的FPGA验证

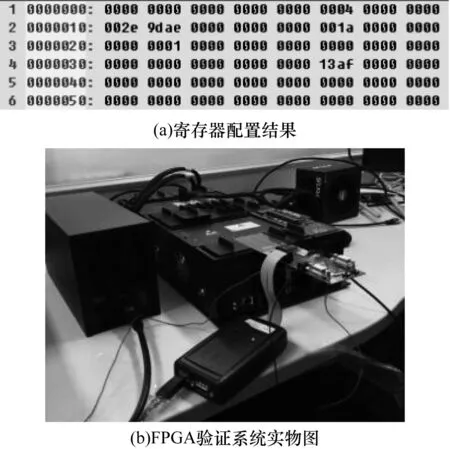

为验证SoC的功能,进而测试总线桥在系统中是否正常工作,搭建由HAPS及相关外设子板构成的FPGA系统验证平台,如图9所示。

图9 FPGA系统验证环境Fig.9 FPGA system verification environment

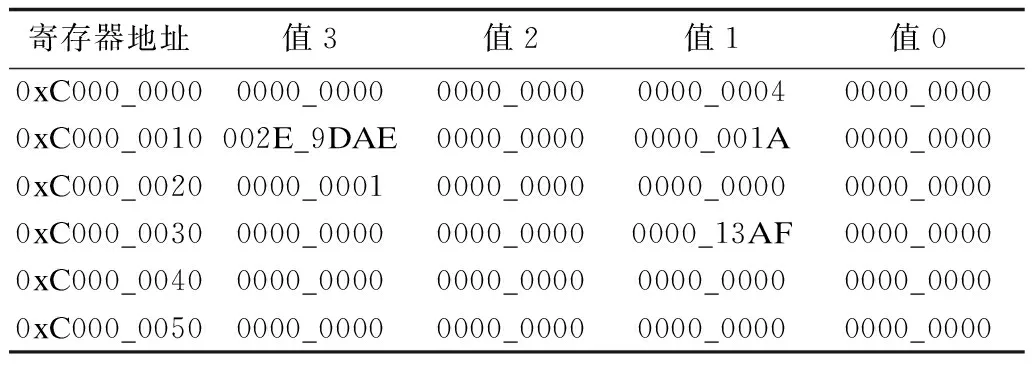

HAPS Prototyping Solution是Synopsys基于FPGA的原型验证解决方案[19],其是一个完整的FPGA系统验证环境。该平台不仅提供高性能的FPGA平台硬件,而且提供与之紧密配套的自动化调试环境HAPS Proto Compiler[20]。在本文设计中,PLB总线上的PowerPC内核通过PLB2AXI总线桥进行协议转换,然后对用户IP Main controller的寄存器进行如表5所示的配置。

表5 对用户IP寄存器的配置值Table 5 Configuration value of user’s IP register

执行配置程序后,PowerPC成功完成了对Main controller中各寄存器的的配置,配置后的寄存器结果如图10所示。测试结果不仅验证了PLB2AXI总线桥协议转换功能的正确性,还验证了SoC系统的跨总线配置功能的正确性。

图10 寄存器配置结果与FPGA验证实物图Fig.10 Register configuration result and physical diagram of FPGA verification

4 结束语

本文通过引入流水线传输和读写重叠机制,设计PLB2AXI高性能总线桥,以实现SoC中各模块协议的精确转换,提升传输效率。实验结果表明,对于同样的传输任务,PLB2AXI用时仅为传统总线桥的54.41%,时间开销大幅降低。此外,系统级的FPGA验证也进一步证明了该设计的正确性。后续将优化本文PLB2AXI总线桥的传输性能,并将其应用于多总线SoC系统的设计中,以此提升系统的整体工作效率。