集成运放电路功能模拟实验教学装置设计*

2020-08-11汪兴海孙雪丽毕敬腾

汪兴海 孙雪丽 毕敬腾

(海军航空大学航空基础学院 烟台 264001)

1 引言

近些年,随着高速AD/DA硬件技术的不断发展,以软件无线电为代表的电子系统设计理念不断深入人心,军用电子设备不断更新换代,对军队院校人才培养提出了新的要求。目前军队院校电子信息类专业相关公共课程主要包括模电、数电、可编程逻辑设计、数字信号处理等,电子技术实践教学作为电子学相关专业本科教学的重要组成部分,目前主要采用项目驱动、比赛牵引、自主实践等形式进行,学生能够在实践过程对课本知识进行综合运用,并能够根据实践目标进行拓展学习,取得了较好效果[1]。

为了进一步提升学生对数字电子技术的认知水平,强化电子技术实践教学环节项目设计的综合性,将电子技术相关知识点有效串联,本实验教学装置将集成运放电路、AD/DA电路、可编程逻辑设计、片上系统设计、嵌入式系统编程等知识点综合为实践教学项目,培养学生电子系统综合应用能力,也为后续数字信号处理相关课程的学习做好铺垫。

2 设计要求与模块组成

运放电路能完成加减、积分、微分以及比例运算等。综合考虑实践教学目标、实验室元器件性能指标、经费保障等因素,将基本要求制定如下[2~4]。

1)模拟信号输入:幅度范围1Vpp;频率范围10k~100k;波形类型为正弦波、方波、锯齿波;通道数2。

2)模拟信号输出:幅度范围10Vpp;通道数1。

3)实时采样率≥10K。

4)可手动设置功能模拟选项,包括加法、减法、积分、微分。

5)显示:能够显示当前电路功能相关信息。

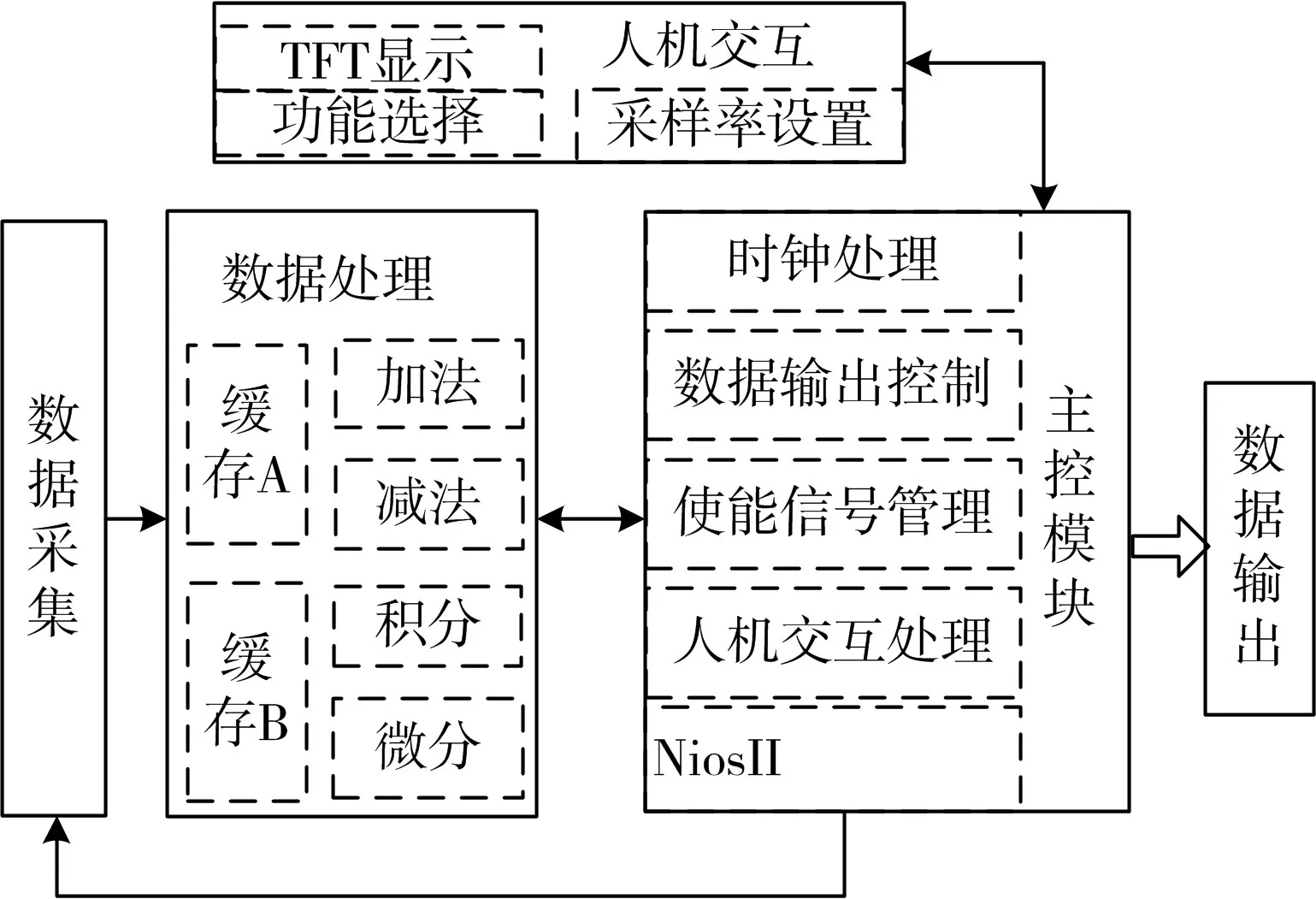

模块组成主要包括:数据采集、数据处理、数据输出、主控、人机交互,如图1所示。

图1 模块组成图

数据采集:根据主控模块提供的采样率,将输入模拟信号转换为数字量。

数据输出:根据主控模块提供的采样率,将数据处理模块生成的数字量转换为模拟量。

数据处理:根据主控模块提供的采样率,读取数据采集模块上传的数据,根据主控模块提供的功能设置信息对数据进行运算处理,并将运算结果传递给数据主控模块。

主控模块:作为片上系统的控制中枢完成各个功能模块的信息解析与传递,负责整个片上逻辑的驱动管理[5~6]。

人机交互模块:实现功能信息的显示和操作指令的输入,例如功能设置输入、采样率设置、功能电路显示。

3 系统硬件方案设计

3.1 数据处理

数据采集电路采用8bit并行输出,每完成一次采样,该模块需要读入2*8bit数据,对数据进行4个采样周期的延时处理后,需要对数据进行处理,完成加/减、微/积分、比例运算等操作,硬件平台基于Altera Cycloneiv系列芯片设计,缓存模块采用芯片内置的DCFIFO和双口RAM设计,该模块的核心部分是算法逻辑电路设计[7~11]。

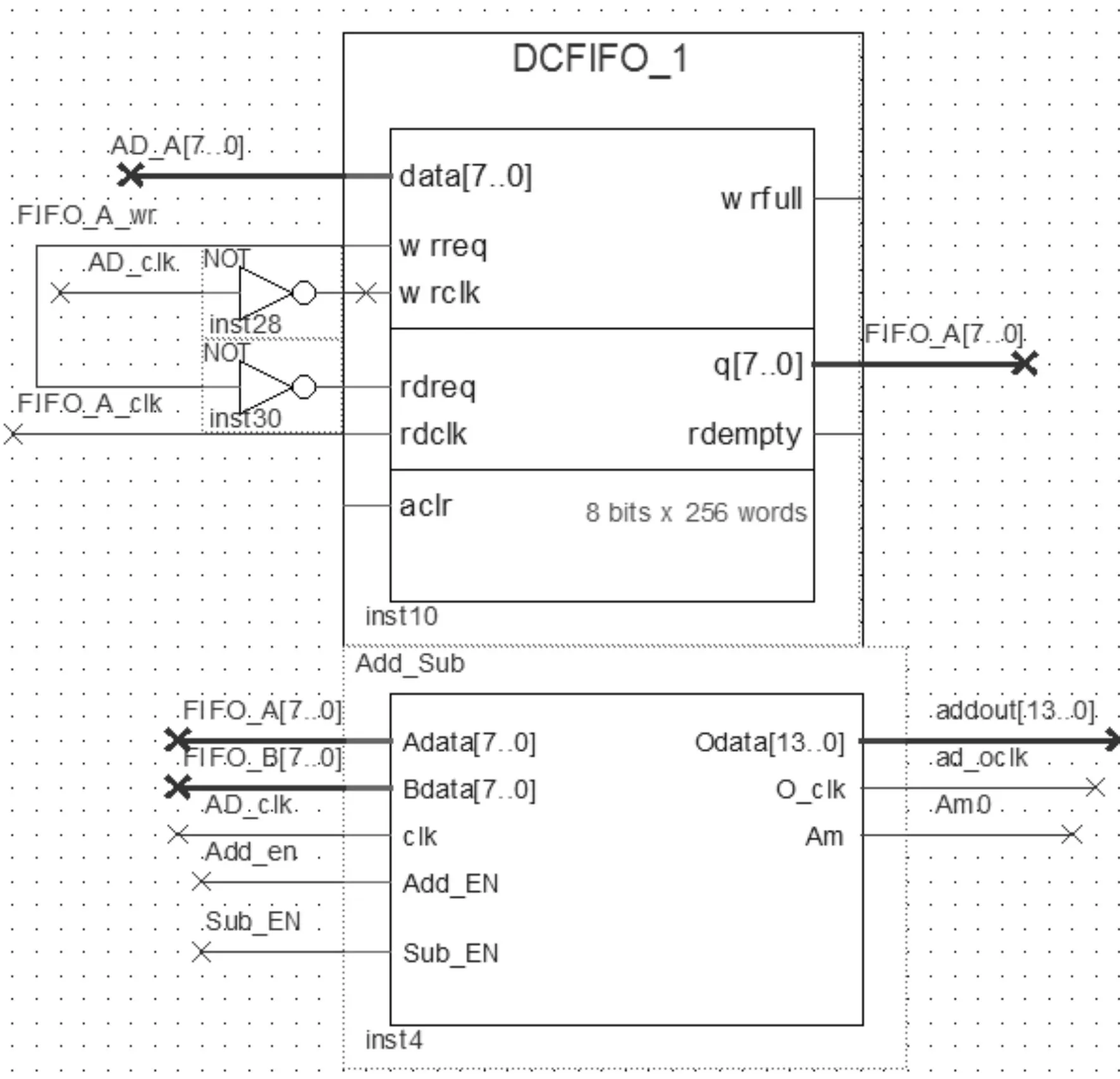

1)加/减逻辑电路

基于运放的加/减法电路比较简单,模拟电路计算公式为U0=-(Ui1+Ui2);U0=Ui2-Ui1。

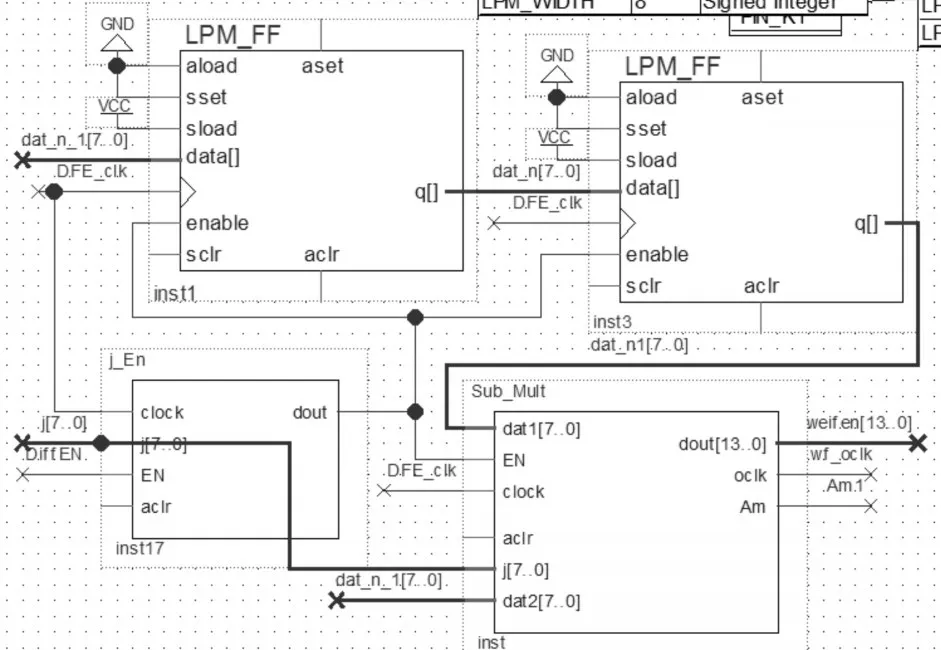

数字逻辑设计如图2。

图2 加减逻辑设计图

其中Adata连接通道A对应的缓存,Bdata连接通道B对应的缓存,clk和模数转换采样时钟同步,AS、AS_clk接数模转换输出选择器。Add_EN、Sub_EN分别为加、减功能选择端,高电平有效,Sel信号线接主控模块的加减控制端,内部逻辑根据Sel的高低,分别执行Adata、Bdata的加和减。

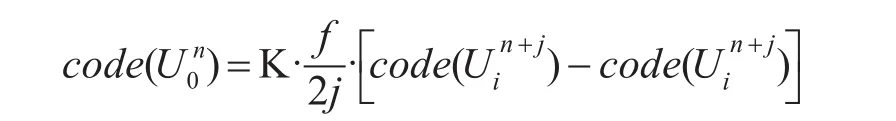

2)微分逻辑电路

集成运放微电路公式:

数字化:

其中K为比例系数,默认为1,f为模数转换频率,默认为1M,j为步长,默认为1。表示第n时刻输出的微分数字量,表示第n时刻输入的被微分函数数字量。数字逻辑设计如图3。

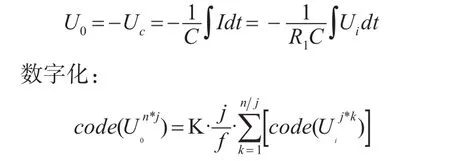

3)积分逻辑电路

集成运放积分电路公式为

其中K为比例系数,默认为1,f为模数转换频率,默认为1M。表示第n时刻输出的积分数字量,表示第k时刻输入的被积函数数字量。数字逻辑设计如图4。

图3 微分逻辑设计图

图4 积分逻辑设计图

其中,acumult模块主要完成累加的功能,DFE_clk为读FIFO时钟,sign为高时表示执行无符号数累加,为低时表示执行有符号数累加,ac_num输出当前执行的累加次数;dachange主要完成数据转换的功能,将累加结果转换为数据输出模块要求的数据格式。

3.2 人机交互

电路功能选择按钮采用左右两个自锁按键设计,按键按下,则向主控模块发送模拟功能切换指令,切换顺序依次为:加法->减法->积分->微分->加法,按下右键则进入当前功能的下一个功能,按下左键则进入当前功能的上一个功能,默认为加法电路。AD分辨率由4档位旋钮控制,4个档位分别对应采样率10K、50K、1M、10M。

3.3 主控模块

该模块以32位软核为核心,配合总线选择逻辑、分频逻辑、译码逻辑,构成片上系统。数该模块实时采集上节所述左右两个按键和旋转开关状态,解析出控制指令,控制数据处理和液晶显示[12~13]。逻辑构成如图5所示。

3.4 数据采集与输出

数据采集基于AD9288设计,该芯片支持最高100M的高速采样,模拟信号输入范围1Vpp。用户模式选择为常规模式,数据输出模式选择偏移二进制输出。数据输出模块基于AD9708设计,完成数据处理模块输出的数字量向模拟量的转换,主要包括模数转换、滤波、幅度调节等,通过比例运放电路可输出模拟信号幅度10Vpp。

图5 主控模块设计图

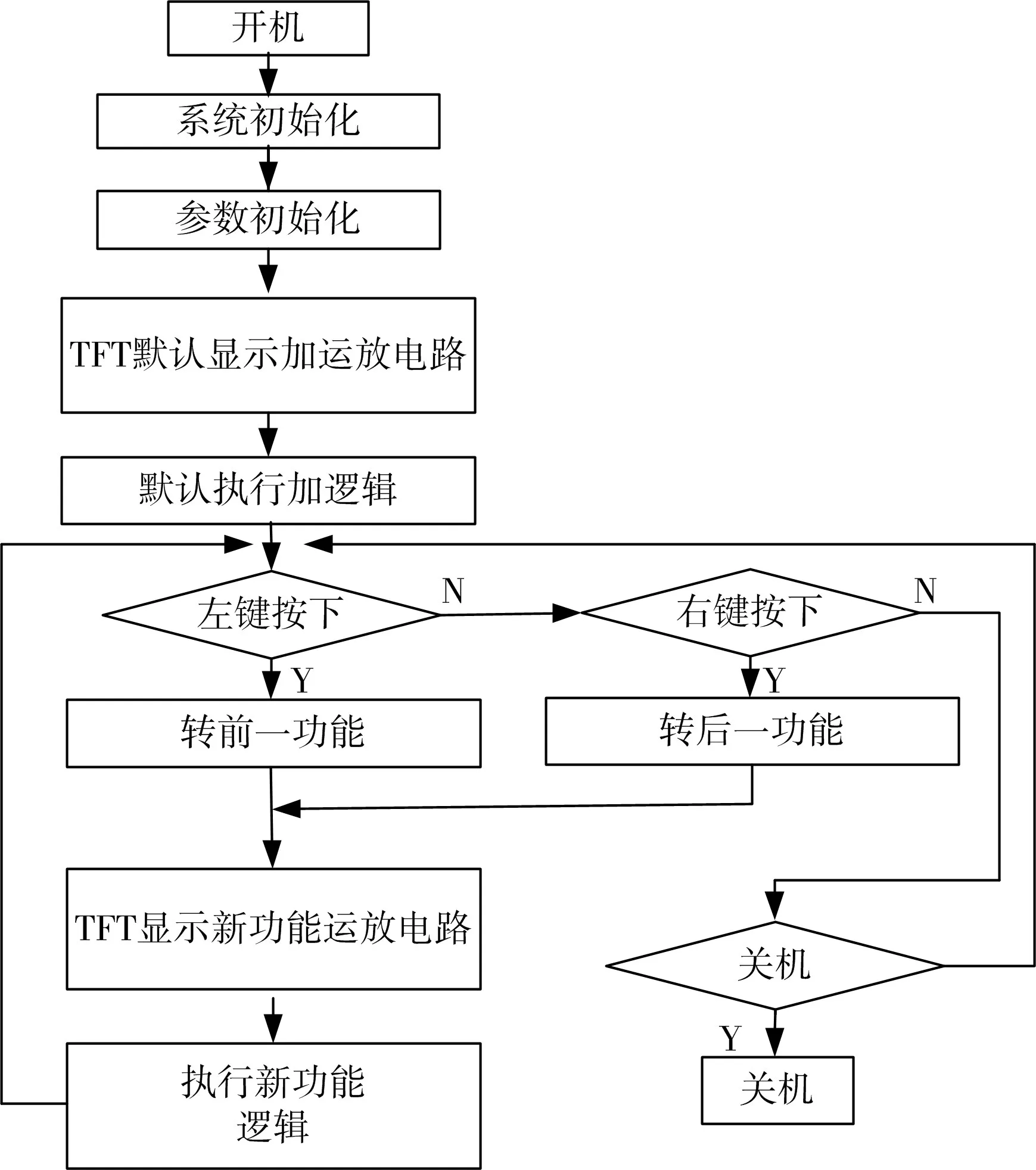

4 软件设计

软件设计流程如图6所示。系统初始化主要指可编程逻辑阵列加载外置ROM的系统数据,包括软核和各功能逻辑模块数据[14]。参数初始化主要针对显示器的功能设置(如横屏显示、白底红字等)和程序中设计的参数变量;其中电路功能状态参数默认为00,即模拟加法功能,NiosII控制TFT显示运放加法电路,用于提示当前电路功能状态和输入输出端口。主控模块译码电路根据状态参数00生成加使能信号,数据处理模块运行数字加法逻辑,DA输出总线连接加逻辑输出总线。主控模块进入扫描等待状态:当检测到左侧按键按下时(检测到下降沿信号),对状态参数进行+1操作;当右侧按键按下时,对状态参数进行-1操作;若状态参数有变化,则主控模块控制TFT清屏,并显示新的功能模拟电路,提示输入输出接口;若状态参数变化,主控模块生成新的使能信号组合,选择新的DA输出总线驱动。若没有按键按下,则执行当前功能电路。

图6 软件设计流程图

5 系统测试

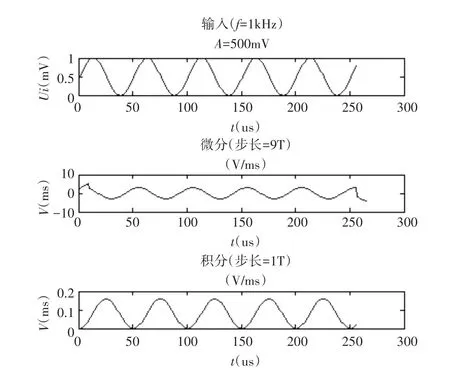

功能模拟算法的难点是微积分算法,在Matlab环境下对微积分算法进行验证,设计输入函数为Sin=0.5sin(pi/500*t);数据采样率设为50kHz;仿真结果如图7。

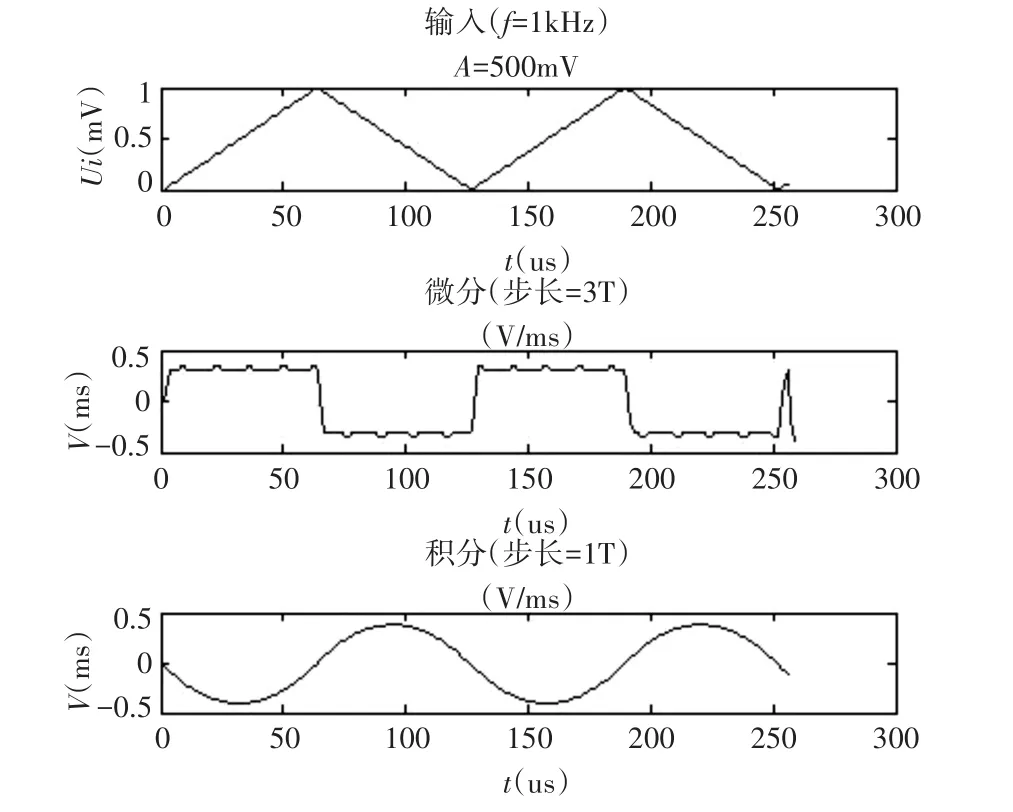

设计输入函数为三角波时,仿真结果如图8。

图7 软件仿真效果图1

图8 软件仿真效果图2

仿真表明,微积分算法和理论计算波形基本一致,能够实现对数字信号的微积分运算。其中微分图形尾部的尖脉冲是由于微分算法步长为3个采样周期导致的数字序列边界突变引起的,当信号足够长或连续时,则不会出现这种失真。其中积分图形为采用单步长积分生成的二次方函数图形。

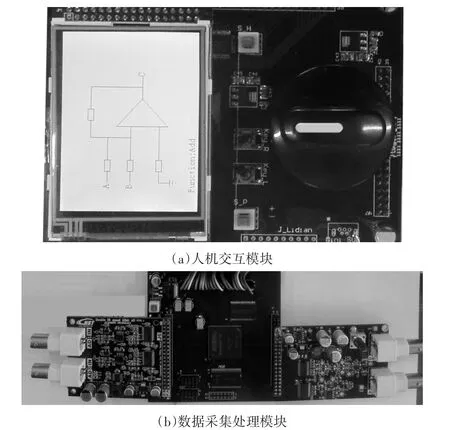

在系统软硬件设计的基础上,制作了PCB板,在QuartusII和EDS软件环境下设计了逻辑模块和软件程序,作品实物图如图9所示。

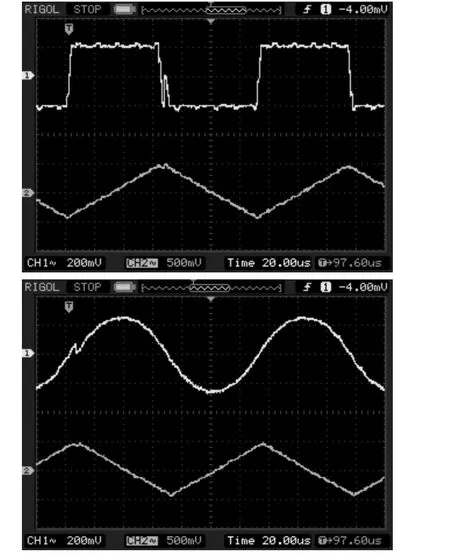

实物测试时主要针对微积分功能进行测试,输入为三角波,微积分输分别为矩形波和方向不断变化二次方曲线,如图10所示。

由于该作品主要用于引导学生由模拟电子技术学习向基于FPGA的数字信号处理学习的过渡,培养学生基于SOPC进行电子系统设计的兴趣,重在功能演示;测试结果表明,该方案达到了预期目标。

图9 作品实物图

图10 系统实际波形测试效果图

6 结语

电子技术相关课程包括模电、数电、可编程逻辑设计等,作为电子信息类本科专业的重要基础课程,对后续的信号处理相关专业课程的学习具有重要的引导作用;电子技术作为一门理论相对枯燥的课程,能否在实验环节合理设计一些综合性强、容易理解、演示效果明显的实验项目成为激发学生学习兴趣的重要措施。通过设计基于SOPC的集成运放电路功能模拟实验教学装置,能够锻炼学生综合运用模电、数电、FPGA、软核等电子技术,引导学生进入数字信号处理领域的学习,同时锻炼学生综合运用Matlab和FPGA开发工具进行信号分析与处理的能力[15],很好地体现了学以致用的实践教学培养目标,即能够锻炼学生电子技术综合实践能力,又能够深化学生对信号处理相关知识的认识,具有良好的实践教学效果。