发控设备CSD串口板卡上电复位可靠性研究

2020-07-12丁立平王志德唐晓峰范文晶

张 帅,丁立平,王志德,唐晓峰,范文晶

(上海机电工程研究所,上海 201109)

0 引 言

发控设备是执行导弹发射任务的重要设备,随着导弹发射任务越来越繁重,对发控设备各组部件之间通信的可靠性提出了更高的要求。发控设备通信接口板卡较多,在实现通用化的同时需保证较高的设备维修性,所有板卡叠加的形式已经无法满足使用要求。为此,必须在发控设备的执控组合PC104计算机系统中使用多接口模块平铺设计技术,各接口模块通过PC104总线实现电气连接。但是,这种平铺架构会导致偶发性的执控组合CSD串口板卡上电复位异常,从而导致发控设备串口通信异常。

基于上述原因,开展对发控设备CSD串口板卡上电复位异常的研究。针对引起串口通信异常的机理进行分析,设计了硬件上电复位信号检测电路和一种提高串口通信可靠性的CSD板卡复位滤波算法[1],保证发控设备的串口通信安全可靠。

1 CSD板卡在发控设备中的应用

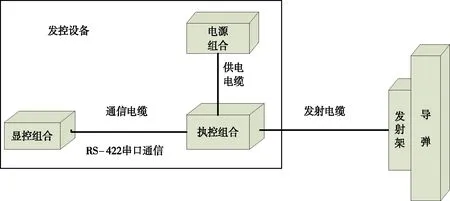

发控设备主要由显控组合、执控组合、电源组合组成,可以实现对导弹的加电控制、参数装订及发射控制。其中,显控组合与执控组合之间采用RS-422串口通信,发控设备的各组部件连接关系如图1所示。

图1 发控设备各组部件连接关系Fig.1 Launch Control Equipment connection relation

1.1 执控组合串口通信内部关系

图1中,执控组合内部PC104计算机系统主要由PC104主板板卡、CSD串口板卡、接口模块板卡、数字输入输出DIO板卡、PC104总线连接电路板组成。PC104计算机系统中使用多接口模块平铺设计技术,接口模块平铺有利于设备维修排查以及解决板卡垒接供电问题,执控组合内部板卡堆叠关系如图2所示。

图2 板卡堆叠关系示意图Fig.2 Boards stack relation diagram

执控组合内部串口通信方式为PC104主板板卡工业标准架构(Industrial standard architecture,ISA)总线经PC104总线连接电路板,对CSD串口板卡进行上电复位时序以及串口通信控制,具体的执控组合内部串口硬件关系如图3所示。

图3 执控组合串口内部硬件关系Fig.3 Executive Control Device serial port internal hardware relation

在与显控组合进行串口通信时,会偶发性地出现串口通信故障,直观现象为执控组合不在线或执控组合接收确认异常。通过采用CSD串口板卡寄存器值回读技术进行监测,显示CSD串口板卡上电复位不正常。

执控组合内部CSD串口板卡与PC104主板之间通过标准的ISA总线[2]接口进行连接,CSD串口板卡内部逻辑如图4所示。

图4 CSD串口板卡内部逻辑框图Fig.4 CSD serial port board internal logic block diagram

图4中,PC104主板ISA总线的8位数据总线、20位地址总线和5位控制信号线连到CSD串口板卡的现场可编程门阵列(field programmable gate array,FPGA)。板卡的通用异步收发器[3](universal asynchronous receiver/transmitter,UART)控制器占用的空间资源和中断资源可以由PC104主板软件设置,并通过FPGA保存在CSD板卡的电可擦可编程只读存储器(electrically erasable programmable memory,EEPROM)内。板卡上电复位后,FPGA自动读取EEPROM的配置数据,获取各个功能单元的基地址和中断号资源。

对显控组合进行了多次串口通信测试,如图5所示。执控组合上电复位时,FPGA加载EEPROM配置数据[4]的过程中,加载了错误数据,导致CSD串口的基地址或者中断号与软件设置不符,从而导致CSD串口板卡复位不正常。

图5 串口通信监测图Fig.5 Serial port communication monitoring diagram

1.2 CSD串口板卡上电复位异常分析

执控组合CSD串口板卡在PC104主板完成复位后会给FPGA提供一个ISA_RST信号,FPGA通过I2C总线从EEPROM加载地址I2C_ADR为00~17的18个数据,完成对CAN、串口、DIO等外设的复位。

在FPGA内部逻辑[5]中,上述配置数据加载过程是通过有限状态机结构来实现的。该状态机的配置加载流程如图6所示。PC104主板复位完成后,加载地址I2C_ADR由FF跳到00,在系统时钟CLK信号的驱动下,加载地址I2C_ADR从00累加到17,循环读取18个EEPROM数据。期间如果发生任何异常,会使加载地址I2C_ADR跳转到其他非法值,则状态机陷入死循环,导致执控组合串口通信读写寄存器错误。

图6 配置加载流程图Fig.6 Configuration loading flow diagram

2 CSD板卡上电复位检测电路及滤波技术实现

串口通信试验显示串口板卡对于PC104主板传输过来的104根ISA总线中的ISA_RST信号(即上文中提到的串口板卡复位信号)的毛刺信号进行了复位响应,但毛刺的脉宽太窄,导致FPGA内部逻辑的建立时间和保持时间不能满足时序要求,状态机工作在亚稳态状态,从而导致执控组合偶发串口通信故障。

根据以上执控组合内部串口通信机理以及对CSD串口板卡上电复位异常的分析,设计了硬件复位信号检测电路以及软件复位信号滤波算法。

2.1 硬件复位信号检测电路

对ISA_RST信号进行了复位信号检测,发现信号中的毛刺会对复位电路产生干扰。采用复位信号检测电路来检测PC104主板的复位信号波动情况,避免串口板卡在毛刺干扰状态下工作。选择PC104主板供电电源作为复位信号检测信号的参考信号。复位检测电路安排在电源附近,可以保证毛刺干扰在源头就能被复位信号检测电路屏蔽掉[6]。复位信号检测电路设计时要求能对主板复位信号的尖锋变化进行屏蔽,本文所采用的复位信号检测电路如图7所示。

图7 复位信号检测电路Fig.7 Reset signal detection circuit

在复位信号ISA_RST无效(低电平)的情况下,当电源信号上有毛刺干扰时,复位信号毛刺干扰大于1.5VDD。干扰信号持续1 ns 以上级别时,复位信号检测信号将被拉低,直至复位信号ISA_RST有效(高电平),复位信号检测信号再恢复高电平。复位信号输出信号RST_OUT能在无毛刺干扰状态下不断刷新复位信号检测电路输出的信号,并输出正确的RST_OUT信号。有毛刺干扰的情况下,复位信号检测电路能使串口板卡截止输出复位信号,等待毛刺干扰滤除后再恢复正常复位信号输出。复位信号检测电路停止工作表现为计数器停止计数[7],状态机进入空操作状态。综上所述,此复位信号检测与状态机响应流程如图8所示。

图8 复位信号检测及状态机响应流程Fig.8 Reset signal detection and State Machine response process

2.2 软件复位信号滤波算法

除了增加硬件复位信号检测外,本文还提出了一种串口通信滤波算法,旨在提高CSD串口板卡对于总线中毛刺的处理能力。对执控组合CSD串口板卡FPGA进行了以下两方面的驱动软件升级:

1) 在原驱动[8]的基础上加入了10 ms的ISA_RST复位信号滤波处理。当采集到ISA_RST复位信号高电平时,计数器开始对芯片时钟CLK信号连续计数,芯片主频为40 MHz。FPGA在10 ms时间内连续采集400 000个CLK信号后,串口板卡才能确认收到一个准确的串口板卡复位信号,CSD串口板卡进行正确复位。

2) 在原驱动的基础上加入了复位信号非正常掉电保持功能,即采集到ISA_RST复位信号高电平受到ISA线路毛刺的干扰而出现短时非正常掉电时,当掉电超出阈值不超过3个CLK时钟信号脉宽,计数器不进行清零操作;反之,如果掉电超过3个CLK时钟信号脉宽,则计数器清零,本次ISA_RST复位信号无效。这样就确保了复位信号电平在受到干扰时也能保持,从而提高了复位电路的抗干扰能力。

经过上述升级后的执控组合CSD串口板卡FPGA驱动程序复位信号滤波算法工作流程如图9所示。

图9 复位信号滤波算法工作流程Fig.9 Reset signal filtering algorithm flow diagram

3 软件仿真及硬件电路实物验证试验结果分析

3.1 软件仿真试验结果分析

图9即为本文提出的复位信号滤波核心算法,升级后的CSD串口板卡上电复位经过10ms滤波能够对ISA总线上的毛刺进行过滤,对于复位信号ISA_RST上的毛刺不响应,避免板卡复位异常。另外,对于复位信号异常掉电不超过3个CLK时钟周期[9]的情况,该算法可对复位信号持续计数,确保复位正常进行。下面用Quartus Ⅱ软件对升级后的滤波算法进行仿真验证。

1) 对升级的FPGA驱动程序进行时序仿真

用Quartus Ⅱ对升级后的程序进行时序仿真,如图10所示。由图10可知,当计数器对时钟CLK信号计数达到40 000之后,脉宽为10 ms,CSD串口板卡确认接收到一个准确的上电复位信号。

图10 时序仿真Fig.10 Timing simulation

2) 对升级的FPGA驱动程序进行边界条件的测试仿真

用Quartus Ⅱ对升级后的程序进行边界条件的测试仿真,如图11所示。由图11可知,当PC104主板复位信号掉电时间不超过连续的3个CLK信号周期时,计数器会持续计数;而当PC104主板复位信号掉电时间超过连续的3个CLK信号周期时,计数器会重新计数。

图11 边界测试仿真Fig.11 Boundary test simulation

上述对驱动程序时序测试以及边界测试的仿真验证表明,执控组合CSD串口板卡上电复位驱动程序能够对PC104主板的ISA_RST毛刺进行滤波处理,并能对信号的异常掉电进行保持处理,确保CSD串口板卡的正确复位。

3.2 硬件电路实物验证试验结果分析

图12为更新硬件电路后的CSD串口板卡实物。

图12 更新硬件电路后的CSD串口板卡Fig.12 CSD serial port board after updating hardware circuit

为了验证上述硬件复位信号检测电路,保持执控组合硬件架构不变,其它硬件架构、软件程序、连接关系保持与图1、图3一致,在实验室对板卡的硬件环境串口通信进行了各种状态下的实物验证试验,对比试验结果可以发现:

1) 硬件电路更新前,进行100次如图5所示的串口通信试验,在第2次和第14次试验中串口通信故障复现,第2次试验为执控组合串口接收功能异常,第14次试验为执控组合串口发送功能异常。

2) 添加硬件复位信号检测电路,进行100次如图5 所示的串口通信试验,串口通信故障未复现。

上述结果表明,增加硬件复位信号检测电路的CSD串口板卡可靠性得到提高,故障未复现。

4 结束语

本文针对发控设备串口通信偶发性故障,设计并实现了复位信号检测电路对PC104主板复位信号的检测,同时设计了一种基于CSD串口板卡FPGA软件驱动的上电复位滤波算法。升级后的驱动算法能够对ISA总线中的毛刺起到滤波效果,可防止板卡异常复位导致通信故障。仿真和硬件电路实物试验验证表明,该复位检测电路和滤波算法可明显提升串口通信的可靠性和抗干扰能力。该成果对同类型的通信电路具有较好的工程借鉴意义。