一种新的基于FPGA的超宽带实时信号侦测技术*

2020-07-09李佳洋

李佳洋

(中国西南电子技术研究所, 成都 610036)

0 引言

战场环境中电子信号主要以雷达信号为主,还包括敌我识别信号、数据链信号等。通过对雷达信号进行侦察,可以全天候、安全、隐蔽的在复杂电磁环境中获取雷达辐射源的位置、信号参数、工作状态、型号等各类信息,有效支撑对周边地区综合态势和战时战场电磁态势的掌握,并实时引导电子进攻和防护作战。针对电子信号侦测的需求越来越多,电子信号侦测瞬时信号带宽大,采样率高,实现难度大等特点,对FPGA处理资源要求也越来越高。一般多采用多相滤波结构技术[1],但带来过渡带信号重复检测、宽带信号分裂等问题。文中提出了一种基于单通道信号检测引导的直接中频信号侦测流程,可避免重复检测和信号分裂问题,并且FPGA实现架构简单,参数测量精度高,资源利用率少。

1 算法流程

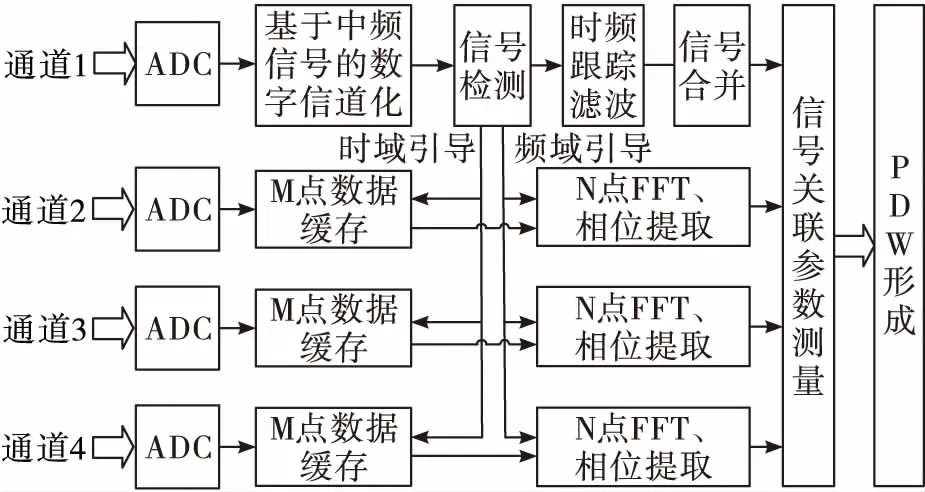

以4通道传统电子信号侦测系统[2]为例,其流程如图1所示。从图中可以看出为了满足检测信号的同步,传统电子信号侦测流程需要4路中频信号都完成ADC转换、数字信道化、信号检测以及信号合并,随着未来系统对侦测瞬时带宽的覆盖、采样率以及系统通道数的需求越来越大,基于基带信号的传统电子信号侦测处理所需的FPGA处理资源也呈几何状态增加,已无法满足未来装备小型化、架构综合化、系统低功耗的发展趋势。

图1 传统电子信号侦测流程图

图2 基于中频数据的单通道信号检测引导的侦测流程

为了满足瞬时超宽带以及实时信号侦测的资源需求,基于单通道信号检测引导的直接中频信号侦测流程如图2所示。从图2中可以看出与传统侦测流程相比,新的侦测方法只有1通道信号完成基于中频信号的信号检测、信号合并、参数测量等,2~4通道只完成相位提取后与通道1的相位参数进行关联,用作后续侧向使用,这样大大节约FPGA的资源并且实现流程简单。

2 算法原理

2.1 基于中频信号的数字信道化

数字信道化处理一般采用多相滤波算法或滑动DFT算法[3]。多相滤波算法比较成熟,但应用于雷达信号侦察处理时其过渡带带来了信号重复检测、宽带信号分裂等问题。为此,文中采用基于中频信号的滑动DFT和时频跟踪滤波的信道化处理算法。该方法在处理增益和多信号分离能力方面具有较好性能,且可避免多相滤波方法容易出现的信号分裂等问题。

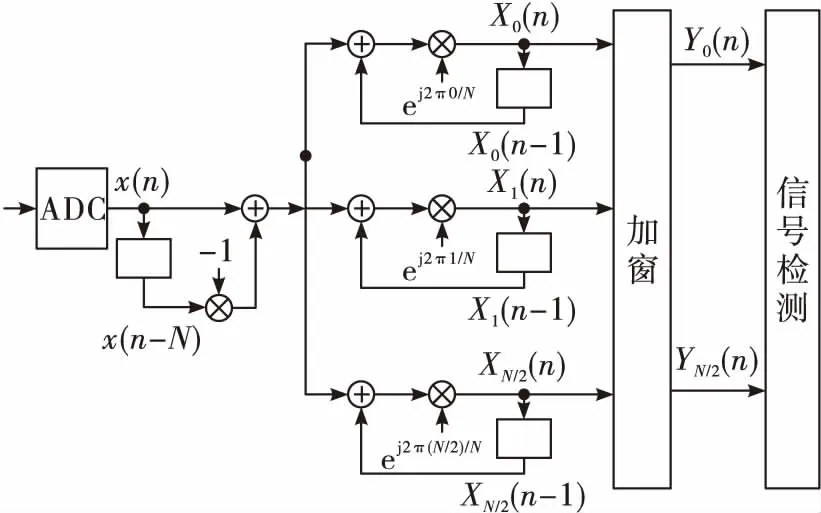

用滑动DFT的雷达信号侦察处理,就相当于用一个固定长度随时间滑动的滑动窗口来选择样本并进行DFT运算,分析其不同时刻的频谱信息。其流程如图3所示。

图3 基于中频的滑动DFT数字信道化

假设滑窗长度为N,数据窗每次滑动一个样点可得到一组频谱数据X(n)和X(n-1),两组数据的DFT计算结果为:

Xk(n-1)=x(n-N)e-j2πkN+x(n-N+1)e-j2πkN+x(n-N+2)e-j2π2kN+ …+x(n-1)e-j2π2kN

(1)

Xk(n)=x(n-N+1)e-j2πkN+x(n-N+2)e-j2πkN+x(n-N+3)e-j2π2kN+ …+x(n)e-j2π2kN

(2)

整理上式可得到:

Xk(n)=x(n-1)-[x(n-N)+x(n)]e-j2πk/N

(3)

上式即为滑动DFT方程,它可实现逐点DFT运算输出,每次计算量较小。由于直接对输入信号进行DFT运算,会存在频谱泄露,采用时域加窗(频域卷积)的方法可降低频谱泄露,如下式所示。

Yk(n)=2Xk(n)-Xk-1(n)-Xk+1(n)

(4)

式中:Y(n)即为n时刻的频谱数据。

2.2 时频跟踪滤波处理

时频跟踪滤波算法主要解决信号时域重叠以及频域跨信道的问题。在实际情况中当2个信号同时被接收机检测时,就会出现时域上的重叠。

图4 时频跟踪滤波处理流程示意图

时频跟踪滤波处理主要由时域关联和频域关联组成。|F(t,k)|2中t表示信号的时间信息,k为信号的频域信息。每种信号都有各自特殊的时频特性,根据信号的时频特性,就可分辨出各种信号。

在前端通过滑动窗后的每一路FFT可测量信号的中心频率。而AD中频信号采集后的并行多路滑动窗就可看成到达信号的时间轴,并可测量出信号的持续时间。

时域关联可根据信号的持续时间将由于高采样以及滑动DFT的并行多路检测的多个信号合成一个信号。频域关联时可将时域上重叠的信号,根据其出现的不同子频带,分离成不同信号,也能通过时域上的连续将不同子频带上的信号合并成符合相应调制类型的信号。

3 基于FPGA实现

3.1 基于中频的滑动DFT实现

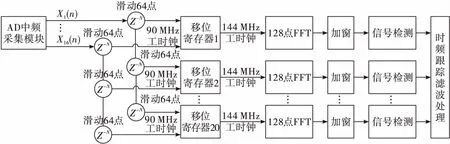

用FPGA实现基于中频的滑动DFT数字信道化,设1.44 Gsps采样率,128路子信道,子信道带宽11.25 MHz。FPGA实现流程[4]如图5所示。

在FPGA处理过程中最重要的是实时性的处理,1.4 Gsps采样率的AD数据解析模块在FPGA中是输出16路,每路的工作时钟90 MHz。数字信道化中滑动的点数根据时间分辨率来决定,一般来说时间分辨率越高越好,但在宽带数字信道化处理时逐点滑动会带来后面FPGA的储存资源和DSP资源消耗巨大,目前市面上的FPGA资源都不满足。因此滑动点数在宽带信号处理时应根据参测指标来决定,一般雷达信号最小测量脉冲宽度为0.1 μs,时间分辨率的计算公式如下:

图5 基于中频信号的滑动DFT数字信道化FPGA实现流程

(5)

式中:N为滑动点数,1.4 Gsps采样率滑动64点的时间分辨率为0.046 μs,满足雷达信号最小测量脉冲宽度0.1 μs的要求。

移位寄存器的个数必须满足一定FPGA处理时序要求。1.4 Gsps采样率下AD模块在FPGA中输出16路,每路的工作时钟90 MHz。为了保证AD中频数据的实时性以及完整性,移位寄存器的个数必须满足以下关系:

(6)

式中:移位寄存器的个数为n,移位寄存器输出工作时钟为Tout,由于进移位寄存器前中频数据为并行16路,因此滑动64点,工作时钟延时tdelay=4个周期,nfft=128路子信道,考虑FPGA在设计实现时的时序优化,移位寄存器输出工作时钟Tout取144 MHz。因此移位寄存器的个数为20。

3.2 时频跟踪滤波处理FPGA实现

时频跟踪滤波处理[3]在FPGA中的设计主要是多层级逻辑判断,主要作用是合并多频点信号以及分离同时到达的不同信号。

下面主要介绍分集信号、频率调制信号以及线性调频信号几种有代表性的多频点信号的时频特性,如图6~图8所示。

图6 频率分集信号时频图

图7 频率调制信号时频图

通过上述的时频图可以看出不同信号的时频特性是不同的[5],频率分集信号在时间上是同时在2个或多个频点有信号,频率调制信号在时间上是连续在2个频点有信号,线性调频信号是频率随时间在线性变化。如图5所示的基于中频信号的滑动DFT数字信道化实现框架中,每一路滑动处理相当于时间轴,每一路中128点FFT相当于频率轴,根据信号时频特性就能判断出多频点信号是多个独立单频点信号还是一个信号的子脉冲,也可根据时频特性将同时达到的多个信号分离开来。

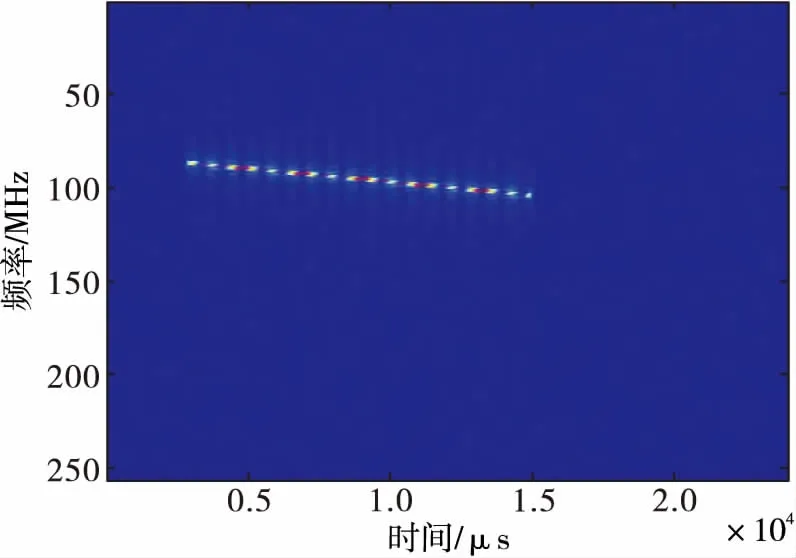

图8 线性调频信号时频图

4 工程实现结果

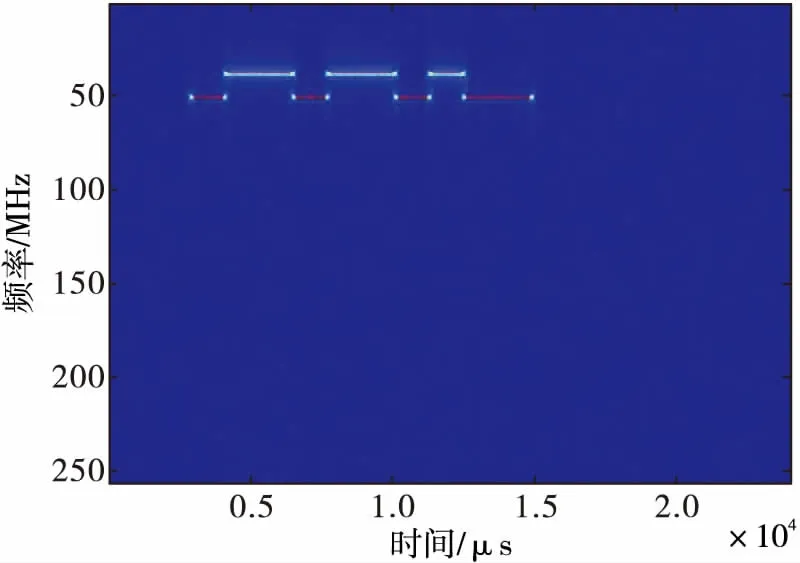

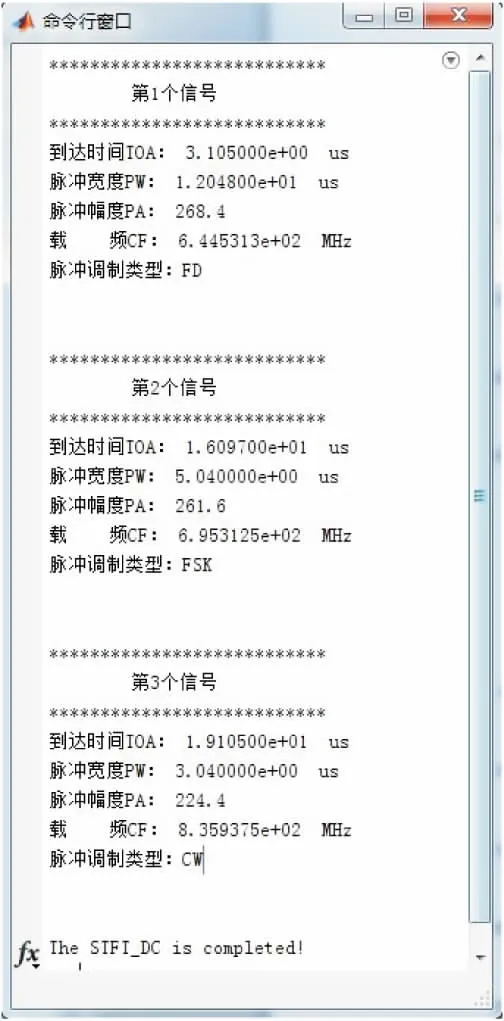

工程实现时FPGA选用xilinx公司V7690T,采样率1.4 Gsps,中频瞬时带宽500 MHz。中频信号为频率分集信号、频率调制信号以及常规脉冲信号的混合信号。其中频率分集信号FD脉冲宽度12 μs、载频644.5 MHz,频率调制信号FSK脉冲宽度5 μs、载频695.5 MHz,常规脉冲信号CW脉冲宽度3 μs、载频836 MHz。通过FPGA检测处理生成PDW(脉冲描述字)后经MATLAB读取结果,如图9所示。

图9 FPGA参测结果

从图9中可看出:FPGA已成功检测出3个信号,并且脉冲宽度的检测精度在0.05 μs以内,测频精度在0.2 MHz以内,完全满足系统指标。

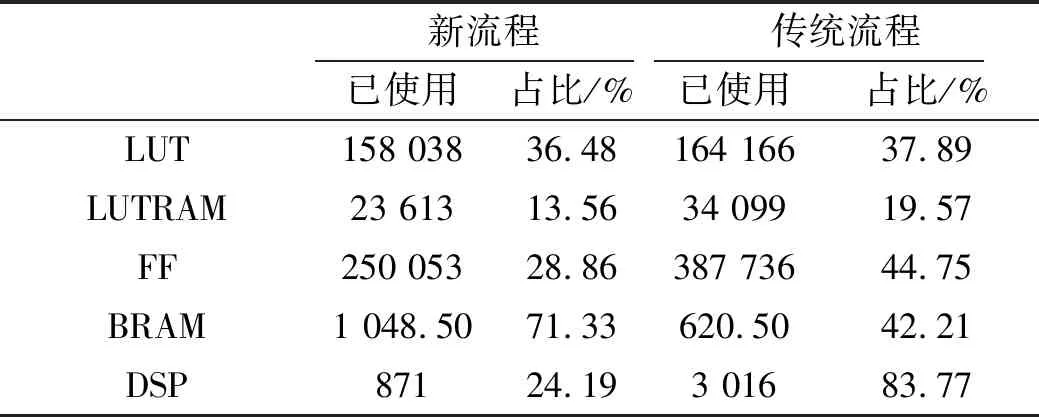

基于中频数据的单通道信号检测引导的侦测流程(新流程)和传统电子信号侦测流程(传统流程)完成4通道信号检测的FPGA的资源消耗如表1所示,从表中对比来看新的信号检测流程除了BRAM的消耗比传统侦测流程要高以外,其余资源使用都大幅减少,特别是DSP资源,节约了50%多。

表1 FPGA资源对比

5 结论

文中提出了基于单通道信号检测引导的直接中频信号侦测流程,采用了基于中频的滑动DFT数字信道化以及时频跟踪滤波处理等技术,在相同的参测指标情况下,新的侦测流程比传统电子信号侦测流程占用更少的FPGA资源,能在低功耗FPGA上实现,降低系统功耗,增加系统可靠性。