可编程宽带噪声干扰源设计*

2020-07-09陈帅霖刘满国闫小东

陈帅霖,陈 炜,吕 芳,刘 坤,刘满国,闫小东

(1 西安现代控制技术研究所, 西安 710065; 2 93811部队, 兰州 730000)

0 引言

为验证多个项目中雷达导引头的抗干扰性能,并方便在内场与外场兼顾使用,需要设计一款设置灵活、参数可调的宽带干扰源。噪声调频干扰具有较大的干扰带宽和较高的噪声功率,是目前阻塞式干扰中最常用的一种干扰形式,广泛的运用于对雷达、导引头、GPS、无线图传、遥测、无线通信等系统中[1]。

噪声调制信号发生器的实现方式有3种,分别为模拟式、数字式、混合式[2]。模拟式噪声调制信号发生器的调制信号与控制信号都通过模拟电路来产生,技术较为成熟,但功能单一,干扰样式固定;数字式噪声调制信号发生器的调制信号与控制信号都通过数字技术来产生,以直接数字频率合成器(direct digital synthesizer, DDS)为基础,具有较高的灵活性;混合式噪声调制信号发生器的调制信号由模拟电路产生,宽带干扰信号由DDS生成,兼顾了模拟调制随机性强和数字方式输出灵活的优点,但存在模拟调制噪声源单一的缺点[3]。

目前,国内大多数数字式噪声调制信号发生器中的噪声源信号都是通过调用函数库,利用超载函数完成调频功能,计算量大,运行速度慢,灵活性差;大多数模拟式噪声调制信号发生器中的噪声源信号都采用物理方法产生,随机性较好,但对外界环境较为敏感。文中研究一种基于DDS的纯数字噪声调频信号产生方法,生成的干扰波形具有严格的相干性和可重复性,对环境不敏感,并且具有高速、灵活、可控等优点,可满足在内场与外场对雷达导引头或其他信号灵活多变的干扰任务需求。

1 方案设计

1.1 系统方案

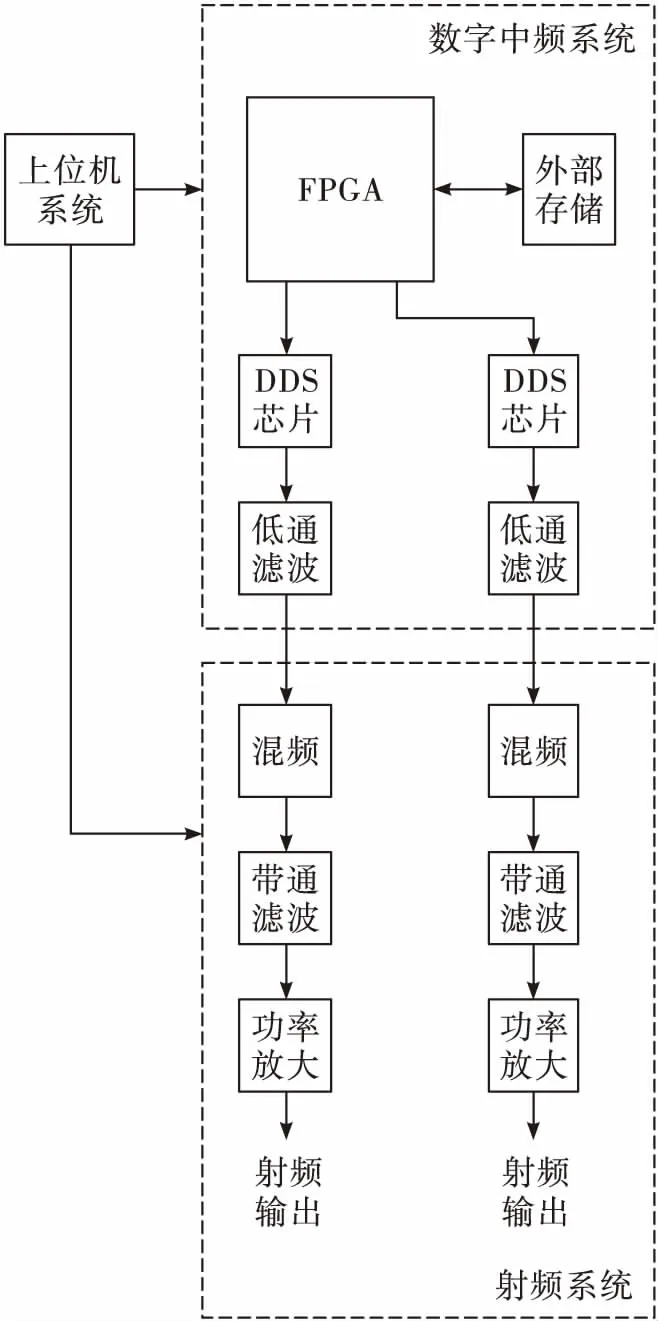

为了兼顾噪声调频信号与欺骗式干扰信号的生成,并保证信号产生速度与质量,采用专用DDS芯片AD9915进行干扰信号产生。系统有3个分系统:上位机系统、数字中频系统、射频系统。上位机系统用于输入指令,控制输出干扰信号的中心频率、带宽、功率等参数,控制数据存储与回放;数字中频系统用于产生宽带中频干扰信号,将干扰信号控制字存储至外部存储器,读取外部存储器中的干扰信号控制字并回放定制干扰,是系统的核心;射频系统用于上变频,将前级系统生成的中频干扰信号混频至所需射频频段[4]。系统框图如图1所示。

图1 系统总体框图

产生噪声调频干扰信号的流程如下:

首先,在FPGA内部产生符合高斯分布的随机序列。高斯随机序列的产生分为两个步骤:第一步,产生均匀分布的随机序列;第二步,根据中心极限定理,将均匀分布的随机序列处理成为高斯随机序列。

其次,将FPGA产生的高斯随机序列作为噪声源,依据系统输出要求,计算相应的DDS控制字,由DDS产生符合要求的中频宽带干扰信号。

最后,经过低通滤波、混频、带通滤波、功率放大,得到最终的射频输出噪声干扰信号。

在该方案中,通过FPGA,可以设置不同的干扰参数,控制DDS芯片实现欺骗式与压制式的多种样式的干扰。此外,还可以加载和存储定制干扰的DDS控制字,以生成定制干扰波形。

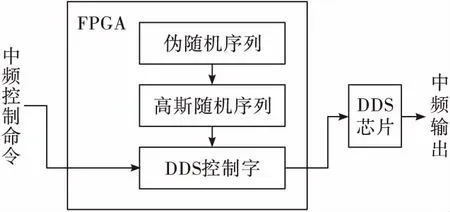

1.2 数字中频系统

数字中频系统是可编程宽带干扰源中的核心,主要功能是由FPGA生成高斯白噪声序列作为噪声调频信号的噪声源,由FPGA计算出相应的频率控制字,来控制DDS芯片产生宽带中频干扰信号。数字中频系统的原理框图如图2所示。

图2 数字中频系统框图

首先,由FPGA中的线性反馈移位寄存器,产生相对独立且均匀分布的伪随机序列。

其次,根据中心极限定理,利用伪随机序列产生符合高斯分布的随机序列,将此高斯随机序列作为噪声源。

再次,根据输入要求,如带宽、时宽、频率分辨率等参数,计算时宽范围内噪声调频信号的瞬时频率,由此得到DDS芯片控制字。

最后,将控制字输入DDS芯片,得到中频噪声调频信号。

2 关键技术及解决途径

2.1 噪声调频信号生成

噪声调频信号的时域表达式如下:

(1)

式中:vN(t)为高斯分布限带噪声;Am为载幅;fc为载频;Kf为调频指数;φ0为载相。

vN(t)的概率密度函数为:

(2)

式中:σv为噪声方差的均方根。

令ωc= 2πfc,则瞬时角频率ω(t)为:

ω(t)=ωc+KfvN(t)

(3)

功率谱GN(ω)为:

(4)

令Kfσv=ωde,Δω=ω-ωc=KfvN(t),其中ωde为有效频偏,Δω为瞬时频偏,则有:

(5)

式中:P0为总功率,与载波总功率相同,为:

(6)

当有效调制指数mfe=Kkσv/Δfv≫1(其中,Δfv为噪声源带宽),即当噪声源功率一定,所需输出带宽远大于噪声源带宽时,噪声调频信号的半功率频谱带宽Δf0.5可近似表示为:

(7)

由式(7)可得,噪声调频信号的带宽只与噪声调频斜率Kf及噪声源功率均方根σv有关,且成正比。一般FPGA生成的噪声源随机序列都会做归一化处理,所以只要控制Kf,就能得到所需的噪声调频信号带宽。

2.2 噪声源随机序列产生

要产生噪声调频干扰信号,先需要产生一个高斯白噪声随机序列,作为调频的噪声源。产生高斯随机序列分两步:首先产生均匀随机序列,再由该序列生成高斯随机序列[5]。

数字产生伪随机码的方式有许多种,其中M序列具有较理想的伪随机性,自相关函数尖锐,性能较好,最为常用[6]。并且大部分FPGA中都有现成的线性反馈移位寄存器(linear feedback shift register, LFSR)的IP核可以直接调用,用来生成均匀分布的随机序列十分方便,这里不再赘述[7]。

生成n个独立同分布的均匀随机序列X1,X2,…,Xn后,根据中心极限定理将其累计相加,再对相加的结果进行标准化处理,即可得到高斯随机序列[8]。假设生成随机序列的期望和方差为:

将X1,X2,…,Xn累加后,随机变量Yn满足:

(8)

Yn的分布函数Fn(x)对于任意x满足:

(9)

得到的结果服从高斯分布。n的取值越大,即用来累加的均匀分布随机数越多,变换得到的随机数越接近于高斯分布。

2.3 DDS芯片控制

得到高斯随机序列后,需要使用DDS芯片来产生噪声调频干扰信号。所选芯片为AD9915,具有32位并行数据接口,能够迅速的改变调频频率,所以这里直接计算出每个时刻的瞬时频率,控制DDS芯片,来产生所需的噪声调频干扰信号[9]。

由式(3),有f(t)=fc+2πKfvN(t)。根据设计需求,计算所需的Kf值,再由FPGA生成的噪声源序列,可得噪声调频信号到各个时刻的瞬时频率。

AD9915的输出频率fout由DDS频率控制输入的频率控制字(FTW)控制。fout、FTW和fsys之间的关系式为:

(10)

式中:频率控制字FTW是介于0至2 147 483 647 (即231-1)之间的32位整数,表示完整32位变量的低半部。此范围包括从DC至奈奎斯特频率(1/2fsys)内的所有频率。

对于给定的fout值,可通过式(10)求出FTW,即:

(11)

式中:函数round(x)表示四舍五入取整,因为FTW必须为一个整数值。

3 仿真验证

依照系统设计流程,使用MATLAB软件对所需的宽带噪声调频干扰信号进行仿真。

3.1 高斯随机序列仿真

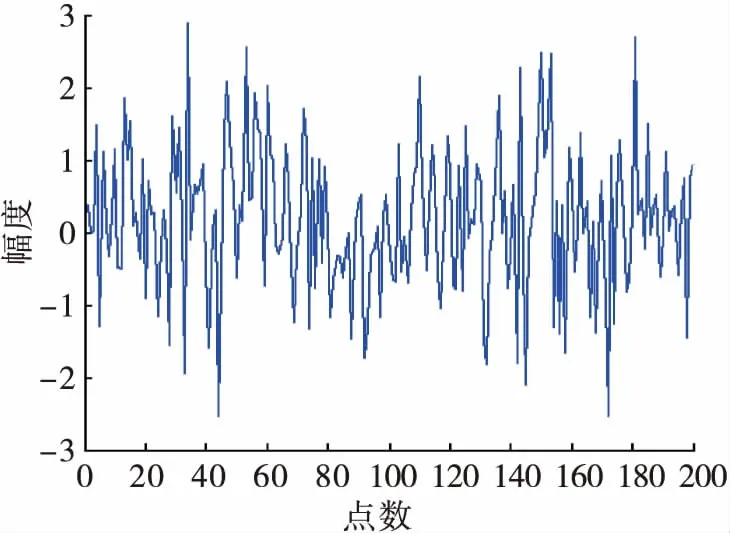

由MATLAB生成32组200点的均匀随机M序列,随机选择两组序列,结果如图3所示。

图3 均匀随机M序列

图4 高斯随机序列时域图

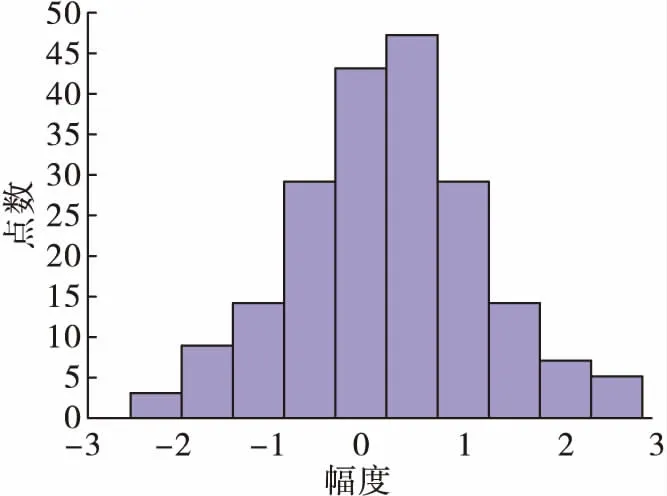

按照2.2节的方法,根据中心极限定理,对生成的均匀随机M序列进行处理,得到高斯分布的随机序列,结果如图4所示。对生成的高斯随机序列进行统计,得到的统计直方图如图5所示。

图5 高斯随机序列统计直方图

此方法可产生任意带宽与长度的高斯随机序列,运算速度快,随机性强。

3.2 宽带噪声调频干扰信号仿真

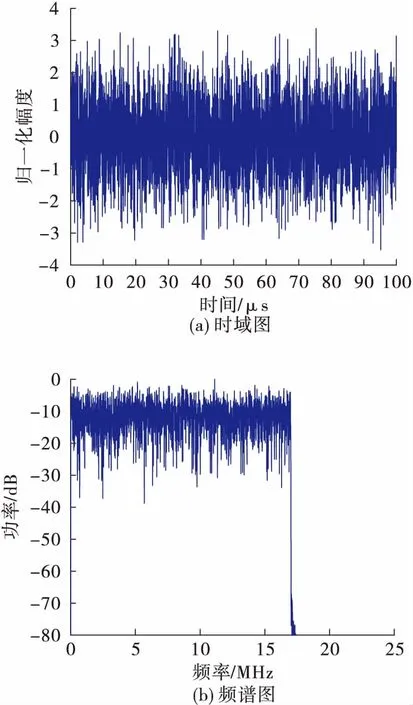

首先产生带限高斯白噪声,作为调频噪声源,根据3.1节生成100 μs的高斯随机序列,通过截止频率为17 MHz的低通滤波器,并归一化,得到的噪声源如图6所示。

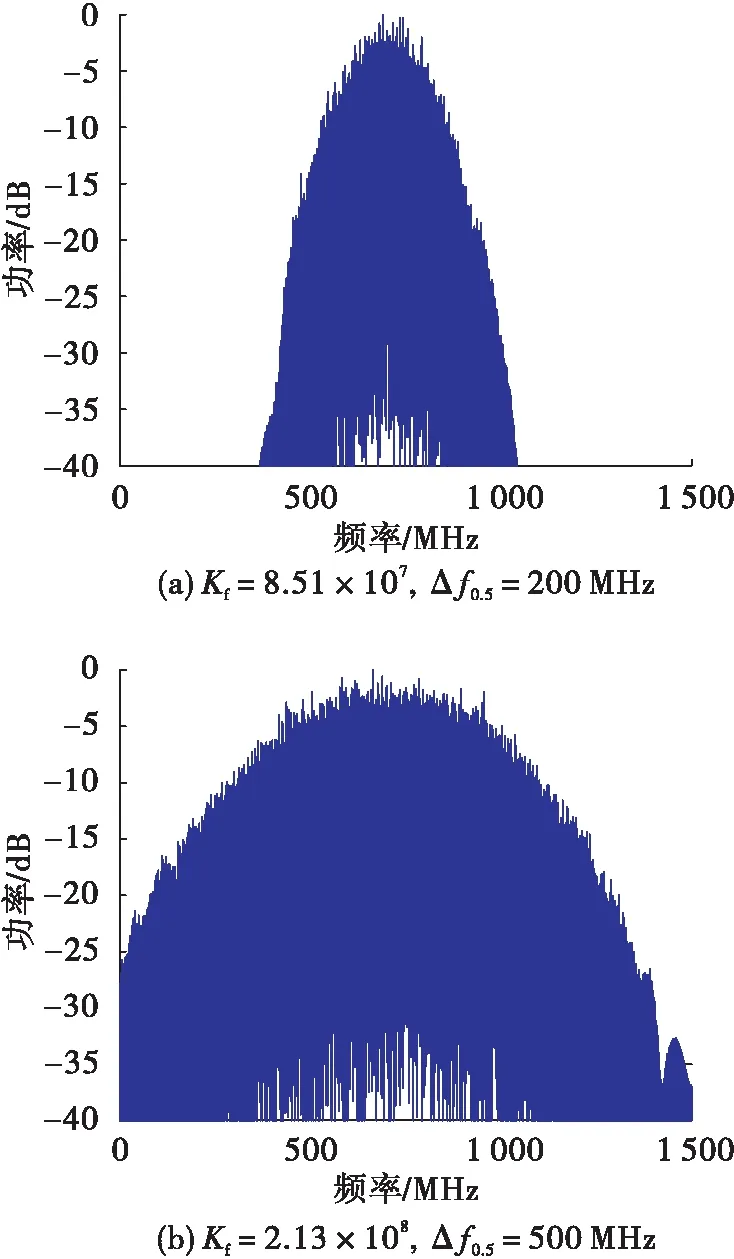

由此可见,噪声调频信号的频谱宽度随着Kf的增大而增大。

假设载频为700 MHz,初始相位为0,根据式(1)可得不同调频斜率下的噪声调频干扰信号,如图7所示。

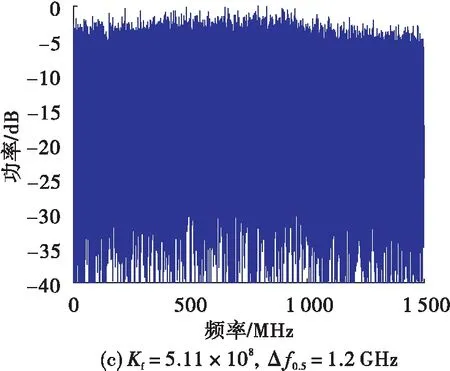

固定Kf为2.13×108,改变噪声源带宽为3 MHz和21 MHz,噪声调频信号频谱如图8所示。

不同噪声源带宽下的调频噪声干扰信号的干扰带宽都为500 MHz,由此可见,在mfe≥ 1的前提条件下,噪声调频信号的带宽与噪声源的带宽无关。

图6 带限高斯噪声源

图7 不同调频斜率下的干扰信号

图8 不同噪声源带宽下的干扰信号

后续经过混频器、滤波器与放大器,将带宽可控的低中频信号变频、放大至所需频点与功率,即可得到最终可用的宽带调频噪声干扰信号。

4 结论

以FPGA与DDS专用芯片为核心,完成了可编程宽带干扰源的设计。用MATLAB软件对噪声调频干扰信号的实现过程进行了仿真与分析,验证了方案的可行性。该方案性能好,灵活性强,集成度高,运行速度快,能够较好的满足多种干扰任务需求。