基于55 nm CMOS工艺的可变增益放大器

2020-07-04安文星佟玲刘亚轩张娜

安文星 佟玲 刘亚轩 张娜

摘 要:为了实现5G通信系统中高数据传输速率的要求,满足宽带条件下接收信号幅度的大动态范围变化,基于Global Foundries 55 nm CMOS工艺提出一种宽带且增益大范围线性变化的可变增益放大器. 在该可变增益放大器中,采用改进型Cherry-Hooper放大器结构使其动态范围和电路带宽有效扩展,并利用晶体管的可调谐特性,在不使用附加电路的前提下使增益变化具有良好线性,解决了CMOS电路中放大器增益与控制电压非线性变化的难题,同时添加低截止频率的高通滤波器,消除可变增益放大器的直流偏移,并降低其误码率. 版图仿真结果表明,在-33.4~46.9 dB的超宽动态范围内实现增益线性变化,3-dB带宽对应的频率达到1.89 GHz(0.000 12~1.9 GHz),可变增益放大器芯片(核心区域,不含焊盘)面积仅为0.006 mm2. 该可变增益放大器指标完全满足目前5G宽带通信系统的要求.

关键词:放大器;互补金属氧化物半导体;宽带;增益控制

Abstract:To achieve the demanding of high data transmission and meet large dynamic range under wideband conditions, a wide-band and high dynamic range variable gain amplifier with dB-linear characteristic based on the Global Foundries 55 nm CMOS process is presented. In this variable gain amplifier, a modified Cherry-Hooper amplifier gain cell is adopted to expand the dynamic range and the bandwidth of circuit, and the tunable characteristics of the transistor are used to make the dynamic range more linear and solve the problem that the amplifier's gain variation is nonlinear with the control voltage in the CMOS circuit without any additional exponential circuit. Meanwhile, a high-pass filter with a low cut-off frequency is added to eliminate the DC offset of the variable gain amplifier and reduce its bit error rate. The layout simulation results show that the variable gain amplifier achieves a ultra gain range of -33.4~46.9 dB with dB-linear characteristic, the 3-dB bandwidth is 1.89 GHz which is from 0.000 12 to 1.9 GHz, and the area of the variable gain amplifier chip(core area, excluding PAD) is only 0.006 mm2. All indicators in variable gain amplifier are suitable for the 5G wide-band wireless communication system totally.

Key words:amplifier;Complementary Metal Oxide Semiconductor(CMOS);wideband;gain control

近年来,5G通信对数据传输速率的高要求,使得无线通信系统的信道带宽成为研究的重要指标,而可变增益放大器(Variable Gain Amplifier,VGA)作为影响收发机芯片信道带宽的重要模块,其带宽特性直接影响数据传输的快慢. 在接收机中,VGA能对不同幅度的输入信号产生不同的增益,从而增大接收机的动态范围[1-2],为了满足5G通信的数据吞吐量,应用于5G中VGA的3-dB带宽必须在吉赫兹以上[3]. 为了保证通信系统拥有稳定的建立时间,VGA必须具有增益线性变化特性. 因此,具有增益线性变化特性的宽带VGA得到了广泛研究.

VGA主要分为开环与闭环两种,由于难以实现高增益、宽带宽的运算放大器,闭环VGA的带宽往往受到极大限制,仅为几十兆赫兹[4]. 现有的基于锗硅双极型互补金属氧化物半导体(SiGe Bipolar Complementary Metal Oxide Semiconductor,SiGe BiCMOS)工艺和互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺的宽带中频或基带VGA多为开环结构[5-10],按控制方式又可分为数字控制与模拟控制两种. 在具有精确增益线性特性的宽带VGA中,数字控制的VGA占主导地位[11-12],但其增益变化为离散型,严重限制了其应用领域;模拟控制的VGA增益虽然能够连续变化,但需要几级低增益、宽带宽的可变增益单元级联,这就会带来功耗、成本增加、整体VGA线性度下降等问题. 例如文献[7]中提出的采用65 nm CMOS工藝实现的一种模拟电流控制的VGA,带宽达到4 GHz,但其功耗超过25 mW,功耗过高,不利于系统集成,在应用上具有一定局限性. 在利于系统集成的CMOS工艺中,实现增益线性变化具有挑战性,文献[9]虽然在低功耗下实现了宽带特性,但增益变化为非线性,不适用于需要稳定建立时间的系统中.

本文采用55 nm CMOS工艺实现了一种模拟电压控制,增益具有线性的宽带可变增益放大器. 在不显著增加功耗的基础上,实现了对数增益随控制电压连续、线性、大范围的变化,且3-dB带宽对应的频率达到1.89 GHz.

1 电路设计

1.1 可变增益单元的设计

考虑到接收机一定的动态范围和带宽需求,本设计采用一种改进型的Cherry-Hooper放大器,这种带有反馈结构的电路可以通过将输出极点移向更高的频率来扩大增益带宽,并且不会使增益显著降低.

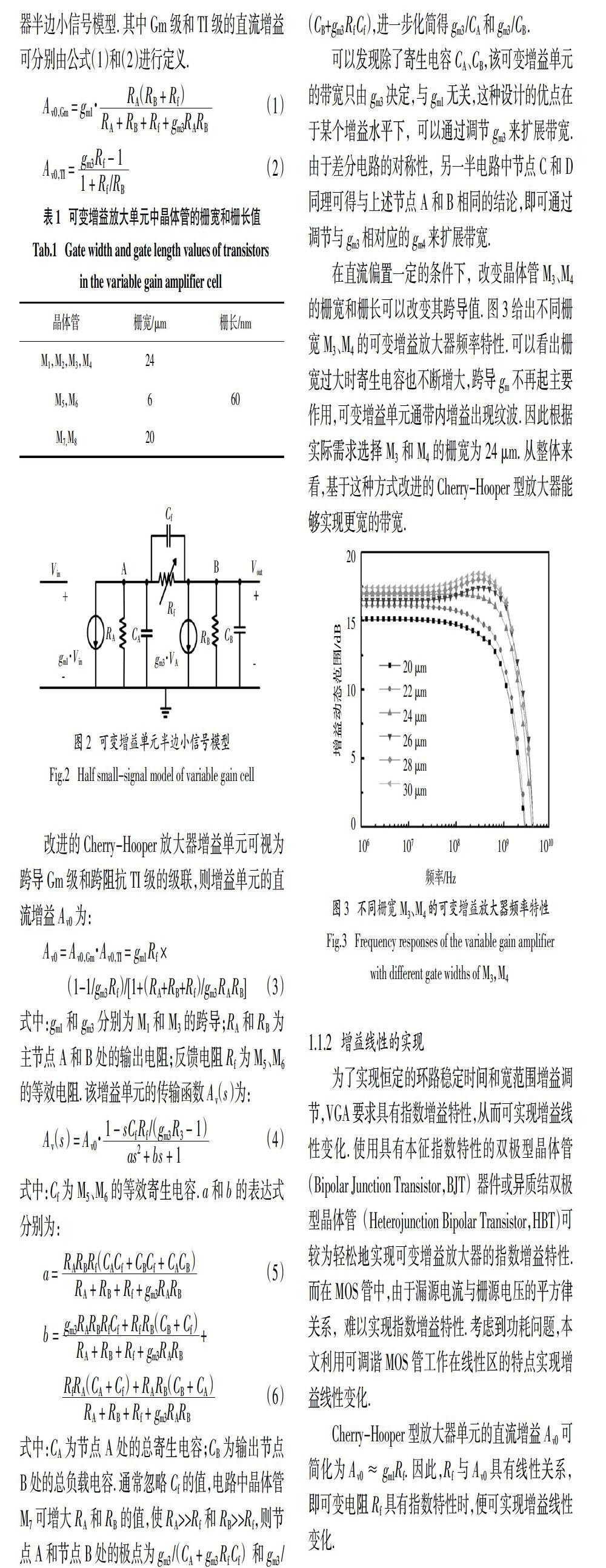

传统的Cherry-Hooper型放大器如图1(a)所示,这种结构有两点不足之处:首先,为使所有晶体管在饱和区域工作,大偏置电压会造成高功耗;其次,RD限制了放大器的最小增益,也就限制了放大器的可调谐范围. 因此,本文对传统的Cherry-Hooper放大器进行了改进,使其在不增加功耗的情况下,具有更宽的增益调谐范围,如图1(b)所示. 其中可用工作在三极管区的PMOS管M5、M6来代替反馈电阻Rf,Cf为M5、M6的等效寄生电容. 利用施加在M5、M6栅极上电压VC的变化来实现可调电阻的功能[13]. 所有CMOS晶体管都采用低阈值电压模型来缓解功耗问题. 外接控制电压的PMOS晶体管M7、M8分别与R3、R4并联,以降低最小增益,从而增加整体增益调谐范围. 此外,NMOS管M1、M2分别由偏置电阻R1、R2提供直流电流. 最终优化得到的各晶体管的参数如表1所示.

1.1.1 宽带的实现

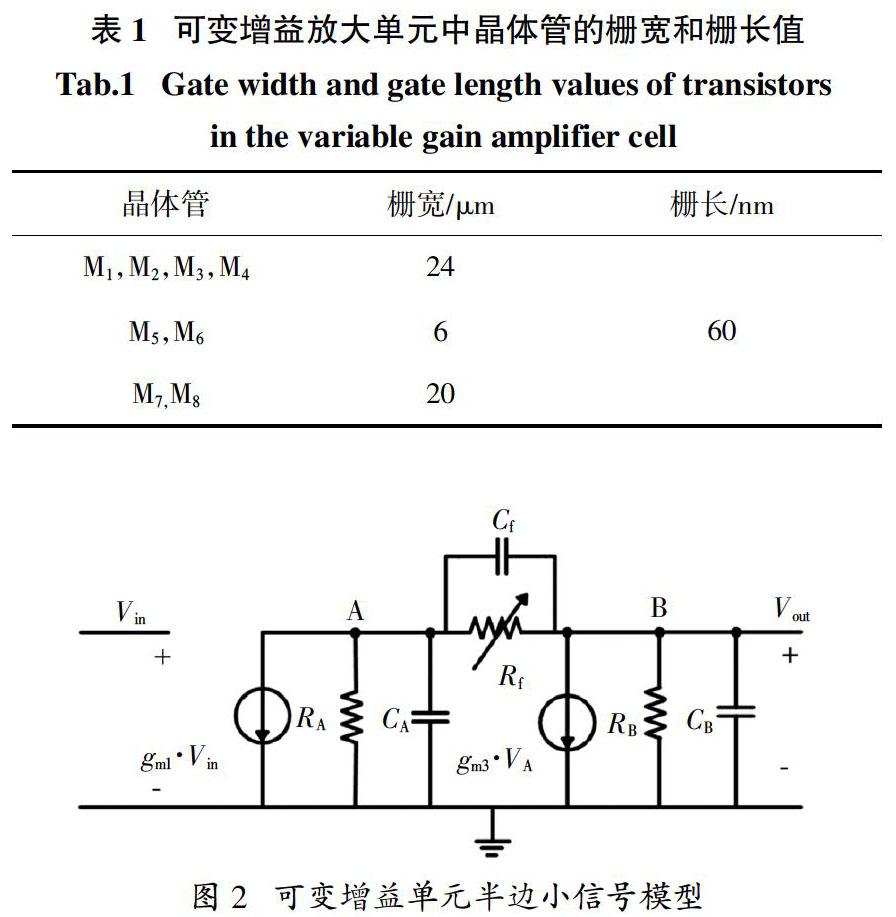

为减小分析复杂度,图2给出了可变增益放大器半边小信号模型. 其中Gm级和TI级的直流增益可分别由公式(1)和(2)进行定义.

可以发现除了寄生电容CA、CB,该可变增益单元的带宽只由gm3决定,与gm1无关,这种设计的优点在于某个增益水平下,可以通过调节gm3来扩展带宽. 由于差分电路的对称性,另一半电路中节点C和D同理可得与上述节点A和B相同的结论,即可通过调节与gm3相对应的gm4来扩展带宽.

在直流偏置一定的条件下,改变晶体管M3、M4的栅宽和栅长可以改变其跨导值. 图3给出不同栅宽M3、M4的可变增益放大器频率特性. 可以看出栅宽过大时寄生电容也不断增大,跨导gm不再起主要作用,可变增益单元通带内增益出现纹波. 因此根据实际需求选择M3和M4的栅宽为24 μm. 从整体来看,基于这种方式改进的Cherry-Hooper型放大器能够实现更宽的带宽.

1.1.2 增益线性的实现

为了实现恒定的环路稳定时间和宽范围增益调节,VGA要求具有指数增益特性,从而可实现增益线性变化. 使用具有本征指数特性的双极型晶体管(Bipolar Junction Transistor,BJT)器件或异质结双极型晶体管(Heterojunction Bipolar Transistor,HBT)可较为轻松地实现可变增益放大器的指数增益特性. 而在MOS管中,由于漏源电流与栅源电压的平方律关系,难以实现指数增益特性. 考虑到功耗问题,本文利用可调谐MOS管工作在线性区的特点实现增益线性变化.

Cherry-Hooper型放大器单元的直流增益Av0可简化为Av0 ≈ gm1Rf. 因此,Rf与Av0具有线性关系,即可变电阻Rf具有指数特性时,便可实现增益线性变化.

如图1(b)所示,在改进型Cherry-Hooper放大器电路中,Rf是由可调谐PMOS管M5、M6实现的,当PMOS管工作在线性区时,可以得到表达式(7),其中VC和VS分别为栅极电压和源极电压.

显然,K1和K2是常数,Rf相对于栅极电压VC成增益线性的关系,即增益Av0与栅极电压VC成增益线性关系.

通过以上推导可以得出,只要调节作为可调电阻Rf的可调谐PMOS管的参数和工作区,就能使电路的对数增益随着控制电压VC呈线性变化.

1.2 整体VGA系统与其他关键模块的设计

1.2.1 整体VGA架构

图4为本文提出的VGA系统框图. 本文采用的VGA系统为级联结构,能提供足够的增益来放大接收到的较弱信号. 设每个可变增益单元的3-dB带宽为BC,增益为AC,级联系统的3-dB带宽为Btot,增益为Atot,则有关系式(10)和(11),其中n代表级联的个数. 为达到高速通信的目的,整体VGA需满足带宽大于1 GHz的设计目标,因此在权衡n与总噪声系数之间的矛盾之后,选择n = 3.

整个VGA的增益变化由控制电压VC决定,三级VGA单元由相同的改进型Cherry-Hooper放大器组成;由具有较低截止频率的高通滤波器构成的前馈电路有效消除了直流偏移. 为了在实际环境中匹配50 Ω的阻抗,在电路输入和输出端添加了缓冲器,能够有效地进行隔离并起到阻抗匹配的作用.

1.2.2 直流偏移消除电路

直流失调是设计高增益放大器时必须考虑的问题,即使一个很小的输入直流失调电压,经过多级放大后可能使输出饱和,导致VGA输出为恒定电平. 实际中,一般采取电容耦合或直流失调消除电路来降低直流失调电压. 其中电容耦合是在前馈路径中每级放大器之间使用大尺寸的电容和电阻,来避免损失信号通路中的低频分量,这种方式往往见于低频应用. 典型的直流失调消除电路是通过带有RC低通滤波器的单个反馈放大器提取输出直流失调电压,将其部分反馈到输入端,逐步在输入端校正直流失调电压[4,8-10],加入反饋放大器后往往会引入额外功耗,不利于整体设计.

图5为前馈直流失调消除电路,利用晶体管代替高通滤波器中的大电阻R0和大电容C0,在降低电路复杂度的同时减小了芯片面积,并使得该高通滤波器的截止频率大大降低,从而降低了该可变增益放大器的下截止频率,可以有效提升数据传输速率,降低误码率.

1.2.3 输入缓冲器与输出缓冲器

为方便在实际环境中进行测试,VGA系统在输入输出端分别使用缓冲器来获得良好的匹配,便于驱动低阻抗负载. 输入与输出缓冲器的原理图如图6所示. 输入缓冲器采用基本的共栅极放大结构[9], 其输入阻抗为R5 /(1 + gm9 R5),gm9 R5的值很小,可忽略不计;输出缓冲器采用具有共模反馈电路的射极跟随器的结构[14],其输出阻抗为Zout = (1/gm15)‖(1/gm16);M15、M16影响着VGA的输出匹配. 缓冲器电路中关键器件的参数见表2.

2 结果与分析

本文设计的VGA版图如图7所示,由于芯片设计时未使用任何电感,故芯片面积小,制作成本低. 芯片面积为0.006 mm2(芯片核心区域尺寸,不包括焊盘),直流功耗为19.68 mW. 使用仿真软件基于Global Foundries 55 nm CMOS工艺模型对该宽带VGA进行版图后仿真. 图8(a)给出了该VGA的对数增益在不同频率上的响应结果. 该放大器3-dB带宽为1.89 GHz(0.000 12~1.9 GHz),带内平坦度极佳.

该VGA的对数增益随控制电压变化结果如图8(b)所示,当控制电压VC为0~0.6 V时,电路的对数增益与控制电压VC呈现相当好的线性关系,拟合度较高,增益线性变化的动态范围为-33.4~46.9 dB,增益实现了最大范围的线性变化.

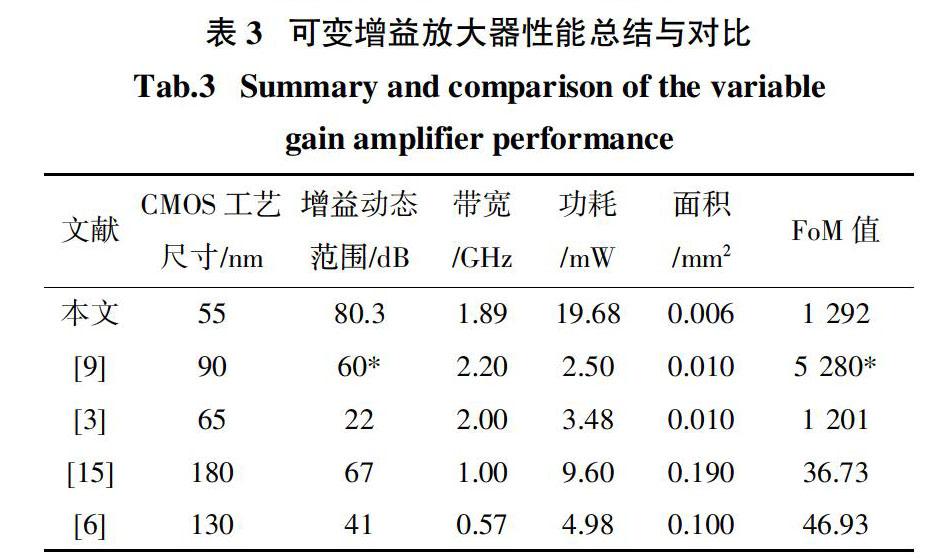

表3为本文中VGA的指标与已发表的同类采用CMOS工艺的可变增益放大器的性能比较. 本文所提出的结构实现1.89 GHz(0.000 12 ~1.9 GHz)的3-dB帶宽,并具有高达80.3 dB(-33.4~46.9 dB)的增益线性变化的增益. 通常广泛使用的综合评价VGA性能的FoM公式如(12)所示,可突出设计在带宽BW、动态范围Gain Range、功耗Power、面积Core Area等方面的优越性. 文献[9]的FoM虽高于本文中的VGA,其增益却不具备dB线性的特征,相较而言本设计可直接应用于自动增益控制系统中,在实际应用中更具有优势.

3 结 论

本文设计了一种CMOS宽带可变增益放大器,该放大器采用三级级联结构,增益单元基于改进的Cherry-Hooper放大器,可增大带宽,通过在放大管输出的漏极添加可调谐的PMOS晶体管代替反馈电阻,同时保证了更大的增益调谐范围. 此外,利用该可调谐晶体管工作在亚阈值区的特征,在整个动态变化范围内实现出色的dB线性. 最后,利用直流失调消除技术优化了电路性能. VGA的增益范围为-33.4~46.9 dB,具有精确的dB线性特性,3-dB带宽为1.89 GHz(0.000 12 ~1.9 GHz),满足了5G通信系统的要求,同时VGA电路仅占用0.006 mm2面积,1.2 V电源仅消耗16.4 mA电流,在VGA广泛适用的FoM值为1 292,高于目前同类设计,实现了芯片小尺寸和低功耗,适用于5G宽带通信系统中.

参考文献

[1] WANG B D,GAO H,RAINIER V D,et al. 60-GHz low-noise VGA and interpolation-based gain cell in a 40-nm CMOS technology[J]. IEEE Transactions on Microwave Theory and Techniques,2019,67(2):518—532.

[2] KODAK U,GABRIEL M R. A 5G 28-GHz commonleg T/R front-end in 45-nm CMOS SOI with 3.7-dB NF and -30-dBc EVM with 64-QAM/500-MBaud modulation[J]. IEEE Transactions on Microwave Theory and Techniques,2019,67(1):318—331.

[3] LIU H,BOON C C,HE X F,et al. A wideband analog-controlled variable-gain amplifier with dB-linear characteristic for high-frequency applications[J]. IEEE Transactions on Microwave Theory and Techniques,2016,64(12):1363—1373.

[4] HASSAN E,AHMET T,KENNETH P. A differential-ramp based 65 dB-linear VGA technique in 65 nm CMOS[J]. IEEE Journal of Solid-State Circuits,2009,44(9):2503—2514.

[5] BAI C F,WU J H,CHEN C,et al. A 35-dBm OIP3 CMOS constant bandwidth PGA with extended input range and improved common-mode rejection[J]. IEEE Transactions on Circuits and Systems-II:Express Briefs,2017,64(8):922—926.

[6] SONG X,LU Z H,YU X P. An accurate dB-linear CMOS VGA based on double duplicate biasing technique[J]. IEEE Journal of Latex Class Files,2018,14(8):1—4.

[7] KUMAR T B,MA K X,YEO K S. A 4 GHz 60 dB variable gain amplifier with tunable DC offset cancellation in 65 nm CMOS[J]. IEEE Microwave and Wireless Components Letters,2015,25(1):37—39.

[8] KONG L S,CHEN Y,CHIRN C B,et al. A wideband inductorless dB-linear automatic gain control amplifier using a single-branch negative exponential generator for wireline applications[J]. IEEE Transactions on Circuits and Systems,2018,65(10):3196—3206.

[9] WANG Y J,AFSHAR B,CHENG T Y,et al. A 2.5 mW inductorless wideband VGA with dual feedback DC-offset correction in 90 nm CMOS technology [C] // Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium. Atlanta,Georgia :IEEE,2008:91—94.

[10] KUMAR T B,MA K X,YEO K S. Temperature-compensated dB-linear digitally controlled variable gain amplifier with dc offset cancellation[J]. IEEE Transactions on Microwave Theory and Techniques,2013,61(7):2648—2661.

[11] SAWSSEN L,SAMIR B S,MOURAD L. Low power CMOS digital variable gain amplifier design for WiMAX/LTE receiver[C] // Proceedings of the 2018 30th International Conference on Microelectronics. Sousse,Tunisia:IEEE,2018:204—207.

[12] LI Q Q,MA S L,YE F,et al. A low power PGA with DC-offset cancellation in 65 nm CMOS process[C] // Proceedings of the 13th IEEE International Conference on Solid-State and Integrated Circuit Technology. Hangzhou:IEEE,2016:946—948.

[13] 曾健平,樊明,陳铖颖,等. 应用于眼压信号检测的低噪声前置放大器[J]. 湖南大学学报(自然科学版),2017,44(8):113—116.

ZENG J P,FAN M,CHEN C Y,et al. Design of low-noise preamplifier for application of intraocular pressure signal-detection[J]. Journal of Hunan University(Natural Sciences),2017,44(8):113—116.(In Chinese)

[14] LIU H,ZHU X,BOON C C,et al. Cell-based variable gain amplifiers with accurate dB-linear characteristic in 0.18 μm CMOS technology[J]. IEEE Journal of Solid-State Circuits,2015,50(2):586—596.

[15] LI J,HUANG F Y,HU X R,et al. A 1 GHz 68 dB CMOS variable gain amplifier with an exponential-function circuit [C] // Proceedings of International Symposium on Signals,Systems and Electronics. Iasi,Romania :IEEE,2010:17—20.