一种具有高稳定相位差的成像雷达频率源

2020-06-16张凤萍章撼中

张凤萍, 梁 影,2, 章撼中, 倪 亮,2

(1.上海无线电设备研究所,上海201109;2.上海目标识别与环境感知工程技术研究中心,上海201109)

0 引言

频率源,又称频率合成器,是雷达和通信系统的核心器件之一,对雷达和通信系统的性能起决定性作用。对于太赫兹成像雷达,为了实现对运动目标厘米级甚至毫米级分辨率的成像,要求雷达系统具有较好的相参性[1],从而对频率源的精度和稳定性提出了更高的要求。目前,对太赫兹波频率源的研究正处于探索阶段,频率源在更高频率、更低相噪、更低杂散和谐波[2]等性能上的突破,能更好地推动高分辨成像雷达技术的发展。

针对微波频率源相位抖动以及频率不稳定等因素导致高分辨成像雷达目标回波抖动、成像效果差的问题,提出了一种具有高稳定相位差的频率源实现方案,并进行系统实测,验证频率源方案的有效性。

1 频率源稳定性对运动补偿精度的影响

高分辨成像雷达作为逆合成孔径雷达(ISAR)成像技术的应用,回波数据处理过程主要包括运动补偿和成像处理两部分。目标相对于雷达的运动姿态变化会导致成像质量下降,由于运动目标的非合作性,在无法预知目标运动轨迹的前提下,高要求的目标成像分辨力很难实现。运动补偿技术[3]作为ISAR成像的一个关键技术,是进行图像处理和分析的基础。

设雷达接收机收到的回波信号为

式中:f(t)为回波复包络;ω0为载波频率。则延时τ的回波信号可表示为

运动补偿过程中对相邻时刻回波进行包络对齐时,充分利用了相邻时刻两次回波之间的强相关性,进行距离像平移处理,并以幅度相关函数R(τ)的最大值所在位置τ0作为运动补偿时间的估计值[4]。幅度相关函数R(τ)的表达式为

运动补偿的包络对齐要求回波之间具有相关性,频率源产生的脉冲调频信号间的初始相位误差以及频率误差越小越好。若频率源使用的系统时钟不稳定,产生的脉冲信号的初始相位会有较大的抖动,相邻多次回波间的强相关性不成立,从而引入包络对齐误差。

同样的,采用运动补偿技术进行初相校准时,需要在目标散射点中寻找一个参考点,如散射中心[5],作为基准完成初相校准。或者根据最大似然估计原理[6],通过回波脉冲间的相位关系,估计目标运动参数,完成初相校准。频率源引入的初相抖动,会增加参考点的选取难度。回波脉冲间的相位关系不稳定,会导致初相校准不准确,合成后的目标像将出现主瓣展宽和副瓣变差的情况,无法满足高分辨雷达成像的精度要求。

2 频率源相位差稳定性的要求

高分辨成像雷达要求成像分辨率达厘米级甚至毫米级。在包络对齐误差无法通过指数加权、卡尔曼滤波、最大熵等滤波算法处理达到分辨率精度要求时,需要对频率源的稳定性提出更高的要求。

完成运动补偿后,即可对回波数据进行成像处理。常用的成像算法有距离-多普勒成像法[7]、超分辨ISAR成像算法、幅度和相位压缩法以及ISAR图像重建算法等。这些成像算法都有一个共同的特点,即成像结果的好坏与频率源的相位特性具有较大的相关性。一发三收脉冲调频ISAR成像雷达,在完成回波的去斜或解调时,需要在接收机中对回波信号与本振信号进行差频处理。差频处理时频率源相位差会对去斜结果引入相位残差项,从而降低雷达成像分辨率[8]。

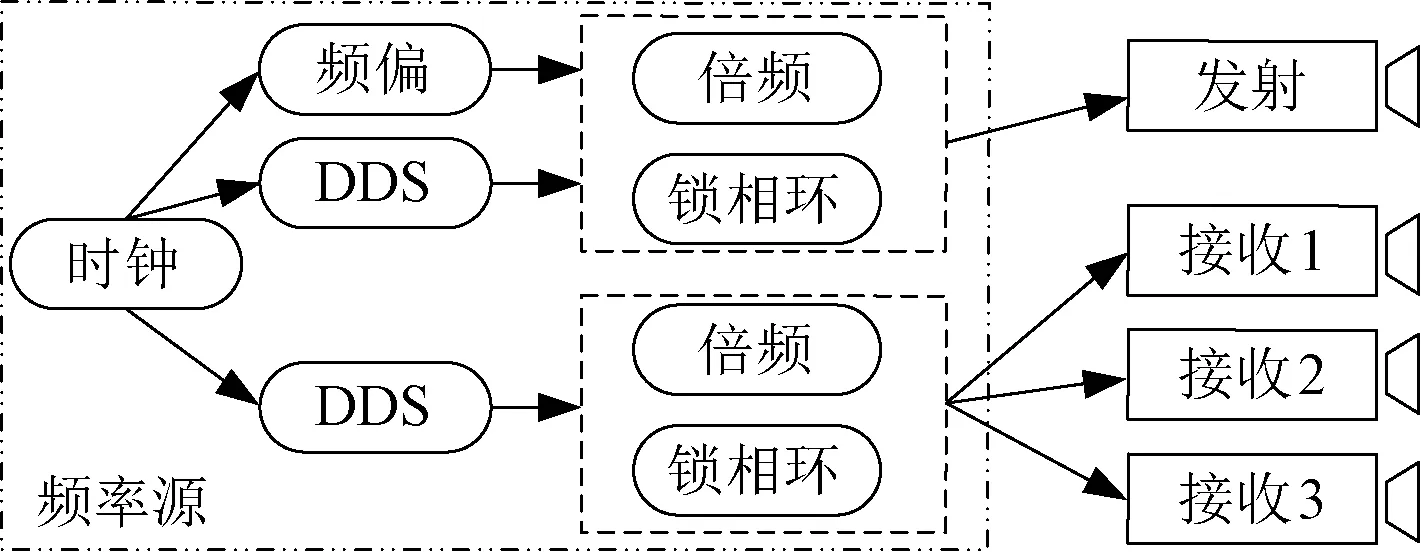

雷达发射和接收倍频链路原理框图如图1所示。接收与发射频率源信号由两片DDS芯片分别产生,经相同的多级锁相倍频,得到太赫兹波段频率源信号输出。发射频率源相对于接收频率源有一个固定频偏,该频偏产生时钟与DDS芯片时钟同源。在保证多级倍频链路本身不产生相位噪声的前提下,DDS芯片输出信号的相位噪声会在倍频链路中逐级放大。如果两路DDS芯片产生的脉冲信号的脉间初始相位差不稳定,会在回波去斜处理过程中引入误差,造成回波中心频率的偏移,产生距离估计误差。为满足去斜混频接收的要求,收发两路DDS电路需要进行同步处理,同一脉冲的两路输出信号同步误差不得超过1 ns;在工作频率为600 MHz时,DDS输出重复脉冲间的相位差应不大于2°。

图1 雷达发射和接收倍频链路原理框图

3 频率源设计

3.1 频率源方案

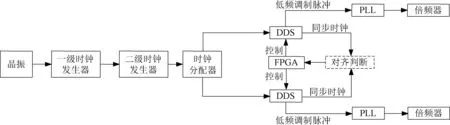

设计频率源时,充分考虑系统相参性要求,各电路模块均采用同一参考时钟。参考电子科技大学[9]基于DDS和锁相环(PLL)的频率源设计方案,将单路的DDS锁相倍频[10]链路扩展成双路固定频率差频率源产生链路(双路DDS+PLL频率源),如图2所示。现场可编程门阵列(FPGA)通过串行外设接口(SPI)与DDS芯片通信,完成DDS信号产生控制;DDS芯片的时钟输入信号与混频输入信号均由同一晶振锁相倍频产生;DDS产生的信号经过二倍频器后,在PLL中与具有固定频率偏差的两路X波段频率源信号进行混频;然后经N倍频得到太赫兹频段信号。

图2 双路DDS+PLL频率源原理框图

FPGA控制DDS信号输出时,需要对DDS芯片内部控制寄存器进行多次刷新,启动DDS芯片内部时钟校准电路,完成多芯片间的系统时钟同步校准,产生两路同步的线性调频脉冲信号。低频信号由两片AD9914芯片产生,充分利用其同步校准功能,分别从硬件和软件上进行初始相位校准设计,保证频率源的频率精度与相位精度。考虑到两片DDS芯片之间的同步性要求,采用2.4 GHz高频时钟信号作为DDS芯片系统时钟。2.4 GHz高频时钟由50 MHz时钟通过两级高精度晶体振荡器级联产生,以保证最后一级振荡器输出信号的相位稳定度足够高。对于2.5 GHz载波,压控振荡器(VCO)相位噪声为-137 dBc/Hz@1 MHz,满足时钟稳定性要求。

3.2 频率源相位差稳定性的改进

双DDS频率源产生的脉冲调频信号的相位噪声与杂散指标能够满足高分辨成像雷达分辨率要求。但是由于两路DDS电路输出信号的初始相位存在波动,会导致雷达测距平均值出现较大偏差。为了解决上述问题,对雷达测距误差产生的原因进行了分析,并改进信号处理流程。

在双DDS频率源信号产生电路中,采用两级时钟发生电路产生频率高达2.4 GHz的同源时钟分别给两片DDS芯片。由于输入时钟频率较高,导致双DDS的低频调制脉冲的脉间相位同步比较困难,同步误差将影响ISAR成像雷达的成像分辨率和测距精度。

为了提高双DDS的输出脉冲相位差稳定性,对DDS芯片输出的100 MHz同步时钟进行前沿对齐监控,结果反馈给FPGA控制软件,对DDS芯片进行多次同步校准,直至同步误差满足系统要求。改进后的电路功能框图如图3所示。

图3 双路DDS频率源的同步改进示意图

4 测试验证

4.1 同步时延测试

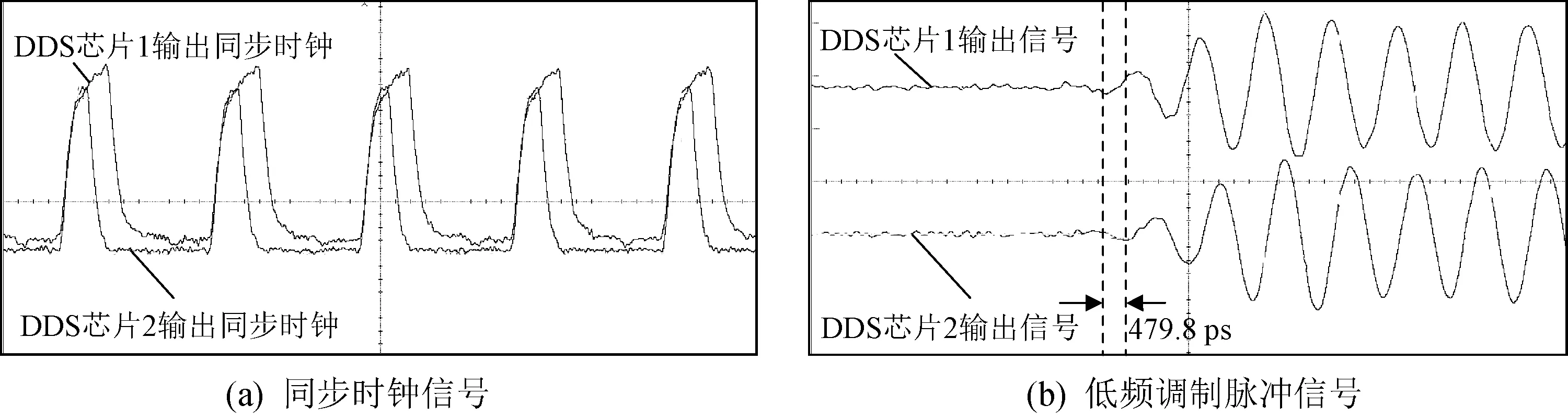

对DDS系统时钟同步时延进行测试,采取时钟上升沿对齐措施前后的两路DDS时钟信号输出波形分别如图4和图5所示。未采取时钟对齐措施时,两路DDS输出同步时钟上升沿明显未对齐,低频调制脉冲输出相对延时1.366 7 ns,不满足高分辨成像雷达测距要求;采取时钟对齐措施后,两路DDS输出同步时钟上升沿对齐,低频调制脉冲输出相对延时479.8 ps,满足高分辨成像雷达测距要求。

图4 采取时钟对齐措施前的DDS输出情况

图5 采取时钟对齐措施后DDS输出情况

4.2 相位差测试

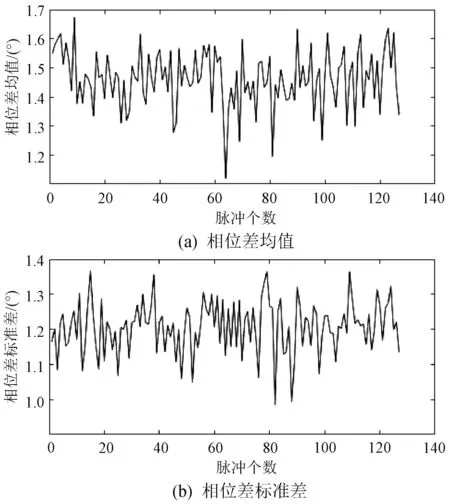

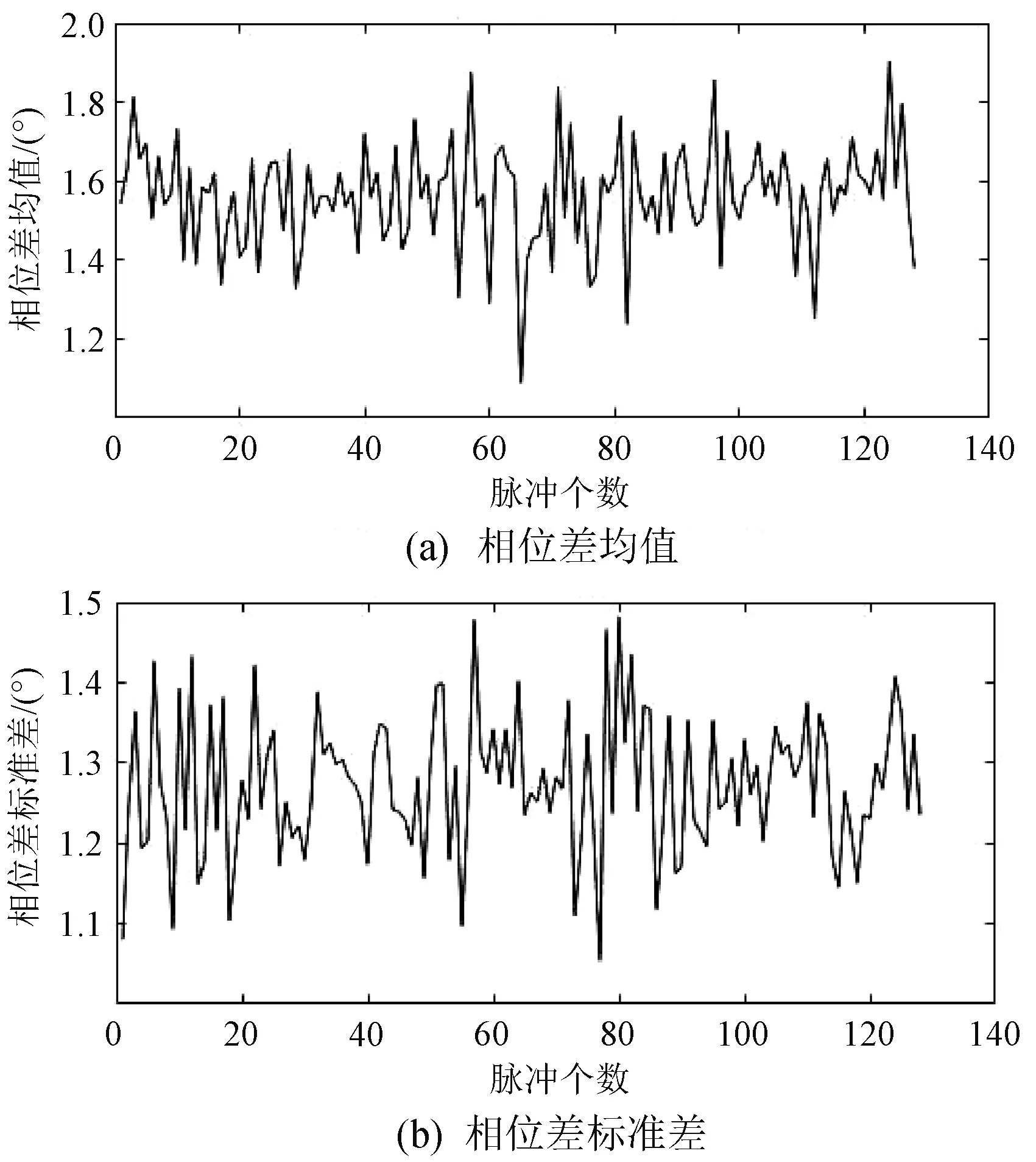

分别对采取时钟上升沿对齐措施后的两路DDS输出的连续128个脉冲进行采集和存储,根据信号幅度值计算相位值。以第1个脉冲数据为参考,分别计算两路DDS输出的后127个脉冲数据相对于第1个脉冲数据的相位差,得到两组127×16 000点相位差数据,其中16 000为每个脉冲内的采样点数。以通道1为参考,求解通道2相对于通道1的相位差,得到一组128×16 000点相位差数据。对相位差求均值和标准差,如图6~图8所示。通道1的各脉冲间的相位差均值在-0.100 5°±0.228 6°范围内,标准差在1.062 7°±0.172 5°范围内。通道2的各脉冲间相位差均值在1.461 7°±0.278 8°范围内,标准差在1.206 9°±0.191 3°范围内。通道2相对于通道1的相位差均值在1.562 0°±0.408 0°范围内,标准差在1.273 5°±0.214 1°范围内。可以看出:通道1的相位差均值和标准差均小于通道2,分别为0.1°和1.06°;两个通道内以及两个通道间的相位差均值均保持在2°以内,满足雷达系统分辨精度要求。

图6 通道1脉间相位差统计

图7 通道2脉间相位差统计

图8 通道2相对于通道1相位差统计

5 结论

本文分析了频率源相位差稳定性对高分辨成像雷达运动补偿精度的影响,给出了雷达成像分辨率对频率源相位差的要求,提出了一种双DDS频率源产生方案。针对双DDS频率源同步时钟前沿未严格对齐,引起回波中心频率偏移的问题,提出了DDS同步时钟实时监控的改进措施。通过多次DDS芯片时钟的同步校准,实现了具有高稳定相位差的双路脉冲调制频率源。测试结果表明,该双路DDS频率源输出同步延时时间在500 ps以内,通道内及通道间的脉间相位差均值均稳定在2°以内,相位差标准差不大于1.5°,能够满足高分辨成像雷达对频率源稳定性的要求。