一种SoC 芯片中PCIe 接口的FPGA 平台验证

2020-05-20黎小玉牛少平

刘 娟,田 泽,2,黎小玉,2,牛少平

(1.中航工业西安航空计算技术研究所,西安 710068;2.集成电路与微系统设计航空科技重点实验室,西安 710068)

0 引言

随着嵌入式系统互连技术的发展,系统对数据传输和处理的速率也有了越来越来高的要求,I/O 子系统的性能直接关系到系统的性能[1],PCI Express(PCIe)是继第一代ISA、EISA、VESA 总线,第二代PCI、AGP、PCI-X 总线之后的第三代高性能I/O 总线,是一种能够广泛应用于移动设备、计算系统、嵌入式计算和通信平台等所有周边I/O 设备互连的总线[2-3]。

由于PCIe 在嵌入式系统的广泛应用,使得在愈来愈复杂的SoC 设计中如何对PCIe 接口尽早的进行充分且完备的验证,是值得研究的重要问题之一,本文基于一款自研SoC 芯片PCIe 接口,详细阐述PCIe 接口的FPGA 平台验证。

2 SoC 芯片PCIe 接口模块功能

本文中SoC 芯片的PCIe 模块符合PCI Express v2.0协议,并兼容PCI Express v1.1协议,支持x4 PCI Express通道,单通道2.5Gb/s 通道速率,实现了协议规定的事务层、链路层、物理层逻辑子块的功能,支持端点操作,提供传统中断和MSI 中断两种中断类型,PCIe 模块为用户提供全面的底层PCIe 状态信息,主机通过PCIe 接口可访问的地址空间分为3部分,可分别配置基地址寄存器BAR1、BAR2、BAR3的值来确定其基地址,BAR0空间保留。BAR1为寄存器区,BAR2为存储区,BAR3为FLASH。

3 FPGA 验证环境搭建

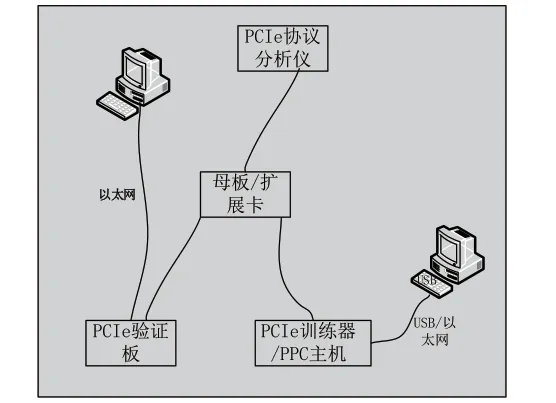

在PCIe 接口的FPGA 原型验证中,需要综合考虑平台的可靠性、完备性以及可测试性,文中采用的验证环境示意图如图1所示:验证环境使用的硬件和软件如下:

硬件组成:PC 机,Xilinx 编程调试电缆,RiscWatch 调试工具,PCIe 验证板,PPC 主机板、PCIe 训练器,母板/扩展卡;

软件环境:ELDK,Tornado2.2,Protocol Exerciser 工具。

图1 验证环境

4 FPGA 验证

对PCIe 接口进行充分完备的FPGA 验证,可以有效的弥补软件模拟仿真的不足,检验设计是否符合SoC 设计需求,尽早的暴露设计中存在的问题[4]。本文中通过协议分析,根据SoC 芯片的PCIe 接口需求以及功能定义,策划了符合性验证,功能验证、性能验证三大类验证项,以保证功能、性能、对外接口以及兼容性满足应用要求。以下分别介绍。

4.1 协议符合性测试

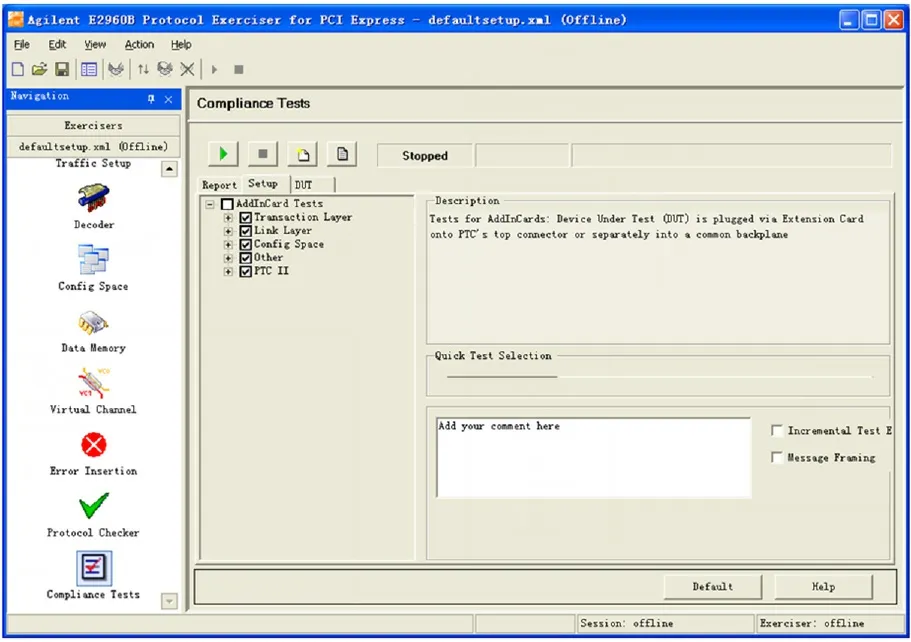

协议的符合性测试是一种功能性的黑盒测试[5],由于PCI Express 协议的复杂性,使符合性测试较困难;另外,在验证中需要考虑提高验证效率,因此,在文中采用安捷伦PCIe 训练器,通过训练器自带的Protocol Exerciser软件来进行协议符合性测试。测试软件如图2所示,协议符合性测试包括以下两项:

(1)PCI-SIG 要求的13个强制测试项目,主要包括对未定义编码的DLLP 是否会被丢弃、对错误LCRC 的丢弃处理以及错误序列号的TLP 是否丢弃等,训练器在测试完成后会自动生成测试报告。

(2)对传输层、数据链路层、配置空间的测试项目,包括传输层70项,数据链路层40项,配置空间66项,电测试1项,可根据训练器软件中对每个测试项的执行提示完成测试项的执行并自动生成测试报告。

图2 协议符合性测试软件

4.2 功能验证

PCIe 接口的功能验证主要包括PCIe 配置空间功能,BAR1寄存器区功能,BAR2存储区功能、BAR3 Flash 功能,PCIe BAR间干扰以及PCIe 中断功能测试,具体如表1所示。

表1 功能验证

4.3 性能验证

根据SoC 设计需求,PCIe 性能验证包括四线转一线测试、PCIe 的读写速率测试以及PCIe 链路稳定性测试,其中PCIe 的读写速率包括单拍读写及DMA 读写。

四线转一线:由于系统上电复位后,系统自动协商为PCIe四线,配置PPC 主机的SRDS1CR1寄存器,将PCIe 链路强制为一线,在PCIe 初始化和配置完成后访问Bar1和Bar2,判断读写是否正常。

PCIe 的单拍读写速率:使用PPC 主机上的定时器进行定时,对BAR1空间进行多次读写数据,计算BAR1的单拍读写速率。

DMA读写速率:DMA读写速率测试需分别测试PCIe在一线、四线时,PCIe 包分别配置为128B、256B、512B 的最大读请求长度和128B、256B 的写请求长度的场景下,使用PPC 主机上的定时器,在PPC主机上准备数据,配置DMA测试寄存器数据源地址、目的地址、测试长度,启动DMA,对DMA 状态查询传输是否完成,从而根据多次DMA的数据长度及定时器时间,计算DMA读速率、DMA 写速率。

PCIe 链路稳定性测试:系统上电复位后,初始化和配置PCIe,在一定的时间段内,对BAR 空间进行连续的单拍读写访问或者DMA 操作,并在数据访问期间读PCIe 链路状态寄存器,判断链路状态是否正常。

5 结束语

本文介绍了一种SoC 芯片中PCIe 接口的FPGA 平台验证,搭建验证平台,策划测试用例,进行协议符合性验证、功能验证以及性能验证,经验证,PCIe 接口符合PCIe 协议标准,功能正确,性能稳定;PCIe 读速率为487.9MB/s,PCIe 写速率为520MB/s,PCIe 接口功能及性能满足该芯片需求,对SoC 芯片的开发进度有一定的促进作用,构建的验证平台具有可重用性,对同类模块的验证有可参考性。