U型槽刻蚀工艺对GaN垂直沟槽型金属-氧化物-半导体场效应晶体管电学特性的影响*

2020-05-16陈扶唐文昕于国浩张丽徐坤张宝顺

陈扶 唐文昕 于国浩 张丽 徐坤 张宝顺‡

1) (中国科学技术大学纳米技术与纳米仿生学院, 合肥 230026)

2) (中国科学院苏州纳米技术与纳米仿生研究所, 多功能材料与轻巧系统重点实验室, 苏州 215123)

U型槽的干法刻蚀工艺是GaN垂直沟槽型金属-氧化物-半导体场效应晶体管(MOSFET)器件关键的工艺步骤, 干法刻蚀后GaN的侧壁状况直接影响GaN MOS结构中的界面态特性和器件的沟道电子输运.本文通过改变感应耦合等离子体干法刻蚀工艺中的射频功率和刻蚀掩模, 研究了GaN垂直沟槽型MOSFET电学特性的工艺依赖性.研究结果表明, 适当降低射频功率, 在保证侧壁陡直的前提下可以改善沟道电子迁移率,从35.7 cm2/(V·s)提高到48.1 cm2/(V·s), 并提高器件的工作电流.沟道处的界面态密度可以通过亚阈值摆幅提取, 射频功率在 50 W 时界面态密度降低到 1.90 × 1012 cm–2·eV–1, 比 135 W 条件下降低了一半.采用 SiO2硬刻蚀掩模代替光刻胶掩模可以提高沟槽底部的刻蚀均匀性.较薄的SiO2掩模具有更小的侧壁面积, 高能离子的反射作用更弱, 过刻蚀现象明显改善, 制备出的GaN垂直沟槽型MOSFET沟道场效应迁移率更高, 界面态密度更低.

1 引 言

随着对功率开关器件需求的不断增加, 硅基电力电子器件逐渐达到了硅材料的极限[1], 对整个电力电子器件的革新开始变缓.以GaN为代表的第三代宽禁带半导体材料凭借其禁带宽度大、击穿场强高和饱和电子速率高等优势, 有望在高压高功率领域得到广泛应用[2−5].AlGaN和GaN材料组成的异质结由于极化效应会在界面处自发形成高浓度、高迁移率的二维电子气[6], 因此GaN功率器件大多是横向结构[7−9].然而, 横向结构的主要缺点在于为了进一步提高功率器件的击穿电压, 就需要不断提高栅漏间距[10,11], 因此导致了高耐压下器件所占面积更大, 不符合小型化的发展趋势.此外,横向器件由于表面存在陷阱态和高电场区, 还存在电流崩塌等可靠性问题[12,13].GaN单晶生长技术和自支撑衬底的发展促使了GaN基垂直型功率器件的研究.相比于水平器件, 垂直器件的高电场区域远离表面, 且器件的耐压取决于漂移层厚度, 无需横向增加器件尺寸就可以实现高击穿电压[14].截至目前GaN垂直器件的典型结构包括电流孔径垂直电子晶体管(CAVETs)[15,16]、结场效应晶体管[17]、垂直沟槽型金属-氧化物-半导体场效应晶体管(UMOSFETs)[18,19]和鳍式功率场效晶体管[20,21],其中UMOSFET通过使呈U型的沟槽侧壁处p-GaN层产生反型, 可以实现阈值电压大于3 V的增强型器件, 目前对于该器件电学特性的工艺依赖性研究较少, 尤其是对于U型槽刻蚀的关键工艺.本文改变干法刻蚀中的射频(RF)功率和刻蚀掩模, 对比分析不同刻蚀条件下的GaN UMOSFET器件性能, 提取出相应界面态密度和沟道迁移率,进一步优化了U型槽的工艺条件.

2 器件结构与制备

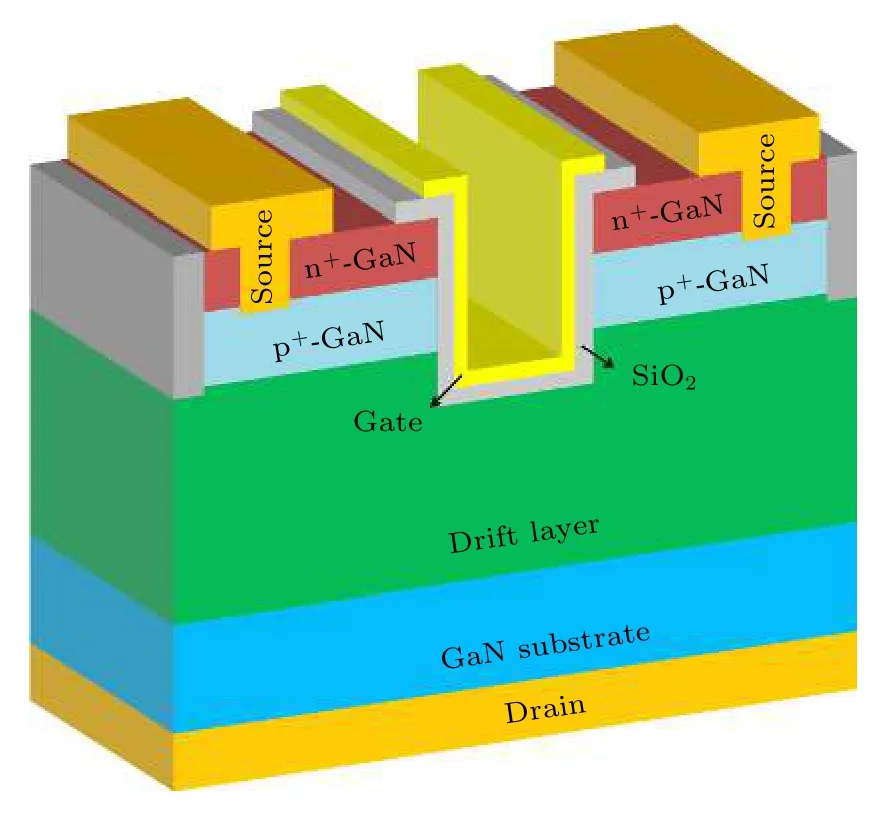

图1为GaN垂直型UMOSFET器件的结构图, 本文中所使用的结构是基于GaN同质衬底通过金属有机化合物化学气相沉积(MOCVD)自下而上依次外延得到, 其中三甲基镓(TMG)和氨气(NH3)分别作为Ga源和N源, H2为载气, 以硅烷和二茂镁分别作为n+-GaN和p+-GaN的掺杂源.首先在衬底上生长4 µm厚的低掺杂n-GaN漂移层 (掺杂浓度为 1.85 × 1016cm–3), 再往上外延500 nm 的 p+-GaN (Mg 掺杂浓度为 3 × 1019cm–3)作为沟道层, 最后外延200 nm的n+-GaN源区层(Si掺杂浓度为 4 × 1018cm–3).

对于GaN UMOSFET器件的制备, 首先制备U型槽结构, 刻蚀工艺采用感应耦合等离子体(ICP)刻蚀技术, Cl2/BCl3/Ar 作为刻蚀气体, 刻蚀深度约800 nm, 本工艺将在第3部分详细介绍,p-GaN沟道层通孔刻蚀也采用相同的刻蚀条件进行.为防止干法刻蚀对p-GaN的补偿作用, 将样品重新置于 MOCVD 腔室内进行 850 ℃, 30 min 的氮气氛围退火, 重新激活p-GaN沟道层.器件隔离通过F离子注入实现, 注入能量和剂量分别为:80 keV/1.2 × 1014cm–2, 140 keV/2 × 1014cm–2,240 keV/4 × 1014cm–2.采用等离子体增强化学气相沉积(PECVD)生长约80 nm的SiO2作为栅介质.最后蒸发 Ti/Al/Ni/Au (20/130/50/150 nm)四层金属作为源极和漏极, 磁控溅射Ti/Au作为栅极金属.器件结构呈正六边形形貌, 且侧壁沿GaN的m面, 六边形的边长约77 µm.

图1 GaN 垂直型 UMOSFET 器件示意图Fig.1.Cross-sectional schematic of a vertical GaN UMOSFET.

3 结果与讨论

GaN UMOSFET 在开态下, p-GaN表面的反型层沟道提供了源极到漏极的导电通道.关态下整个器件可等效为反偏PN结, 电压主要由厚的轻掺杂一侧的N型漂移区来承担.由GaN UMOSFET的工作原理可知, 关键的工艺步骤是U型槽的干法刻蚀工艺, 因此, 我们对ICP干法刻蚀中的RF功率和刻蚀掩模进行了调节, 研究两者对器件特性的影响, 表1为不同样品对应的干法刻蚀条件参数.

ICP干法刻蚀是利用射频电源产生的等离子体对样品进行化学反应与物理刻蚀.虽然高的离子能量更有利于获得陡直的U型槽形貌, 但是高能物理轰击也会带来不可逆转的干法刻蚀损伤, 对GaN UMOSFET沟道处的界面态密度造成不利影响[22].射频偏压功率源主要是控制离子轰击能量,因此很大程度上也决定了干法刻蚀的损伤情况, 三个样品对应A, B和C三个刻蚀条件, RF功率从135 W调节到50 W以对应不同离子轰击能量的情况, 探究对器件特性的影响.

表1 干法刻蚀条件参数 (1 Torr = 1.33322 × 102 Pa)Table 1.Experiment parameters of the dry etching process.

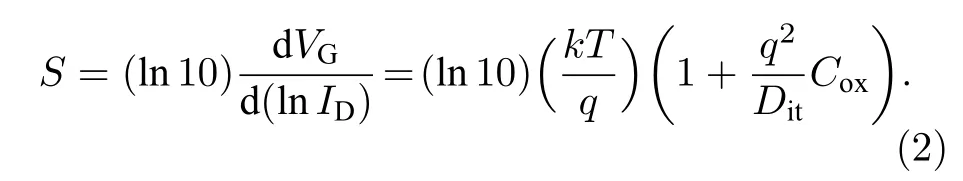

图2(a)给出了分别采用 RF功率为 50, 75和135 W三种干法刻蚀条件所制备出的GaN UMOSFET的转移特性曲线, 转移测试过程漏极偏压固定为1 V.从半对数坐标下的转移特性曲线可以看出, 三个样品的阈值电压(定义为源漏电流达到1 A/cm2)随着RF功率的增加而逐渐负偏,分别为 3.4, 2.7 和 1.2 V.且在线性坐标下, 施加栅压为18 V时三种器件的饱和电流也存在差异, 分别为 96.8, 91.0 和 85.6 A/cm2.

器件跨导gm与沟道迁移率µchannel的关系如下[23]:

其中, L是沟道长度, 即 p-GaN沟道层的厚度;W是栅宽; Cox是单位面积栅介质的电容; VDS是漏偏压.可以通过三种器件的跨导推算出相应的沟道迁移率, 结果如图2(b)所示, 可以看出采用RF功率为 50, 75和 135 W刻蚀条件制备出的GaN UMOSFET的沟道峰值迁移率分别为48.1,44.9 和 35.7 cm2/(V·s).大的 RF 功率对侧壁的干法刻蚀损伤更大, 导致器件沟道载流子所受散射效应增加, 沟道峰值迁移率降低[24].

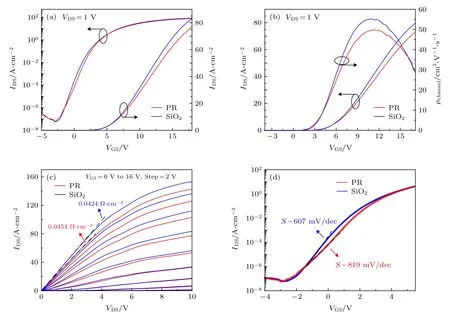

图2(c)显示的是采用三种不同RF功率制备出的GaN UMOSFET的亚阈值特性, 它可以量化MOS管随栅压快速关断的水平, 通过器件半对数坐标下的转移特性可以对亚阈值区域进行线性拟合[25], 三种器件的亚阈值摆幅S随着RF功率的提高逐渐增加, 分别是 481, 593 和 977 mV/dec,这表明采用较低RF功率条件的器件随栅压变化关断得更迅速, 开关特性更优.亚阈值摆幅S与界面态密度Dit的关系式为

图2 干法刻蚀RF功率为50, 75和135 W制备出GaN UMOSFET器件的电学特性曲线(IGS和IDS分别指栅电流和漏电流)(a)转移特性曲线; (b)沟道场效应迁移率随栅电压VGS的变化曲线; (c)亚阈值特性; (d) RF功率50 W的器件三端击穿特性Fig.2.Electrical characteristics of GaN UMOSFETs fabricated with RF power of 50, 75 and 135 W (IGS and IDS are gate and drain currents): (a) Transfer characteristics; (b) field-effect channel mobility as a function of gate voltage; (c) subthreshold characteristics;(d) breakdown characteristics.

此处忽略了耗尽层电容的影响, k是玻尔兹曼常数,T是温度, q是单位电子电荷.通过进一步计算得出, 采用 RF 功率为 50, 75 和 135 W 刻蚀条件制备出的GaN UMOSFET的界面态密度分别是1.90 × 1012, 2.40 × 1012和 4.13 × 1012cm–2·eV–1.可以看出器件界面态密度随着干法刻蚀RF的增加而明显增加, 这是大的干法刻蚀损伤带来更多的刻蚀损伤所致.实验中发现不同RF功率对器件的三端击穿特性无明显影响, 器件耐压集中在350—380 V.图2(d)给出了 RF 功率为 50 W 的器件击穿特性曲线, 器件在限流为1 A/cm2条件下击穿电压约在378 V, 且器件击穿的原因是栅极击穿.栅极提前击穿是因为栅极和漏极之间SiO2与GaN形成的MOS结构具有正的价带带阶.随着漏极偏压的增加, 正价带带阶成为空穴向栅极移动的势阱, 使得空穴聚集在介质层表面, 从而产生电场集中现象, 造成栅极提前击穿[26].

本文制备的器件具有约80 nm的SiO2介质层, 理论阈值电压应该在 12—14 V, 而实际测量值明显负偏.实际器件中阈值电压负偏的原因主要有两个: 1)干法刻蚀存在刻蚀损伤, 尤其是由于高能离子轰击侧壁而在侧壁表面处产生较高浓度的氮空位[27], 而氮空位在GaN中属于浅施主, 施主能级比导带底低0.03—0.1 eV, 这种施主杂质会补偿一部分p-GaN沟道层中的空穴, 从而降低p型掺杂浓度, 甚至使表面p-GaN发生反型变成轻掺杂n-GaN[23]; 2)生长的SiO2介质层中存在有正的氧化物电荷, 正电荷等效于对半导体产生附加正偏压, 从而降低器件的阈值电压.

图3 采用光刻胶和SiO2作为刻蚀掩模制备出的GaN UMOSFET器件的电学特性曲线 (a)转移特性曲线; (b)沟道场效应迁移率随栅电压的变化曲线; (c)输出特性曲线; (d)亚阈值特性Fig.3.Electrical characteristics of GaN UMOSFETs with SiO2 and photoresist as etching masks: (a) Transfer characteristics;(b) field-effect channel mobility vs.gate voltage; (c) output I -V characteristics; (d) subthreshold characteristics.

为了得到较理想的U型槽形貌, 本文又研究了两种不同刻蚀掩模进行U型槽的干法刻蚀, 分别是1.6 µm的光刻胶掩模和500 nm的SiO2硬掩模.光刻胶直接采用光刻和显影形成相应图形, 而SiO2利用PECVD方法生长, 其图形通过光刻胶形成窗口后利用反应离子刻蚀机(RIE)刻蚀而成,光刻胶通过有机溶剂去除.图3(a)和图3(b)给出了采用光刻胶和SiO2作为U型槽刻蚀掩模的GaN UMOSFET的转移特性曲线及提取的沟道迁移率, 测试过程漏电压保持1 V, 两种器件均可实现开启关断, 两者沟道峰值迁移率分别为49.5和55.2 cm2/(V·s).图3(c)显示了不同刻蚀掩模制备GaN UMOSFET的输出特性曲线, 漏压从 0到10 V, 栅压范围 0 —16 V, 步长 2 V, 可以看出采用SiO2做掩模的器件导通电阻更低, 输出电流更大.从半对数坐标下的转移特性曲线可以提取出两种UMOSFET的亚阈值摆幅, 见图3(d), 分别是819和 609 mV/dec, 说明采用 SiO2做刻蚀掩模的器件的开关特性更好, 进而计算出相应界面态密度为 2.46 × 1012和 3.42 × 1012cm–2·eV–1.需要指出, 图3(d)提取的亚阈值摆幅相对于图2(c)中RF功率为75和50 W的器件亚阈值摆幅稍大.原因是图2(c)中改变RF功率的器件相比前者多了一步U型槽处理工艺, 即在进行U型槽干法刻蚀后, 刻蚀样品在85 ℃条件下25%的四甲基氢氧化铵 (TMAH)溶液中湿法处理1 h, TMAH热溶液对刻蚀侧壁起到修复损伤的作用, 同时不会影响沟槽深度[28].

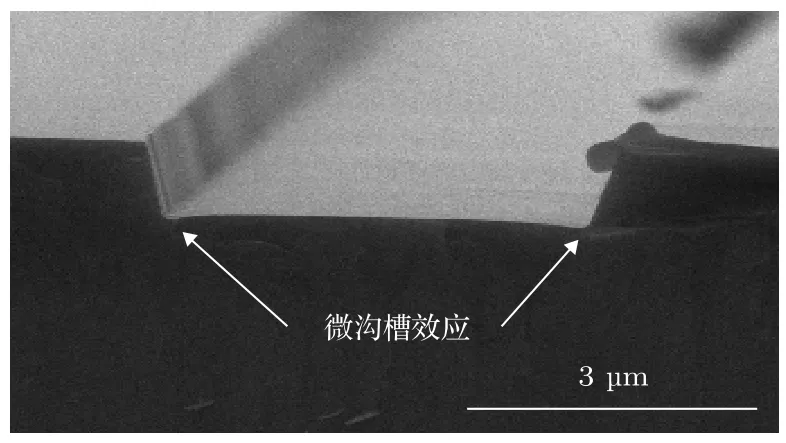

图4 (a)采用不同刻蚀掩模后 U 型槽的刻蚀形貌; (b)刻蚀掩模侧壁的高能粒子反射现象Fig.4.(a) Etching morphology of the U-shape trench using different etching masks; (b) high-energy ion reflection at the sidewall of etching masks.

为了探究采用不同刻蚀掩模的两种器件表现出上述不同电学特性的原因, 刻蚀后的样品经过原子力显微镜(AFM)来评价刻蚀形貌.图4(a)显示了不同刻蚀掩模相对应的沟槽形貌, 选取的沟槽形貌同为宽度约 8 µm, 刻蚀深度约 800 nm, 可以看出采用光刻胶的样品在沟槽底部两端处出现了明显的过刻蚀现象, 即微沟槽效应, 刻蚀后沟槽底部呈现中间高两边低的“凸”字型形貌, 图5是光刻胶做刻蚀掩模的样品U型槽区域的扫描电子显微镜(SEM)图像.这种U型槽形貌会导致器件在导通时, 载流子流经器件积累区受到的散射作用更大,从而降低器件的工作电流.

图5 光刻胶掩模的样品经U型槽刻蚀后的SEM图像Fig.5.SEM image of U-shape trench after dry etching with photoresist etching mask.

这种现象出现的原因来自两种刻蚀掩模的形貌不同, 见图4(b).正性光刻胶作刻蚀掩模时, 经过显影和坚膜处理后, 光刻胶侧壁存在一定角度,形成梯形结构, 且光刻胶厚度约在 1.6 µm, 因此具有较大的侧壁面积.高能粒子经过侧壁反射后, 在ICP腔室的垂直电场作用下反射轨迹出现弯曲, 所以更容易出现侧壁处过度刻蚀[29].而SiO2硬掩模与GaN材料的刻蚀选择比相较于光刻胶更高,SiO2的厚度仅为500 nm, 因此高能离子的侧壁反射效应减弱, 避免了过刻蚀现象.

4 结 论

本文对U型槽的干法刻蚀条件进行了改善,主要研究了RF功率和干法刻蚀掩模对GaN UMOSFET电学特性的影响.实验结果表明, 适当降低RF功率可以减少工艺带来的干法刻蚀损伤,从而提高器件沟道的场效应迁移率, 且器件的亚阈值摆幅和界面态密度随着RF功率的降低而降低,器件的开关特性更好.相比于光刻胶, 厚度较薄的SiO2更适合作为U型槽刻蚀中的刻蚀掩模, 采用此种方法制备的UMOSFET器件的沟道峰值迁移率更优, 界面态密度更小.在未来的研究中, 我们将综合调节包括RF功率、腔室压强、反应气体流量等多项参数, 继续降低刻蚀损伤, 进一步优化器件电学特性.