GaAs HBT 中测信号防护处理

2020-05-11肖宗勇陈剑平陈燕玲徐智文

肖宗勇,陈剑平,陈燕玲,徐智文

(福建省福联集成电路有限公司,福建 莆田351115)

1 引 言

电性测试的目的是检验规格的一致性及可接受的电学性能。如果发现电性缺陷,将确保有缺陷的芯片不会送至客户端,并纠正制作过程中的问题[1]。电性测试必须迅速、准确地完成。测试中的高废品率会削弱芯片的市占率,但若测试程序不完善造成低废品率,将有更多产品在客户使用过程中失效,增加转移订单的风险。为避免该情形,正确地得到电性良率是必须的。

GaAs HBT 器件的中测(Circuit Probing, CP)过程主要以直流测试(例如:漏电流/偏压和输出电流)为主,有时会增加射频功能测试项[2](例如:增益/小增益/P1dB/Pout),对应使用的测试工具是悬臂式探针卡。悬臂式探针卡主要由印刷电路板、探针、环氧树脂和固定环四个部分组成,是测试机与晶圆间重要的媒介工具。藉由探针卡的探针与晶圆上的焊垫或凸块接触,将电性信号传送到测试机并分析其功能与特性,进而判别晶粒的好坏[3]。中测可能会出现误判的情况,其原因有测试机与探针卡的匹配问题或测试人员操作不当等[4]。探针和晶粒接触在电气性能上有所局限,容易因接地讯号处理不良而产生漏电和接触电阻异常,这对于处理高精度的信号测量会带来不良的影响。因此设计探针卡时要提供正确的焊垫坐标及配置,并根据不同的测试条件配置滤波及阻抗匹配。

针对GaAs HBT 器件发生中测误判的情形,可通过滤波、阻抗匹配及电磁屏蔽的方法改善探针卡,以得到真实的良率,满足量产快速检测需求。

2 工作原理

中测设备采用美国泰瑞达J750EX 测试机和日本东京精密UF200 系列探针台,并搭配悬臂式探针卡。电脑端软件IG-XL 通过GP-IB 连接J750EX 测试机与探针台共同完成测试作业。中测的部分测试流程如下:从测试仪通过电缆束至测试头,再通过测试头至探针卡,然后通过探针至芯片上的焊点,到达被测器件,最后沿原路返回测试仪器[5]。最终电脑端通过测试条件中的规格范围,判定此颗晶粒是否为良品。重复上述动作,即可得晶圆电性良率。

3 结构与设计

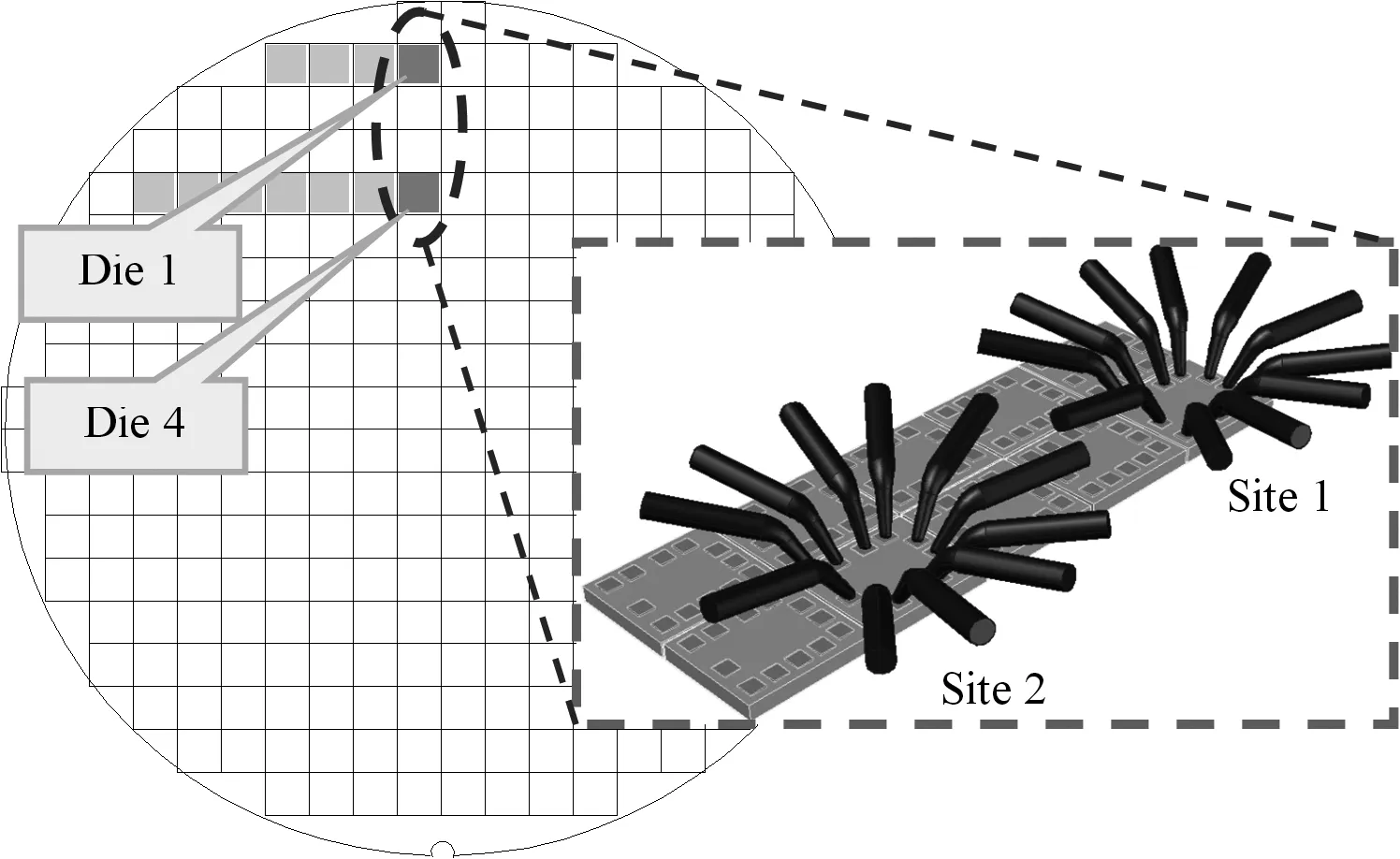

在验证器件电性的过程中,为提升产能利用率,减少测试时间,降低测试过程中的无用功,会选择Multi-Site 并行测试,将大大提高并行测试效率[6]。由于探针卡上的Site(测试单颗晶粒的所有探针)彼此之间会产生相互讯号干扰,进而影响测试数值,因此将Site 设置为间隔两个晶粒进行制作。如图1 所示,Site1、Site2 同时下针并测试Die1、Die4 电性,目的是减少Site 与Site 之间的干扰。

图1 探针间隔两个晶粒测试示意图

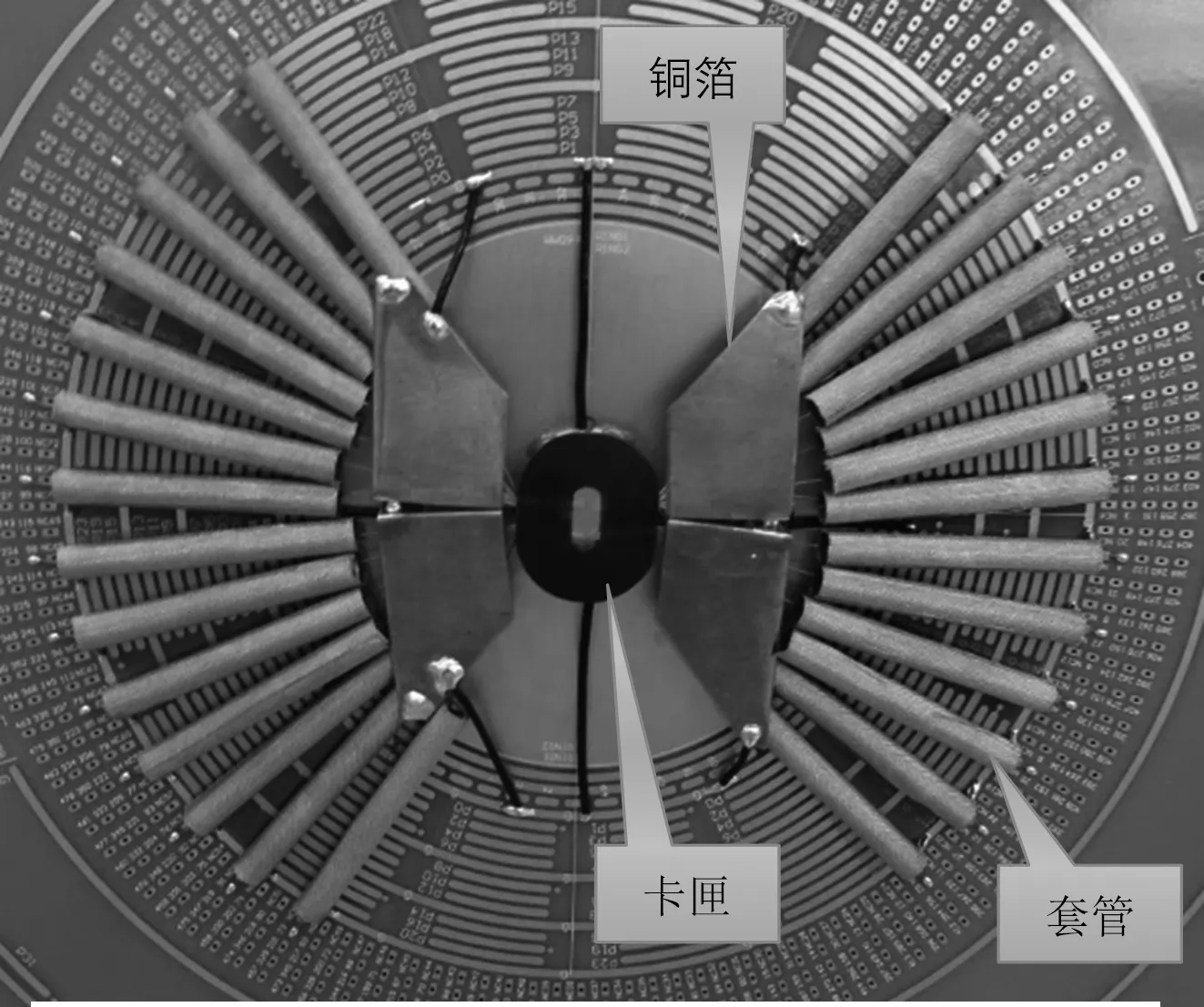

即使Site 之间已间隔两个晶粒,于单一Site 中同时进行所有电性测试项仍会造成误判,因此需要对两个Site 均做电磁屏蔽处理。完成电磁屏蔽的探针卡如图2 所示,中间的卡匣用于固定悬臂式探针位置,铜箔遮挡导线较集中的区域,其他导线则穿过套管。套管由屏蔽胶带包覆磁珠组成,目的是抑制信号线及电源线的高频噪声与尖峰干扰,并屏蔽电磁干扰。之后再根据测试需求进行滤波及阻抗匹配,可得到合理的电性良率。

图2 完成电磁屏蔽的探针卡

4 结果与分析

4.1 失效分析

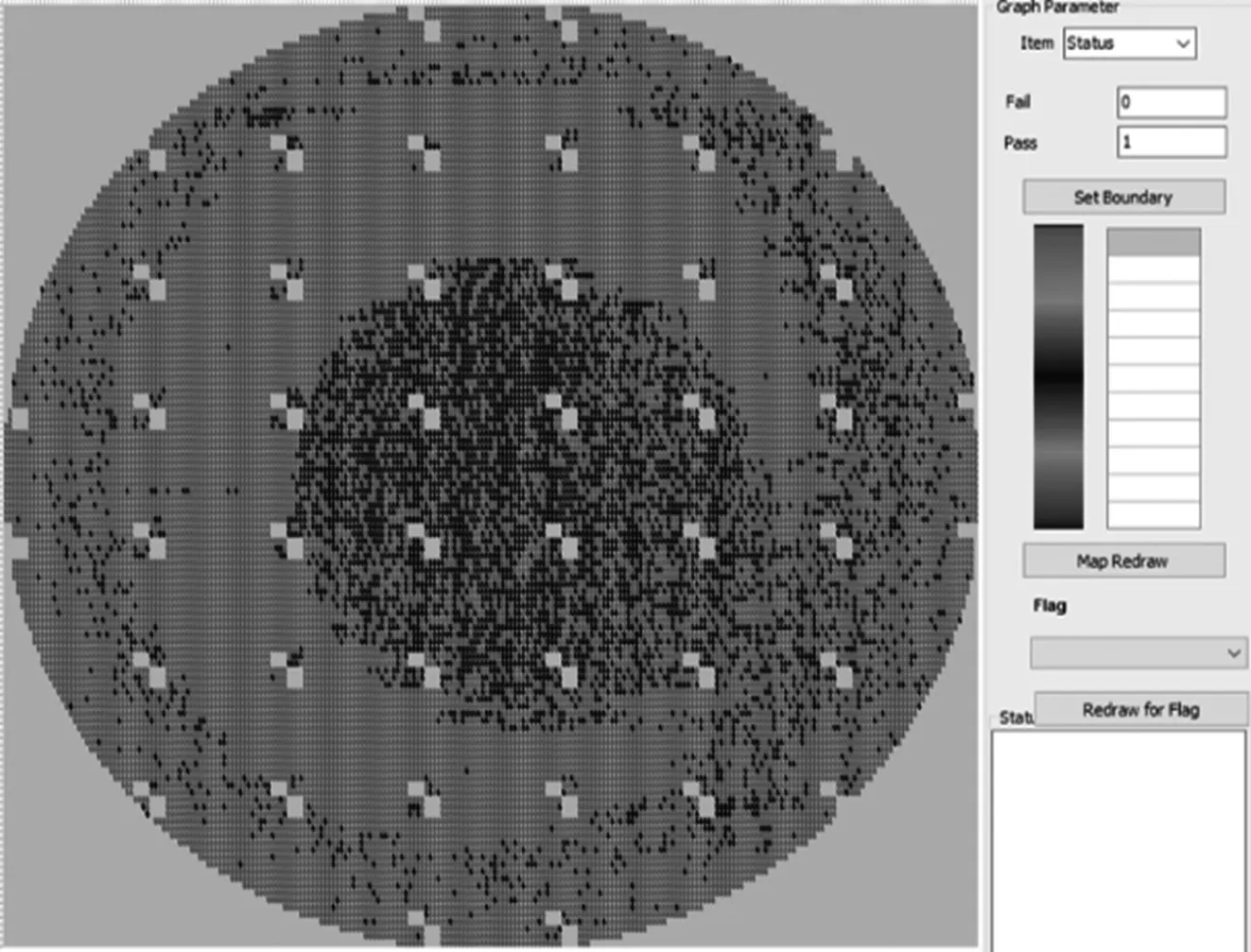

电性测试的良率不佳,可能来自工艺造成的不良或测试造成的误判。若是中测的误判,会出现部分晶粒电性呈现时好时坏的现象。除了屏蔽电磁干扰外,也须针对信号干扰进行处理,以得到稳定且可再现的量测结果。图3 是未进行电路匹配、所有测试项迭加的良率分布图。浅色(即不良品)占大部分面积,整体图形呈环状分层现象。该结果大多是测试信号存在严重干扰与振荡造成,与器件本身性能无直接相关。

图3 未电路匹配的中测良率(22.19%)

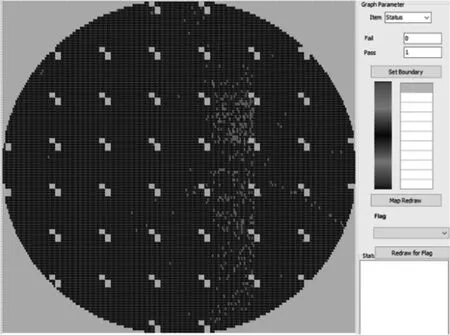

图4 是进行电路匹配后,所有测试项迭加的良率分布图。深色(即良品)占大部分面积,且比例符合出货良率最低要求。探针卡进行电磁屏蔽及电路匹配后,中测良率从22.19%变为98.28%,避免大量的误判,并满足迅速、准确地检测需求。

图4 电路匹配的中测良率(98.28%)

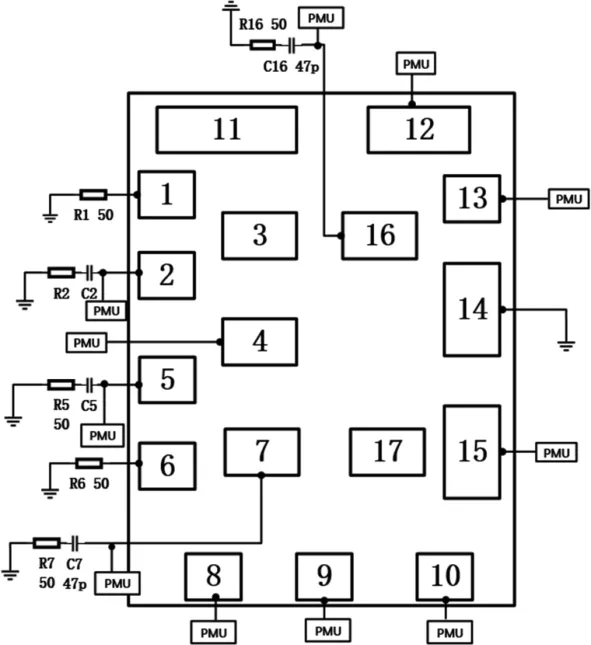

图5 是探针卡电路滤波及阻抗匹配原理图。在GaAs HBT 器件的测试过程中,测试结果会因外界电磁干扰与样品本身产生干扰信号而产生偏差。电容在电路中主要起到滤波作用,滤除信号中高频尖峰,稳定信号幅值。为了增强滤波作用效果,在针尾处添加了电感。由电感与电容组成的电路,主要起到滤波、振荡、延迟、陷波以及筛选信号、过滤噪声、稳定电流及抑制电磁波干扰等作用。探针卡配置的电容及电阻方案是针对测试条件中,输入电压的管脚与需要收电流值的管脚(依业界目前规格选用50Ω 的电阻与47pF 的电容)。

图5 探针卡电路滤波及阻抗匹配原理图

器件测试项3 在Pad2 及Pad5 输入电压;测试项4 在Pad7 和Pad16 输入电压,因此在探针卡对应的Pin2、Pin5、Pin7、Pin16 都分别串联电容与电阻。若使用并联会导致电容和电阻值变小,从而产生波扰。串联的目的是为了减少干扰,降低阻抗。

4.2 结果分析

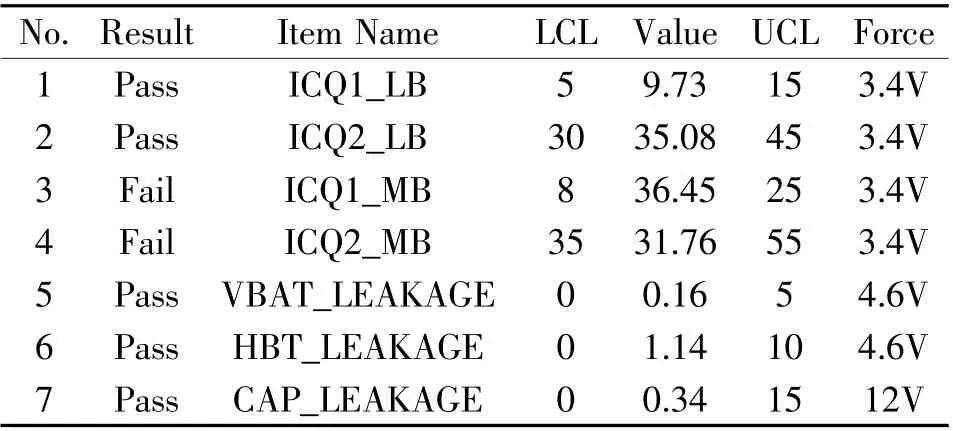

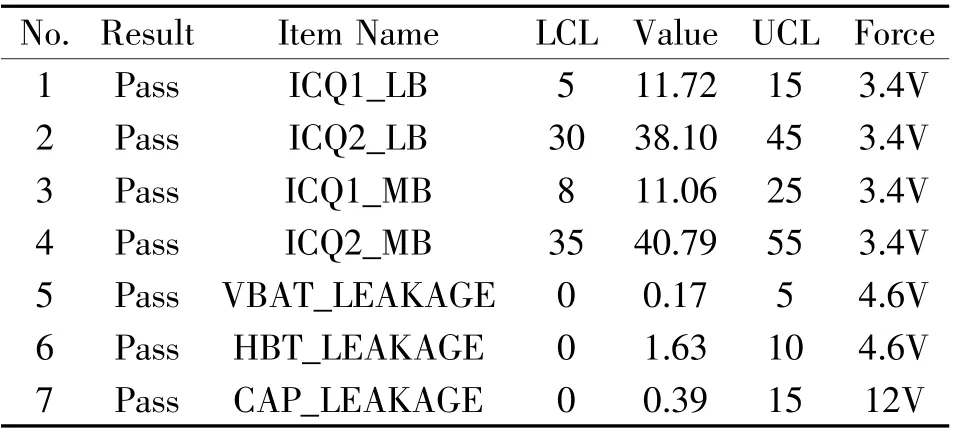

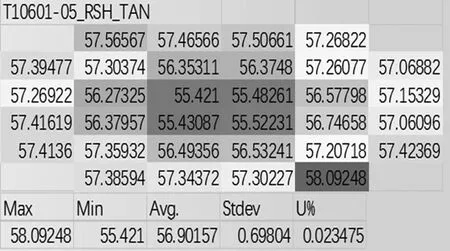

表1 是探针卡未电路匹配时,某器件中测的数值。测试项3 的Pin2 与Pin4 分别接在Collector 端与Base 端,所得电流输出值为Pin10 和Pin12 的总和。ICQ1_MB 电流值为36.45 mA,高于该测试项的上限。测试项4 的Pin2 与Pin4 分别接在Collector端与Base 端,所得电流输出值为Pin10 和Pin12 的总和。ICQ2_MB 电流值为31.76mA,低于该测试项下限。由于电源刚开启,电路中存在不稳定的电流振荡,没有及时抑制与滤除,若信号刚好处于尖峰或低谷,就会出现超过规格的状况。表2 是探针卡电路匹配后同器件中测的数值,所有测试项均在规格之内。

表1 未电路匹配的中测结果

表2 电路匹配的中测结果

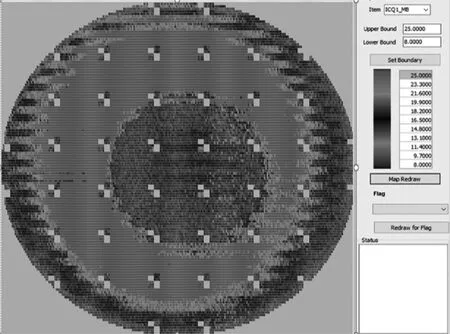

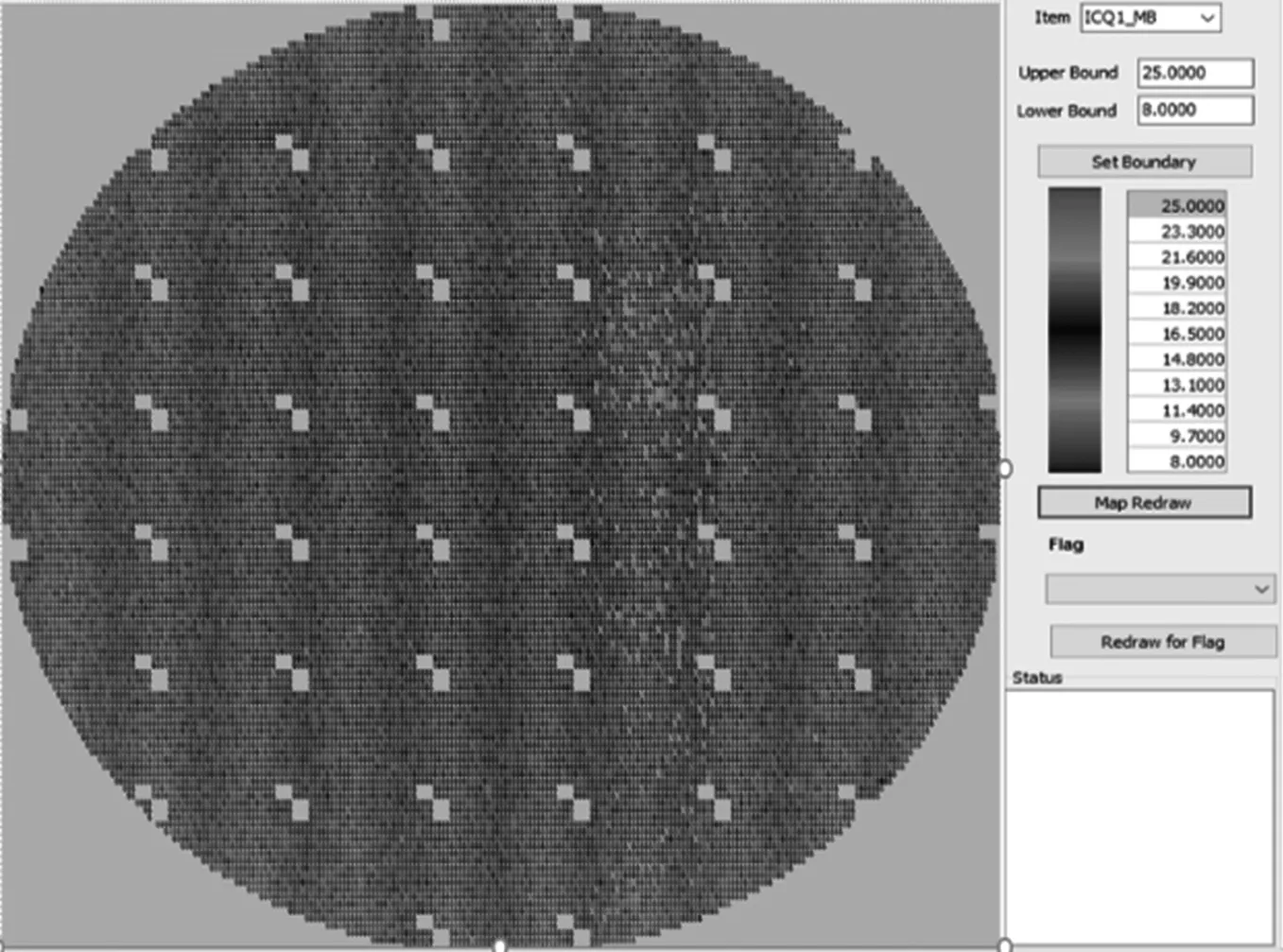

图6 是电路匹配前测试项3 的Map,Map 分为三种颜色,其中浅色与深色区域的分层现象是探针卡的振荡影响造成。由于传输在探针上的电压不稳定,导致信号波动,使器件电性反馈不稳定。亮色区域是探针卡存在着Site 与Site 之间电磁相互干扰导致的,因此在探针卡的针尾处添加电感来抑制电磁波干扰,使多个Site 之间相互独立工作而不受干扰。

图6 电路匹配前测试项3Map

图7 是电路匹配后测试项3 的Map。图8 是WAT 测试的片电阻(Ω·cm)shot 分布情况,电路匹配后测试项3 与TaN 片电阻U%相符,表示该测试项可反推中测结果是否存在明显的振荡与干扰。

图7 电路匹配后测试项3Map

图8 晶圆的TaN 片电阻值

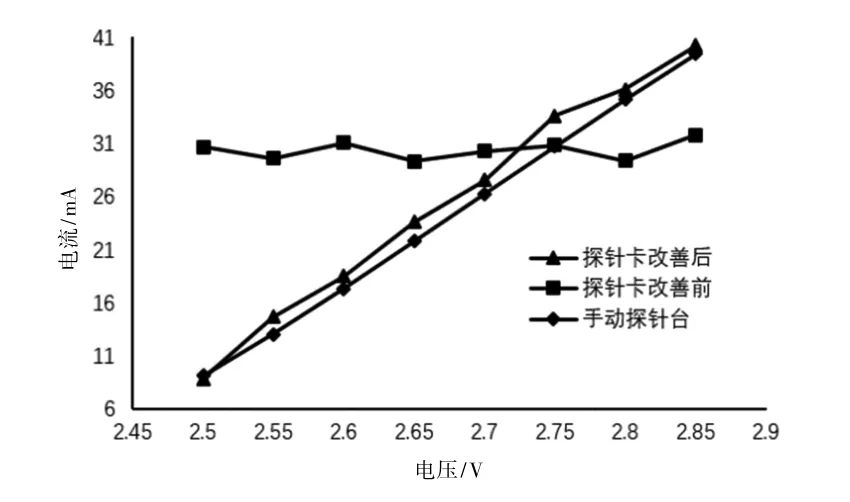

手动探针台可应用在射频/毫米波器件表征中。通过在一定偏置条件下对CV、IV、S 参数的片上测量结果,可以清晰地表达和模拟器件的性能[7]。手动探针台是探针直接与晶粒接触,测试的电性比较准确;而中测需借助探针卡与晶粒接触,所以需要进行额外的信号处理。为确认中测结果的可靠性,使用手动探针台的数据进行对比。图9 是针对同一晶粒,在2.5V~2.85V 区间内进行ICQ2_MB 测试项的电流测试,并比较三种方式之间的差异。藉由中测与手动探针台量测的I-V 曲线比较,在95%置信水平上,自由度为7 时t 值为2.365,因为t计算<t表,说明在该置信水平上两种方法无显著性差异[8]。确保探针卡改善后的检测数值与手动探针台的数值相符。

图9 不同量测方式于同一晶粒进行I-V 曲线比较

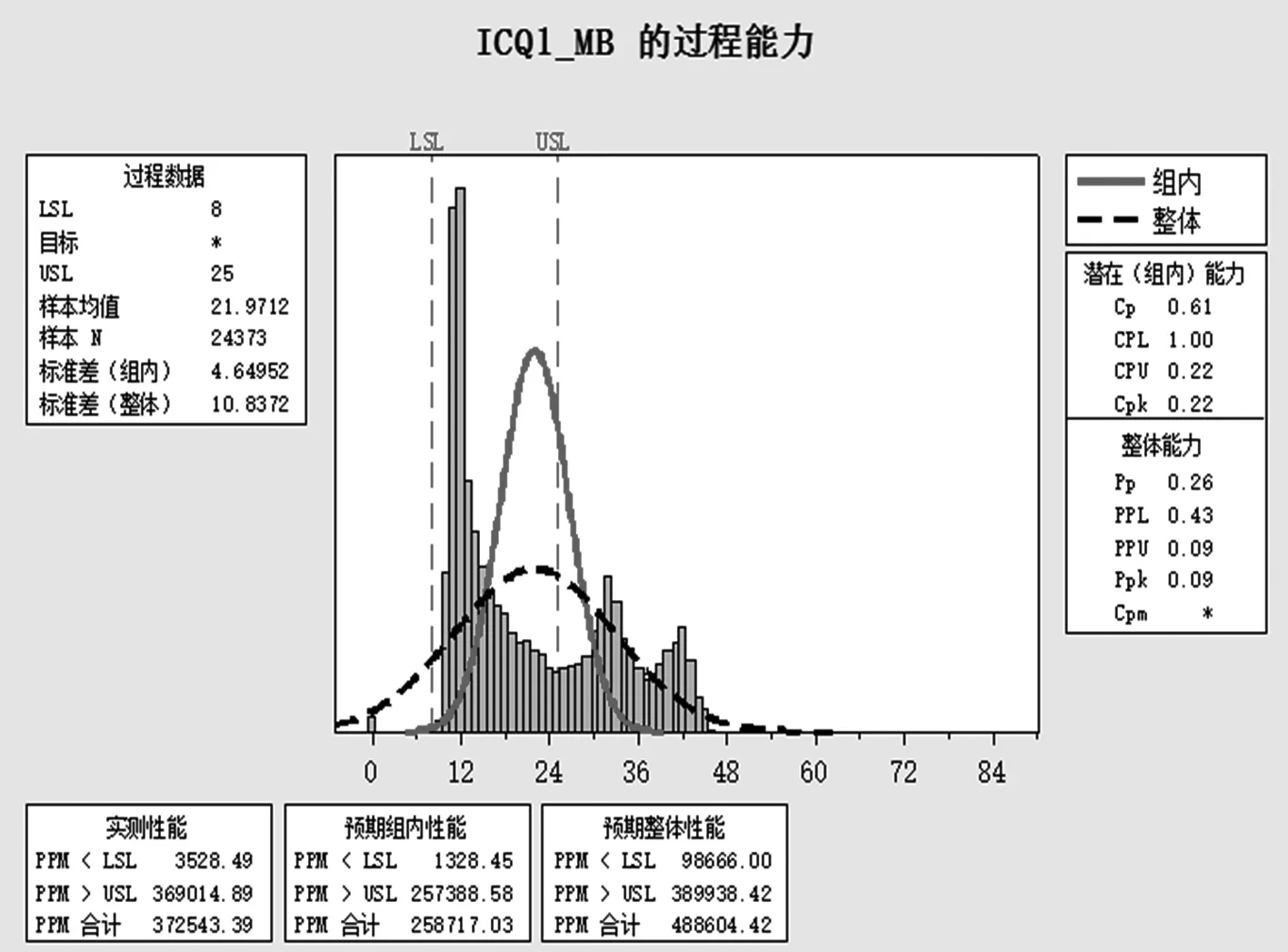

图10 是电路匹配前测试项3 的高斯分布,测试项3 的结果分布是从10mA 到45mA。但该结果分布与实际TaN 片阻值U%不符,且分布较为发散。图11 是电路匹配后测试项3 的高斯分布,其结果分布较集中且在规格上下限的区间之内。从电流值的高斯分布可得知中测结果属于集中或发散,可间接反映工艺稳定性,以及多数晶粒是否满足规格要求。通过TaN 片电阻U%与测试项3 的比较,检验探针卡改善后振荡与干扰的现象,可作为中测结果是否可靠的参考依据,并评估电磁屏蔽及电路匹配方法是否合宜。由于单个晶粒的每个测试项目进行的测试时间很短,任何的外部干扰信号波动都会影响测试的最终结果数据。故若要防止量测时的干扰与振荡的情况发生,可以事先针对探针卡作好防干扰与振荡的防护处理。

图10 电路匹配前测试项3 高斯分布

图11 电路匹配后测试项3 高斯分布

5 结 束 语

针对GaAs 芯片在中测时产生异常现象的研究,提出了对探针卡进行干扰与振荡的防护措施,采用电磁屏蔽与电路匹配的方式,并与中测设备相结合的测试过程,可以避免大量的误判,满足快速、准确的检测需求。在探针卡的改善方面,未来可以增进探针数量,并满足更高频的器件量测,其设计细节和存在的问题还有待在后续研究中进一步摸索。