集成电路组装过程中裸芯片目检不合格类型与原因分析

2020-05-11周安琪张育赫王丽丹

周安琪,张育赫,王丽丹

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引 言

芯片目检是集成电路质量控制的重要环节,贯穿在整个组装过程中。为了保证军用集成电路的质量,我国制订了国军标。通过执行军用集成电路质量检验标准,集成电路的寿命与可靠性稳步提高。裸芯片检验是集成电路组装的第一步,须严格按照GJB548B 方法2010.1 内部目检标准进行[1]。

以20 个批次的代表芯片为研究对象,通过目检和统计分析,归纳出裸芯片目检不合格的主要类型。进一步开展不合格原因分析,提出过程优化控制方法并加以实施,确保每个批次的裸芯片目检不合格率明显下降。

2 目检方式及判据

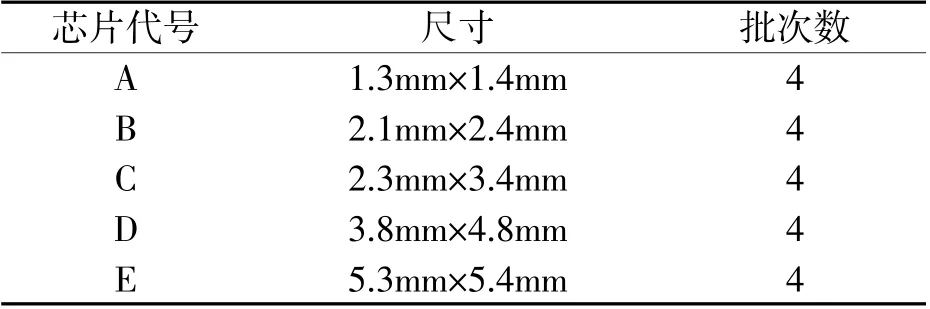

对待检裸芯片采用随机抽取的方式,随机抽取A、B、C、D、E 五种不同型号芯片,选取每种型号芯片的4 个批次,每个批次抽取50 只为统计样本,在电子显微镜下75~150 倍进行目检,按照GJB548B-2010.1 对该20 批次共计1000 只裸芯片进行目检,统计样本如表1 所示。

表1 统计样本表

3 主要不合格类型

3.1 芯片表面金属化划伤及裂纹

按GJB548B 方法2010.1 规定,划片槽内裂纹长度超过25 微米且除键合区和梁式引线以外,金属化层的划伤沿长度方向暴露出下层钝化层,使保留的未被破坏的金属宽度小于原始金属条宽的50%,均判定为不合格[2]。

金属化层的划伤主要是芯片储存、传递、组装过程中人为因素造成的。划伤使金属化层的有效导电截面积减小,因此电流承载能力下降,导致该处金属同其他正常部位相比容易出现过流熔断。另外,在使用过程中由于受到损伤的金属化层部位的有效导电截面减小,使该处的实际电流密度增加,所以更容易发生电迁移导致铝条开路失效[3]。

3.2 芯片金属化层图形缺陷

GJB548B 方法2010.1 中规定,金属化层中的空洞使未受破坏的部分小于原始金属条宽度的50%或金属化层出现隆起、起皮或起泡现象不得接收。

芯片金属化层图形缺陷多发于芯片制造工艺过程中,是先天即存在的薄弱环节[4]。空洞或原始金属条宽度不足,不仅仅会导致单个芯片的电性能问题,更有可能引发整个批次的共性问题,应比照芯片图纸对线条进行全局性的检查。

3.3 芯片表面污物

GJB548B 方法2010.1 中规定,芯片表面的液滴、化学污斑、油墨或光致抗蚀剂跨接了未被玻璃钝化层覆盖的任何金属化层或裸露的半导体本体区域为不合格。

如果沾污桥联了电路内部不同电位的工作区,可能导致电路内部工作材料间的漏电增加或短路;如果多余物含有腐蚀性物质,可能导致金属化层腐蚀;如果沾污材料足够厚,可能影响芯片的局部散热。这些因素,都会对元器件服役过程中的使用寿命和可靠性造成很大程度的影响[5]。

3.4 芯片嵌入多余物

GJB548B 方法2010.1 中规定,在芯片表面上附着或嵌入的多余物,桥联了包括金属化层在内的有源电路元件,除非用暗场照明下的高放大倍数验证它仅是附着而不是嵌入。

该种情况可能导致电路内部工作材料间的意外短路,对电路的性能造成影响。此外,对于应用在高加速环境中的元器件,对密封腔体内部多余物有额外的要求,芯片粘附的颗粒物可能在应用中脱离,并产生较高的动能损伤键合引线等关键部位[6]。

4 统计与分析

4.1 主要不合格类型统计

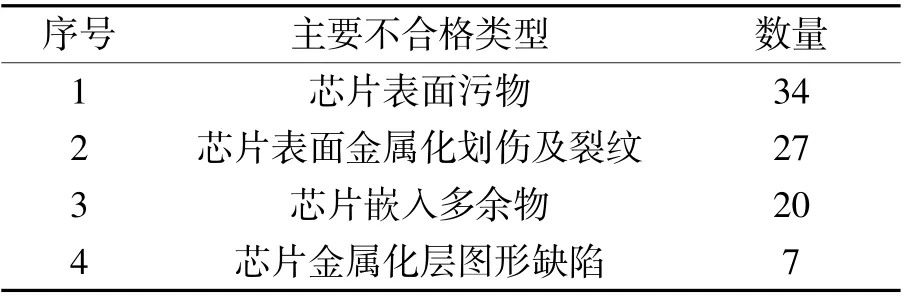

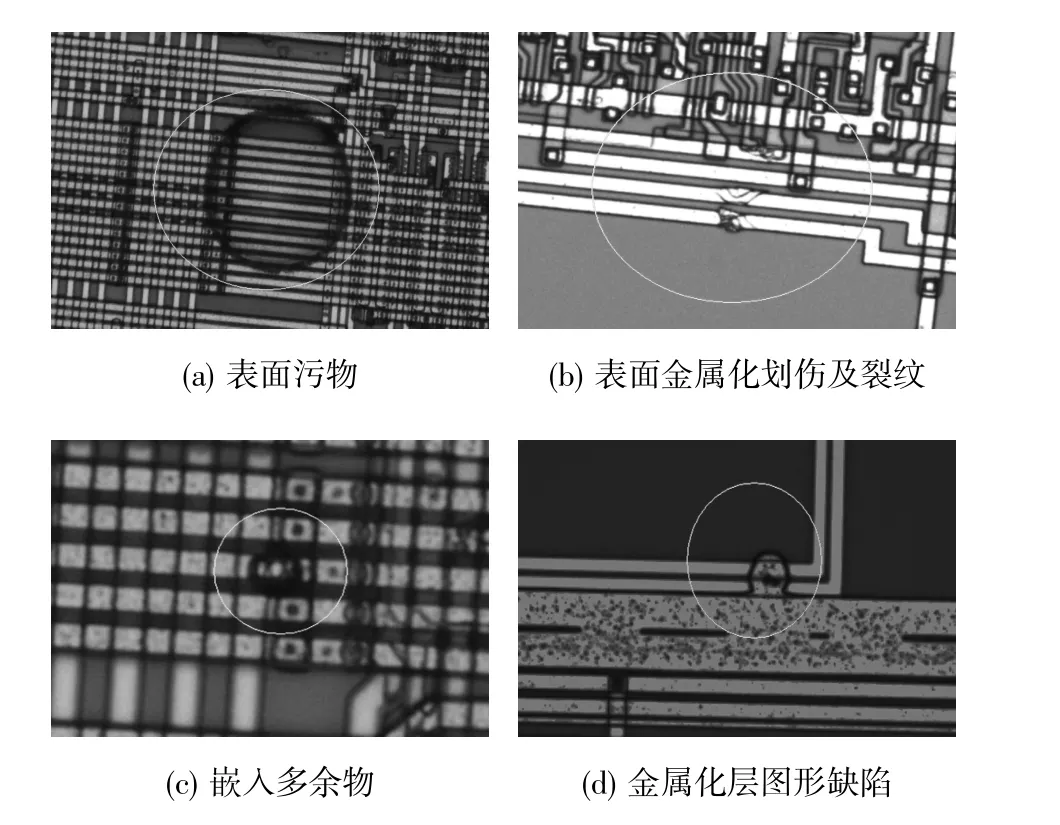

根据随机抽取的20 个批次的芯片,共1000 只芯片的统计,可以得到总体的不合格类型分布,如表2 所示,主要不合格类型图例如图1 所示。

表2 主要不合格类型统计表

图1 主要不合格类型图例

4.2 主要不合格类型的机理分析

从表2 中可以看出,芯片表面污物是导致芯片目检不合格的最主要因素之一。进一步对A、B、C、D、E 五种芯片统计不合格数量,分别为5 只、6 只、8只、7 只和8 只,表现出较为均匀的分布,说明该种不合格现象具有共性。需要对供应商和组装生产线进一步加强控制。

芯片表面金属化划伤也是较为多发的典型不合格类型之一,A、B、C、D、E 五种芯片不合格数量,分别为8 只、6 只、7 只、4 只和2 只。随着芯片面积的增大,划伤数量呈现递减的趋势。通过鱼骨图分析,发现在夹取芯片过程中,工具使用控制不当是引起芯片划伤的主要原因因素。

芯片多余物的来源较多,一方面是可移动组装多余物,例如芯片粘接材料的颗粒、键合丝尾线等,可直接用工具、气体等辅助手段使其于芯片剥离[7];另一方面是高温烘焙、固化时,固定在芯片表面的不可移动多余物,需尝试在不损伤芯片的前提下使用坚硬工具剔除[8]。

5 控制措施及效果

基于上述分析,可制定如下控制措施:

(1) 对芯片拾取、传递、保存等环节进行优化处理,严格控制工作环境的洁净度、温湿度,同时对于静电进行控制,防止颗粒物吸附到裸芯片表面。

(2) 用吸笔拾取到裸芯片放置托盘中代替人工用镊子夹取裸芯片到玻璃板上,条件允许情况下可采用全自动粘片设备,避免人工粘片夹取时对芯片的损伤。

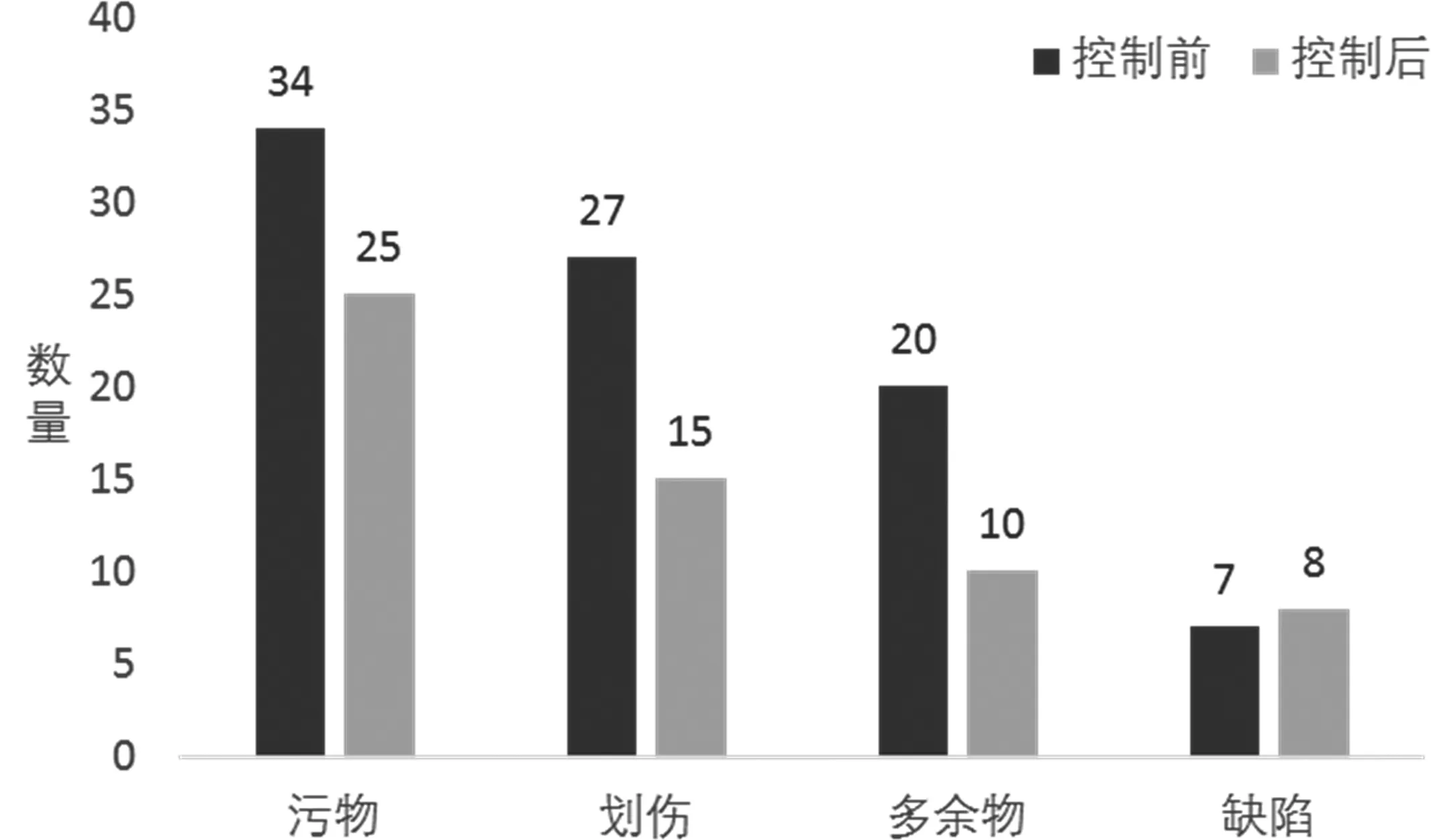

实际施行上述优化控制措施后,发现对于裸芯片划伤、污物、多余物不合格现象有显著减少,但是对于芯片嵌入多余物和芯片金属化层图形缺陷问题没有明显改善。优化前后的对比如图2 所示。

图2 优化前后对比图

6 结 束 语

裸芯片目检是集成电路质量检验中的重要环节。以若干批次的芯片为研究对象,通过目检和统计,分析了裸芯片目检的主要不合格类型。进一步研究了目检不合格原因,提出并实施了过程优化控制方法,使各批次的裸芯片目检不合格率明显下降。