基于FPGA的TCP段乱序重排设计与实现

2020-05-06杨宪伟李治辉

黄 锐,王 银,杨宪伟,李治辉

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

随着网络带宽需求爆发式的增长,传输控制/网际协议(Transmission Control Protocol/Internet Protocol,TCP/IP)处理占用了越来越多的处理器(Central Processing Unit,CPU)时间,使得计算机在处理万兆级别的业务流时无法充分利用CPU的性能[1,2]。因此,通过硬件实现已经十分成熟且与业务松耦合的底层TCP/IP协议栈,使CPU更专注于处理业务是一种高效灵活的做法[3]。

TCP协议属于传输层协议,通常运行于网络层IP协议之上。IP网络传输数据存在因网络拥塞和传输错误导致的报文丢失以及多路由转发导致的报文乱序等问题[4]。如果TCP协议栈对不连续报文不加处理,直接丢弃,可能会导致网络拥塞加剧,传输效率降低,因此TCP协议栈需要合理高效地处理乱序报文[5]。

软件TCP协议栈通常采用链表的方式处理乱序报文[6]。而对于硬件实现的TCP协议栈如果也采用链表的方式处理,那么每个报文都需对链表进行搜索匹配等操作,不但复杂度极高,而且处理效率也会受到极大影响,因此需要设计一种符合硬件实现特点的高效乱序重排方法。

本文提出一种适用于现场可编程逻辑阵列(Field Programmable Gate Array,FPGA)实现的TCP/IP硬件协议栈的乱序重排实现方法,首先简要介绍TCP/IP硬件协议栈的架构,然后详细介绍硬件协议栈段乱序重排的实现方法。

1 TCP/IP硬件协议栈架构

TCP/IP硬件协议栈架构如图1所示。

图1 TCP硬件协议栈架构

协议栈前端包括链路层处理模块万兆以太网媒体访问控制器(Medium Access Control,MAC)和IP层协议处理部分。IP层处理模块负责提取报文的源IP地址、目的IP地址以及TCP源端口和目的端口信息,匹配TCP连接信息,匹配成功获取相应的连接索引号后送入TCP处理模块进行后续处理。

TCP连接状态控制模块负责TCP连接建立过程中的3次握手及关闭时的4次挥手的状态跳转控制[7]。当TCP连接不处于连接已建立(ESTABLISHED)状态时,报文由该模块处理。TCP接收模块负责对处于ESTABLISHED状态的连接所接收到TCP报文进行处理,该模块先判断报文合法性,然后根据已接收数据块信息对接收报文进行排序。

缓存管理模块负责对TCP连接的接收和发送环形缓冲区进行读写管理,并维护每条连接的读写地址偏移和序号(Sequence Number,SN)等相关信息。

2 硬件协议栈乱序重排方法

2.1 报文处理流程

乱序重排功能在TCP接收模块内实现。接收模块先提取报文的TCP头部信息,根据SN、长度及接收窗口信息判断报文是否有效,然后根据接收信息表所记录的已接收数据信息判断报文所携带数据相对位置,同时计算出新的接收信息表,最后将数据发送到缓存管理模块并写入缓存。

2.2 数据结构

接收信息表数据结构如图2所示,其记录了下一个待接收的字节序号RCV.NXT和不连续数据块记录Qi=(RCV.FSN,RCV.LSN),其中i=[0,1,2]指示数据块序号,RCV.FSN为数据块起始字节序号(First Sequence Number,FSN),RCV.LSN为末尾字节序号(Last Sequence Number,LSN),如果对应数据块位置数据无效则FSN及LSN字段均置0。

图2 接收信息表数据结构

RCV.NXT表示已确认接收数据区。记录的不连续数据块位于RCV.NXT至RCV.NXT+WIN_SIZE之间,WIN_SIZE为接收窗口大小。Q0,Q1,Q2这3个数据块序号为递增排列。缓存信息表记录该条连接缓存内已写入的数据长度WRLEN、已读出的数据长度RDLEN以及下一个待接收的字节编号FSN及其地址FADDR。

2.3 乱序重排算法

乱序重排的关键是判断新接收数据所处的相对位置,并对数据块记录进行重新排序,确保Q0~Q2按发送的先后顺序排列。

首先,根据前端IP层处理模块匹配得到的连接索引号,读取对应的接收信息表。先判断报文是否处于有效窗口内,同时判断接收信息表记录的数据块是否有效。对于接收到的TCP报文,其起始数据序号为SN,数据长度为LEN,如果RCV.NXT+WIN_SIZE≤SN或SN+LEN≤RCV.NXT,则报文无效,丢弃[8]。对于数据块Qi,如果RCV.FSN与RCV.LSN相等,则该数据块无效,后续处理忽略该数据块。

其次,比较新收数据块与已接收数据块关系。SN=RCV.NXT时记为B1,RCV.NXT< SN<RCV.FSN0时记为B2,RCV.FSN0≤SN≤ RCV.LSN0记为B3,RCV.LSN0<SN<RCV.FSN1记为B4,RCV.FSN1≤SN≤RCV.LSN1记为B5,RCV.LSN1<SN<RCV.FSN2记为B6,RCV.FSN2≤SN≤RCV.LSN2记为B7,RCV.FSN2<SN时报文无效。

SN+LEN=RCV.NXT时报文无效,RCV.NXT<SN+LEN<RCV.FSN0时记为E1,RCV.FSN0≤SN+LEN≤RCV.LSN0记为E2,RCV.LSN0<SN+LEN<RCV.FSN1记为E3,RCV.FSN1≤ SN+LEN≤ RCV.LSN1记为E4,RCV.LSN1<SN+LEN<RCV.FSN2记为E5,RCV.FSN2≤ SN+LEN ≤ RCV.LSN2记为E6,RCV.FSN2<SN+LEN时记为E7。

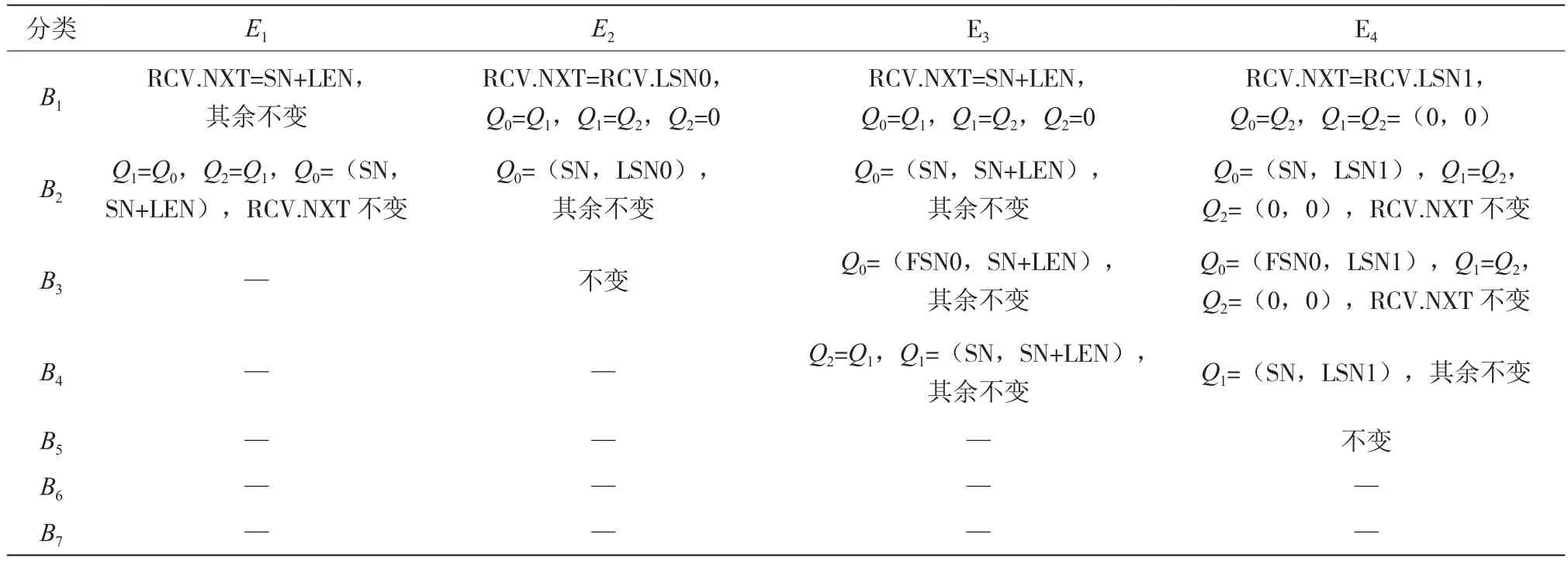

再次,根据比较结果更新数据块记录,如表1、表2所示。

表1 数据块记录计算(E1~E4)

表2 数据块信息计算(E5~E7)

最后,将合法数据发送到缓存管理模块。缓存管理模块根据数据块起始SN值与缓存信息表FSN值之差计算出数据块,写入偏移OFFSET=SN-FSN,数据写入地址为Wraddr=FADDR+OFFSET。

3 性能分析及测试结果

接收信息表用FPGA内部RAM存储,数据接口为64位宽,TCP接收模块根据连接索引号读出全部数据需要5个时钟周期,分析TCP报文与读表并行进行,位置比较与数据块记录重新生成需要3个时钟周期,生成缓存管理模块所需信息需要2个时钟周期,再加上状态控制需要2个时钟周期,因此每个报文除了处理数据外还需要额外的12个时钟周期。假设TCP报文长度为常见的1 480字节,数据处理接口为128位宽,则数据处理需要93个时钟周期[9]。系统时钟频率为250 MHz,此时报文处理能力为2.38 M/s,远大于万兆网络每秒最大报文量0.8 M。假设TCP报文长度为最小的576字节,则数据处理需要36个时钟周期,此时报文处理能力为5.2 M/s,而此时万兆网络每秒最大报文量2 M。即使考虑最差情形,即报文不携带数据,该情形下报文处理能力为17.8 M/s,而万兆网络报文量为16 M/s,依然能满足要求。上述分析表明进行端乱序重排的TCP接收模块处理性能可以满足万兆网络所有情形下的处理要求。

TCP硬件协议栈利用Intel Stratix V FPGA实现,将其配置为服务端,并将内部数据接收和发送接口环回。以Dell Precision T7610工作站为客户端,用Intel X520-SR2万兆网卡与服务端连接,使用自行编写的测试软件对TCP硬件协议栈性能进行测试。

测试结果表明,FPGA实现的TCP硬件协议栈数据收发速率达到9.388 Gb/s,即包含本文所述乱序重排实现方法的TCP接收模块处理性能满足要求。

4 结 论

本文先简要介绍一种基于FPGA的TCP硬件协议栈的架构,对其中的TCP段乱序重排的数据结构及实现方法进行详细说明,最后对其性能进行了分析及测试,结果表明利用该方法实现的TCP协议栈处理能力达到10 Gb/s。本方法具有逻辑简单、处理高效及资源消耗低等优点,但存在的不足是不连续数据块记录只有3个,当到达的互不相邻的报文超过3个时只能丢弃等待重传,不过该问题出现的概率极低,可以通过增加不连续数据块记录数量来优化[10]。