一款53~99 GHz硅基毫米波宽带低噪声放大器

2020-04-08刘贤栋苏国东孙玲玲

刘贤栋,苏国东,孙玲玲

(杭州电子科技大学微电子CAD所,浙江 杭州 310018)

0 引 言

宽带低噪声放大器作为低噪放的一个分支,受到业界的广泛关注与研究。传统的宽带放大器使用分布式结构,但分布式功耗高,噪声大,在毫米波频段应用少[1]。目前,在硅基互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺中,毫米波宽带设计主要使用平衡式[2]、反馈式[3]结构和宽带匹配技术,反馈式会增加放大器的噪声系数,平衡式放大器采用双路结构,而单端结构的放大器一般使用宽带匹配技术来实现毫米波宽带,利用宽带匹配网络的单端放大器得到较广泛的研究。在目前采用CMOS工艺的文献中,针对较低频段的Q(33~50 GHz)至V(50~75 GHz)波段毫米波低噪放有不少研究[4-5],但这些带宽小于50%。文献[6]设计一款在V至W(75~110 GHz)波段的低噪放相对带宽达50.9%,实现了W波段最大带宽,而文献[7-8]低噪放频率跨入到F(90~140 GHz)波段,其中文献[7]使用两级T型网络匹配Cascode单元实现了47.2%的宽带,文献[8]使用L型网络匹配Cascode单元实现了21.8%的宽带,L型网络常用于窄带匹配,因此文献[8]难以匹配出较大带宽,文献[7]使用两级的T型匹配网络虽然实现了带内较好的驻波性能,却没有实现最大带宽匹配,同时两级T型网络的损耗增加了低噪放的噪声。因此,本文提出了一种高Q值的单级T型匹配网络以扩展低噪放带宽并降低其噪声系数,并采用该T型网络匹配Cascode增益单元,以实现毫米波频段较大的带宽和较低的噪声系数。

1 低噪放设计

1.1 宽带和低噪声原理

在毫米波频段,电路损耗和晶体管产生的热噪声是毫米波电路的主要噪声源。因此,对于毫米波低噪放而言,降低电路损耗成为降低噪声的一种方法,设计高Q值匹配网络以降低匹配损耗是毫米波低噪放的一个设计方向,同时,通过提高放大单元增益降低后级放大器对噪声影响以进一步降低噪声系数。

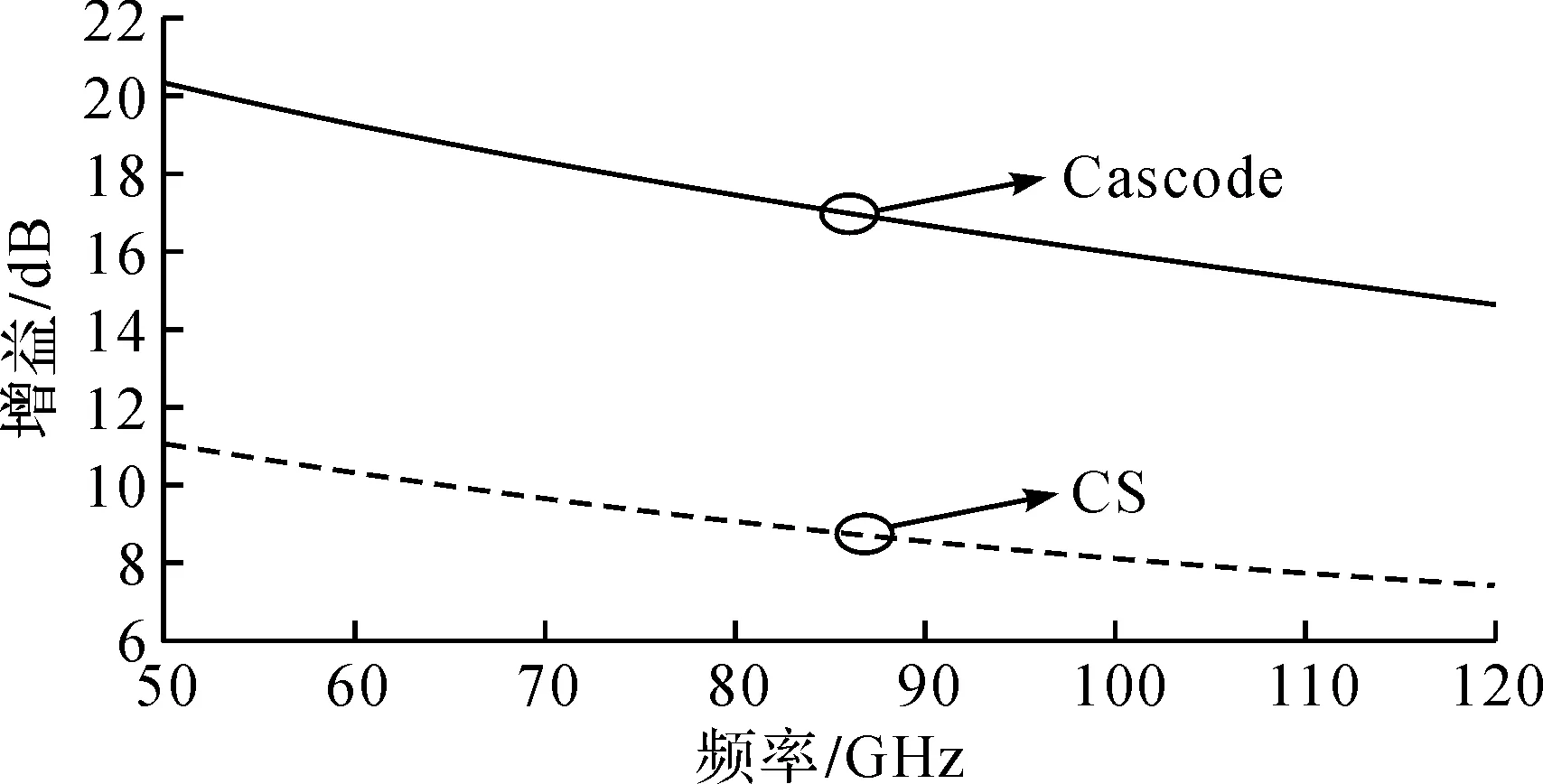

图1 共源共栅和共源结构最大增益比较

Cascode是一种通过共栅管(CG)作负载以提高共源管(CS)增益的结构,Cascode具有较高隔离度和增益,易于实现宽带匹配的优点,因此可以使用Cascode这些特性来简化匹配结构以降低匹配损耗,实现放大器的宽带低噪声等性能。Cascode结构中共栅管以增大输出负载的方式增加整体增益,对同样尺寸的Cascode结构和共源管进行S参数仿真,其增益如图1所示,Cascode最大增益大于共源级,可见采用Cascode提高电路增益,可以降低后级放大器噪声对整个低噪放噪声的影响,降低电路噪声系数。

由于晶体管的寄生电容效应,晶体管输入输出阻抗呈容性,Cascode结构输入输出阻抗的史密斯圆图如图2(a)所示,S11和S22均在第4象限靠近最外面的圆,输入输出阻抗为R+1/(jwC),其中R为电阻,w为角频率,C为电容,j为虚部,该阻抗宜采用L型匹配网络匹配到50 Ω,L型匹配如图2(b)所示,在75 GHz处将阻抗50×(0.15-j2.018) Ω匹配到50 Ω时,取L1=45.44 pH,L2=175.72 pH即可实现75 GHz的点频匹配。而宽带匹配比点频匹配复杂,可以在L型网络上再串联一个电感形成T型匹配网络,T型匹配可以看成两级的L型匹配级联,相比L型匹配,T型匹配网络更适合宽带,是最简单的宽带匹配结构。

图2 Cascode端口阻抗和L型匹配

1.2 电路设计

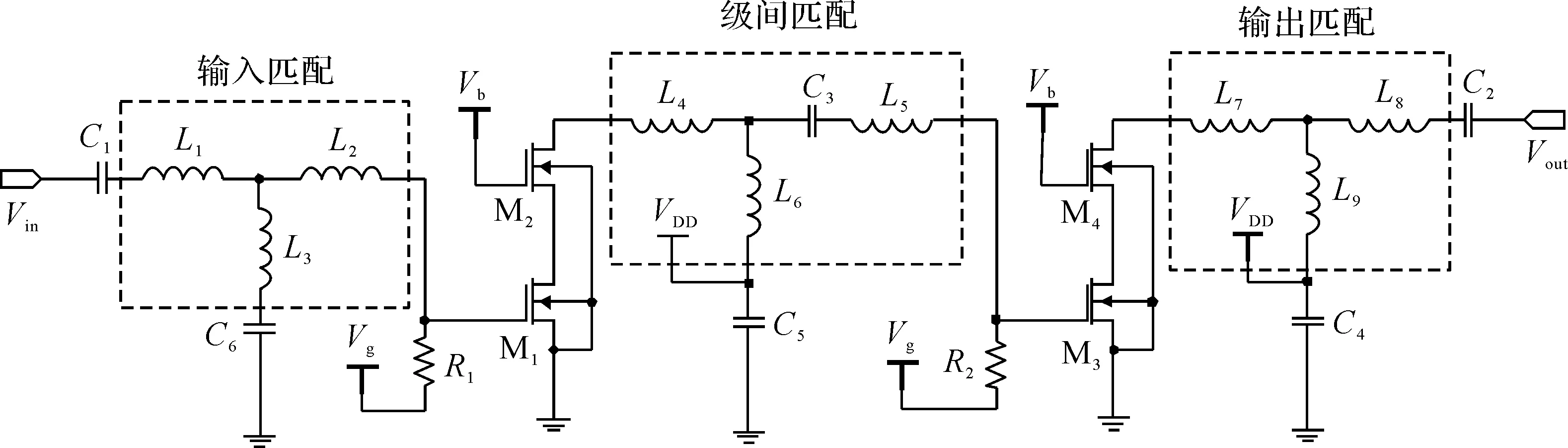

本文设计的电路原理如图3所示,两级增益单元尺寸相同,晶体管M1和M2的栅宽分别为2 μm×15和2 μm×30,共源管偏置Vg为0.8 V,共栅管偏置Vb为2.4 V,电阻R1和R2为3 kΩ,供电电压VDD为2.4 V。

图3 低噪放电路原理图

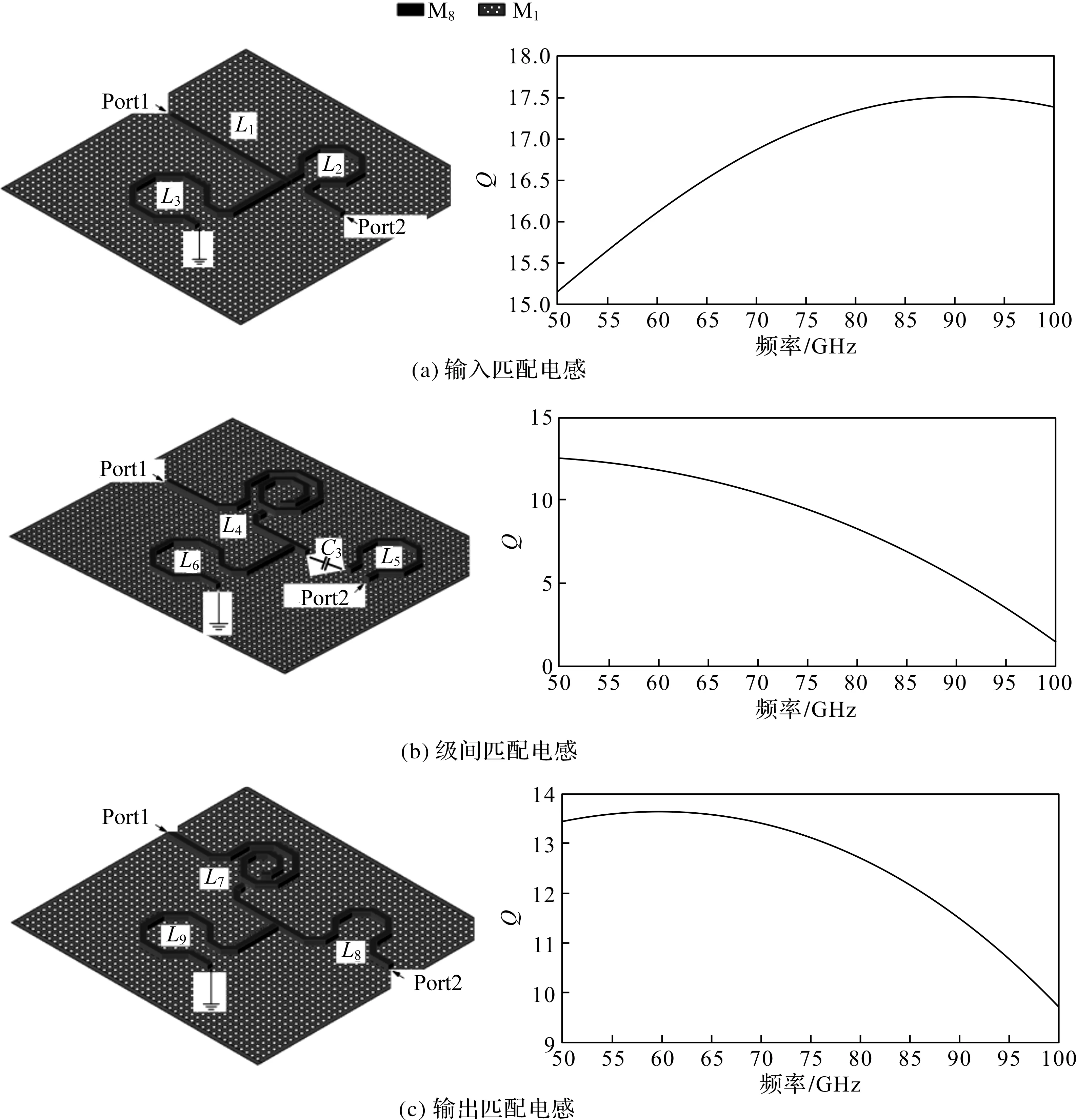

由于CMOS工艺的硅衬底在毫米波频段损耗非常大,以硅衬底为介质的传输线Q值低,设计传输线时需要将衬底屏蔽以降低介质损耗。因此该匹配电感以第1层金属层M1为地,第8层布线层M8设计八边形电感,电感线宽取4 μm,M8层4 μm线宽特征阻抗约等于50 Ω,M8层厚3.3 μm,电感截面接近正方形,最大程度降低电感损耗,T型匹配网络示意图和Q值曲线如图4所示。

图4 T型电感匹配网络及其Q值

图3中,C1和C2为输入输出匹配电容,同时起到隔直流的作用,容值分别为560 fF和63 fF。C3,C4,C5,C6为交流接地电容,容值为800 fF,工艺库中适合设计较大容值的电容是阱电容,Q值较高但容值较小的是交指电容,所以C1,C3—C6采用N阱电容,C2采用交指电容。80 GHz处电容Q值曲线如图5所示,输入输出匹配电容Q值分别约为0.2和50,隔直电容Q值约为0.2。

图5 N阱电容和交指电容Q值

2 版图和仿真结果

2.1 低噪放版图

电路采用65 nm CMOS工艺,硅基衬底厚度为737 μm,工艺有9层金属层,M1—M6金属层厚度为0.220 μm,适合晶体管间小距离布线,最顶层金属层M7—M9,厚度分别为0.900 μm,3.300 μm,1.325 μm,用来长距离或较大功率走线。图6为低噪放版图,版图尺寸为500 μm×800 μm。

图6 宽带低噪声放大器版图

2.2 仿真结果

本文设计的宽带低噪放仿真结果如图7所示。其中图7(a)为小信号S参数仿真结果,中心频率增益为15.75 dB,3 dB带宽为53~99 GHz,3 dB相对带宽达63.5%,为兼顾增益的平坦和宽带特性,设计中允许电路存在一定的失配,带内S11在89 GHz处最大达到-1.9 dB,但带内其它频率反射较小,S11在64 GHz处有最小值-15 dB;图7(b)为噪声系数曲线,带内88 GHz处有最小噪声系数3.9 dB,53 GHz处有最大噪声系数7.9 dB;图7(c)为1 dB压缩点仿真结果,可见低噪放的输入1 dB压缩点(IP1dB)为-12.5 dBm,饱和输出功率(Psat)为5 dBm;图7(d)为稳定因子曲线,稳定因子最小值为6.1,可见低噪放在带内带外均无条件稳定。

图7 低噪放仿真结果

本文中低噪放和其它使用65 nm CMOS工艺的低噪放对比结果如表1所示。从表1可以看出:文献[4]、文献[5]、文献[7]及文献[8]的低噪放均采用Cascode结构,其中文献[4-5]为Q波段的低噪放,噪声系数和功耗均较为理想,但文献[4]的增益和文献[5]的带宽均较小,文献[7-8]的低噪放频率进入F波段,文献[7]的低噪放具有文献中最大增益指标25.3 dB,其输入输出采用两级T型微带匹配,所以文献[7]的低噪放输入输出反射指标是表1中最好的,但文献[7-8]的低噪放噪声系数和功耗较大,且文献[8]的相对带宽在表1中是最小的,文献[6]采用跨导增强技术(Gm-boost)的共源结构实现了50.9%的宽带低噪放,在参考文献中具有最大相对带宽,但文献[6]的低噪放噪声系数相对较大。本文设计的低噪放3 dB相对带宽达到63.5%,在表1的参考文献中最大,最小噪声系数仅为3.9 dB,综合噪声性能优于其它文献,低噪放的增益、线性度和功耗指标均较理想,但设计中为实现毫米波的宽带低噪声性能,低噪放在匹配上做出了一定折中,导致低噪放在89 GHz处的S11最大达到-1.9 dB,在输入输出反射指标上不及其它文献。

表1 CMOS工艺毫米波宽带低噪放设计方法对比

3 结束语

本文从提高增益和降低损耗两方向出发,使用具有宽带输入输出阻抗特性的共源共栅结构和自定义的T型匹配网络实现低损耗宽带匹配,设计一款单级T型网络宽带匹配式的毫米波宽带低噪放,兼顾了噪声和带宽两个重要指标,拓展了毫米波低噪放在W波段的带宽。但单级T型网络并不能使端口阻抗在宽带内完全匹配到50 Ω以实现较理想的输入输出反射指标,需要结合其它技术兼顾低噪放输入输出反射指标。