基于FPGA的声纳系统数据编码模块设计与研究

2020-02-03吴锟刘慧

吴锟 刘慧

(1.上海船舶电子设备研究所 上海市 201108 2.91860 部队 上海市 200940)

声纳系统数据贯穿于声纳发射机、接收机及信号处理机的各个环节,是反映声纳系统各项技术指标的直接载体,这些数据需要进行传输、存储和事后分析处理[1]。声纳数据的传输是连接声纳系统水下与水上设备的中枢,主要用于将水下设备采集的数据快速可靠地传输至水上信号处理模块中,其精确性和可靠性对声纳系统信号采集与处理的稳定可靠运行具有重要影响。随着声纳 系统数据容量越来越大,频率等级越来越高,传统的诸如串口、ATM 光纤传输方案已呈现出诸多难以克服的瓶颈。基于集光学与电子技术于一体的以太网传输方案有效解决了传统串口、ATM 光纤等传输方案存在的带宽限制与可靠性等一系列问题,还保留了成熟的传输技术,与光电子技术相结合,具有提升带宽、可靠性高等传统传输方案无法比拟的优势。本文设计的声纳系统数据以太网传输编码模块是以太网光纤通信的重要组成部分,它的实现可使声纳系统水下与水上的数据通信更加高速可靠。

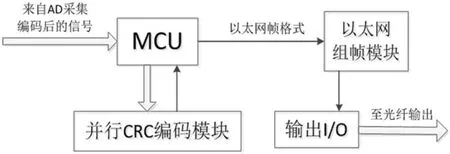

图1:以太网传输编码模块总体设计

1 设计概述

声纳系统水下接收换能器的输出信号为非常微弱的模拟信号,抗干扰能力很弱,在高电压强磁场并水下复杂环境下进行传送,精度很难保证,因此必须进行数字化处理。虽然水下接收机AD 采集模块已对换能器输出的模拟信号做了数字化处理,但为了保证数据能实时可靠地传送,对接收机AD 采集编码后的数据进行二次编码处理,按照以太网数据帧格式将编码后的数据传送至水上信号处理模块中。以太网传输编码模块的原理框图如图1 所示。

图1 中MCU 采用Xinilx 的V5 系列FPGA,接收来自AD 采集编码后的信号,控制各功能模块完成数据编码及组帧。其中最为关键的是CRC 校验码的产生,以下将从理论计算和硬件逻辑实现两方面对其做重点阐述。

2 CRC编码模块的FPGA实现

2.1 CRC校验的基本原理

循环冗余校验(CRC)是一种数字通信中常用的信道编码技术,其特征是信息段和校验字段的长度可以任意选定。CRC 编码由信息码和校验码两部分组成,在Kbit 信息码后在拼接Rbit 的校验码,使整个编码长度变为Nbit,以增加整个编码系统的码距和查错能力,此种码制被称为(N,K)。在产生CRC 校验码时,需要用到除法运算,这是比较麻烦的,因此,对于给定的(N,K)序列,利用最高次幂为N-K=R 的生成多项式G(x),即xR+xR-1+…+x2+x+1 来表示二进制序列,生成Rbit 的校验码。将待传输的数据位串看做是一个系数为0或1 的多项式K(x)的系数序列,根据发送端与接收端约定好的生成多项式G(x)去除K(x),得到的余数多项式即为CRC 校验码。将CRC 校验码续接到信息码的尾部构成完整的CRC 码,继而发送到接收端。接收端接收到CRC 码后,利用同样的生成多项式G(x)再去除接收到的CRC 码,如果传输过程没有误码,接收到的CRC 码可被生成多项式G(x)整除,得到的余数为0,反之即为传输过程中出现了误码。

2.2 CRC校验码的实现方法

2.2.1 串行实现方法

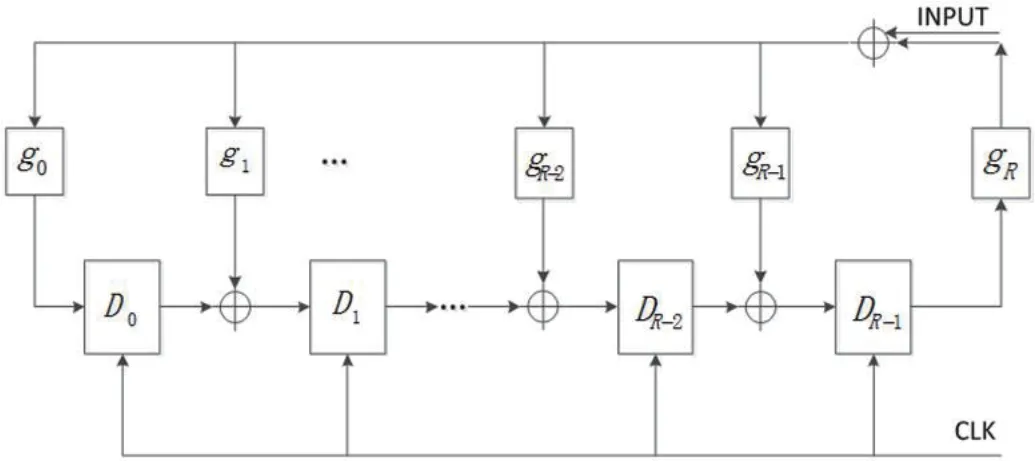

CRC 编码模块本质上是利用了模2 除的运算法则,即在除法运算中加法不考虑进位,减法不考虑借位,可通过数字逻辑中的移位和异或操作来实现。CRC 校验码其实就是模2 除的余数,常采用线性反馈移位寄存器(LFSR)寄存余数,模2 运算用异或门实现,则通用的CRC 串行编码原理就可由n 个D 触发器和若干个异或门的电路结构来实现,如图2 所示。

对于生成多项式G(x)来说,存在Rbit 的CRC 校验码,需要R个D 触发器(D0, D1, …DR-1)。图中反馈项gi(i=0,1,2,3,…R)表示生成多项式G(x)的系数,当gi=1 时,代表存在反馈,需要进行异或运算;当gi=0 时,代表不存在反馈,无需进行异或运算,一般地,g0=gR恒为1,即代表始终存在反馈。串行计算产生CRC 校验码时,此电路可以完成上述的模2 除的运算,外部时钟同步启动线性反馈移位寄存器,每次输入一位数据,输入的数据和上一次异或运算的结果组合,循环进行异或运算,直到所有的数据全部输入完毕,DR-1到D0中的数据即为所要求的余数,即CRC 校验码。

图2:编码原理图

图3:CRC-32 编码仿真波形

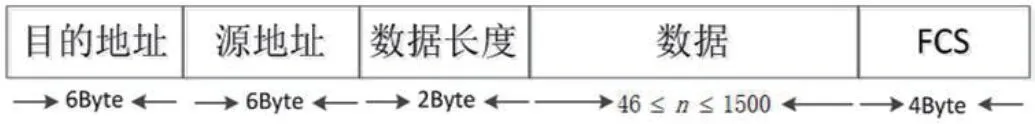

图4:以太网MAC 子层帧格式

2.2.2 并行实现方法

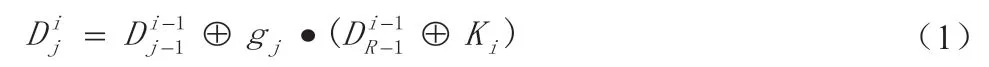

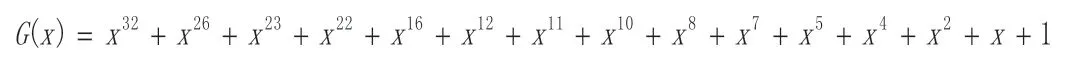

并行实现方法是在串行实现方法的基础上,利用迭代运算进行逻辑推导。当nbit 信息码并行输入运算电路,CRC 校验码的计算结果应与串行计算结果一致。根据串行计算时各移位寄存器的状态值只与信息码当前的输入值和各移位寄存器的上一个状态值有关这一特点,可以推导出CRC 校验码并行计算的逻辑关系。设Dij 表示第i 个信息码序列输入后,第j 个移位寄存器的状态值,j=0,1,2,…,R-1为移位寄存器序列号,Ki(i=1,2,3,…)为输入的信息码序列,根据图2 可得:

2.3 CRC校验码的FPGA实现

大规模集成电路及计算机技术的发展,使得之前相对复杂的算法实现成为可能。现场可编程门阵列FPGA 的出现能够解决许多传统数字电路设计中遇到的问题,它能够便捷地实现复杂数字系统的设计。本设计主要是利用Xilinx 公司Virtex-5 系列FPGA 芯片,内置有用于构建大型阵列的FIFO 逻辑,逻辑单元多达330000 个[3],在ISE13.3 开发环境下采用Verilog 语言描述电路结构,通过片上专用的RocketIO 收发器资源实现编码模块及以太网光纤通信功能。

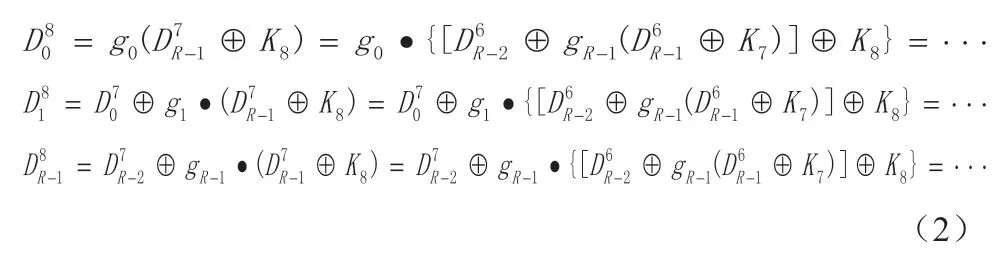

在数字编码模块的设计中,为了满足声纳系统通信的高速、可靠性要求,采用CRC-32 并行算法实现CRC 校验码的生成。发送方和接收方按照规定的CRC-32 生成多项式

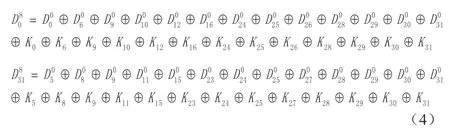

得到R 的值为32,将其带入式(2)中,得到8bit 并行数据的CRC-32 校验码的计算式(4)。

上式中D0j(j=0,1,…31)为触发器j 在本次8bit 并行数据输入前的初始值,对于整个包含若干字节的数据帧,其CRC-32 校验码的产生就是由上一个并行输入的8bit 数据的校验结果作为下一个数据校验过程中移位寄存器的初始值,如此循环往复,在整个数据帧最后一个字节数据并行输入后的下一拍,就能输出整个数据帧的CRC-32 校验码。

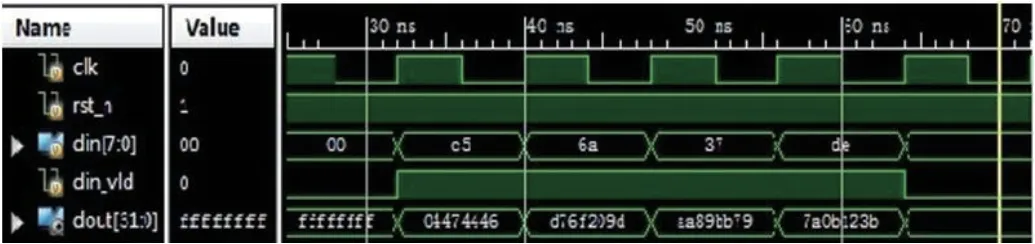

本设计中进行了4 个字节(C56A37DE,十六进制,从高位到低位)CRC-32 校验码编码实验。通过在ISE13.3 开发环境下对Verilog 硬件描述语言进行编译、仿真、下载,实现了上述8 位并行输入数据CRC-32 编码功能。仿真结果如图3 所示。

从仿真结果看到,寄存器中存储的余数值的计算结果符合上述整个数据帧的运算流程,即每个时钟周期并行输入一个字节,在第1 个时钟周期,系统复位并初始化,寄存器清零。从第2 个时钟周期开始向Verilog 描述的运算电路并行输入8bit 数据,电路计算的并行数据与寄存器的初始值按照上述推导的逻辑关系计算,得到的32 位的CRC 余数值存入寄存器中。当第3 个时钟的8bit 数据并行输入时,再次与寄存器当前余数值进行异或运算,得到的新的余数值再次存入寄存器中,如此循环往复迭代计算,当整个帧4 字节数据全部输入完毕后,生成的CRC-32 校验码为7A0B123B,即为整个数据帧的CRC-32 的校验码。

3 以太网组帧模块的实现

以太网上的数据通过MAC 子层在上层协议和以太网网络之间利用光纤介质进行传输和接收数据,其主要功能是确保以太网上每一帧数据的传输都遵循IEEE802.3 规范所规定的介质存取规则[4]。以太网MAC 子层帧格式如图4 所示[5]。

图中目的地址用于识别需要接收帧的站,源地址用于识别发送帧的站,数据长度定义了数据字段的长度,数据是一组字节的任意值序列,FCS 为帧状态检测字段,该序列包括32 位的循环冗余校验(CRC)值,由发送MAC 方生成,通过接收MAC 方进行计算得出,以校验帧传输过程中出现的误码。

MAC 子层从上层协议接收到发送帧数据的请求,首先插入目的地址和源地址,其次统计来自上层协议数据的长度,插入量值,然后插入来自上层协议的数据,如果数据小于46 个字节,则自动补齐46 字节,最后根据目的地址、源地址、数据长度和数据产生CRC-32 校验码,并插入该校验序列,以太网数据组帧完成。在全双工方式下发送整个以太网数据帧至接收端,接收端接收整个数据帧后,首先检查数据帧中的目的地址和当前地址是否相符,然后检查接收到的数据帧中的数据长度和CRC-32 校验序列和实际的数据长度、CRC-32 校验序列是否相符。如果均相符,表明数据传输过程中未出现误码,传输任务完成。

4 结论

声纳系统内部的数据传输采用先进的电子及以太网光纤通信技术,具有广泛的通用性。本文介绍的基于FPGA 的声纳系统数据编码设计方法包含了CRC 校验模块、以太网组帧模块,从理论分析了CRC 校验码的生成,采用CRC 并行算法在FPGA 上实现以太网数据传输编码模块。实际测试也证明本方案能够满足声纳系统数据传输的高速性、实时性和可靠性的要求,方案是可行的,可广泛地通用于声纳数据通信系统,具有使用价值。同时,本方案的设计实现采用了目前应用的现场可编程逻辑器件FPGA,使声纳系统数据传输的精度更高,更加稳定,可快捷地完成系统所要求的数据传输任务。