S波段宽带数字变频单元的设计与实现

2020-02-03刘洪升李宏王瑞斌

刘洪升 李宏 王瑞斌

(西安电子工程研究所 陕西省西安市 710100)

1 概述

某数字阵列雷达工作在S 波段,主要完成低空超低空搜索功能,还需重点监测“低慢小”目标。雷达工作的外部环境中存在强烈的地杂波,工作时需从纷繁复杂的外部环境中分辨运动目标,就要求数字变频单元需要具备极低相位噪声、极低杂散干扰的特性,并可实现宽带数字收发以满足雷达目标识别能力。

2 设计方案

该数字变频单元主要用于产生8 路雷达发射激励信号,并完成8 路回波信号的变频、中频放大、AD 采样、抽取、时序控制等功能。发射激励信号具有瞬时宽带工作模式,可实现移频、移相功能。

2.1 方案简介

本系统采用二次变频体制,并使用DDS、ADC 等产生频率、相位可控的发射激励信号和数字接收信号,形成数字收发阵列。系统实现方案框图如图1 所示。

2.2 数字单元

数字单元主要由FPGA、ADC、DDS、光收发模块、电源芯片、接口芯片等组成,主要完成以下功能:

2.2.1 FPGA

(1)对外通信及时序重建;

(2)对AD 采样数据下变频、数字滤波;

(3)8 路变频组件的控制;

(4)波控功能;

(5)故障信息汇总。

2.2.2 AD

(1)对变频组件的回波信号进行采样;

(2)校准时对DDS 输出信号进行采样。

2.2.3 DDS

(1)产生发射中频信号,也可产生窄带线性调频信号;

(2)频率分集功能;

(3)由频移控制码和相移控制码控制,进行频率补偿和相位补偿。

2.2.4 供电

2.3 光纤通信

正常工作时,在每个波前脉冲之前,通过光纤接口将下一波列周期的控制参数发送给数字单元。然后光纤通信模块调用FPGA 内部的高速收发模块GTX 将高速串口信号转换为32 位并行数据,再经过FIFO 缓存后译码产生时序参数、工作参数和自检参数等,并在波列脉冲的上升沿使能译码产生的控制参数。同时,数字单元在每个波列脉冲周期内将校验参数、故障信息和I/Q 基带数据上报给上级。

2.4 时序响应及处理

数字单元接收来自信处提供的CPI 同步时序信号,一个CPI 内包含若干PRI 信号,并于首个PRI 工作前完成参数配置工作;CPI内的多个PRI 信号具有相同时域特性。根据PRI 时序产生并设置收发通道相关参数,使之可按要求收发信号,采样后送至信处进行检测。

图1:数字变频单元原理框图

2.5 波形信号产生

波形信号产生功能根据工作参数,控制DDS 产生中频信号,具有多种波形和频率,并通过移频、移相进行补偿。主要包含复杂波形产生功能、信号频率值切换控制功能以及选择不同波形信号模式开启或关闭功能。上述各种功能控制由芯片内部独立的各个子模块单独完成,在时间域上的执行模式属于并行模式。

2.6 ADC采样处理

数字单元中,ADC 先进行采样,得到的数字中频频率信号与数控振荡器时域相乘,形成相位差互为90 度的两路I、Q 基带信号,再由FIR 低通数字滤波器滤除系统不需要使用的高频频率分量,最后通过GXB 传输到信处分系统进行进一步处理。

2.7 变频组件

上行通道DDS 产生的发射中频信号与本振信号进行混频,产生8 路发射激励信号;下行通道回波信号与本振信号进行混频,经中频放大产生数字单元ADC 采样所需的接收中频信号。收发通道中均设计有收发开关,根据收发转换脉冲等时序,完成接发收转换功能。

3 关键技术及分析

3.1 多通道相位同步

数字阵列雷达正常工作需要每个单元都同步受控,同步精度为同步时钟频率的倒数。在发射时,若不能实现同步控制,则得不到发射合成波束,且单元相互间还会产生干扰,系统不能正常工作;在接收时,若不能实现同步控制,则得不到接收合成波束,且还可能引起数据错误。因此多通道相位同步是数字阵列雷达的实现难点之一。

数字变频单元同时产生8 路发射激励信号,每路信号都经过一个独立的信号传输通道,包含DDS、混频器、放大器、滤波器等元器件。以上所述元器件,每个独立的器件均具有自身固有的群时延特性,当这些元器件串联成为电路系统时,会因各自特性的趋向性,产生一定延时的通道误差。系统加电后,环境温度因系统工作而产生变化;同时以年为单位,系统进行长时间的使用后也会因元器件的退化等因素产生变化;基于以上短期和长期的系统环境变化,必然会因不同程度的影响,导致通道群延时误差的产生。

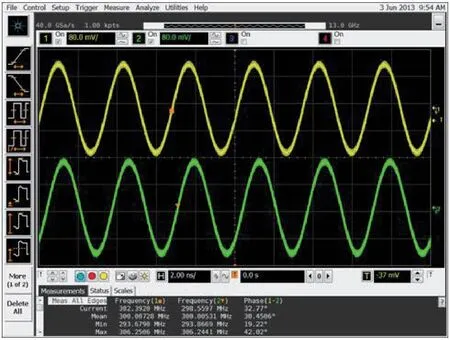

图2:两通道间的初始相位差(30.45°)

图3:修正后两通道间的相位差(0°)

本设计中时序信号、采样时钟及DDS 时钟严格保证等延时传输,并且采用了一款国产的DDS 芯片GM4941,该DDS 具有4 路独立通道,每个通道均可提供独立的相位、频率、幅度控制,所有通道共用一个公共系统时钟,具有固有的同步性,避免了在多路DDS 同步过程中由于器件差异造成同步困难的问题。对于大于4通道系统的扩展应用,GM4941 还支持多芯片的同步。在数字阵列雷达中,可以采用多片GM4941 来进行同步,同时配合软件校准的方法,降低同步设计难度,提供了灵活的控制方法。

在系统上电自检期间,由ADC 对每路信号进行采样。通过开关控制可以直接对DDS 输出的中频信号进行采样,然后通过FPGA 计算各路信号之间的相位差,通过DDS 进行相位补偿,从而保证每路信号之间具有相同相位。

如图2 所示,每次上电通道1 和通道2 之间的相位差为30.45°;图3 中通过调整通道1 的相位寄存器,将初始相位改为30.45°,通道1 和通道2 之间的相位差变为-0.04°,实现同相位。通过FPGA 控制电路基带初相,发射通道相位控制精度可达0.1°(均值)。

3.2 孔径渡越补偿

针对大孔径相控阵雷达在宽带宽角扫描时的孔径渡越问题,采用频移时延补偿技术,发射时通过DDS 频率控制字进行发射通道时延补偿,接收时在信号处理进行多普勒时延补偿。

以发射信号为例,由于不同阵元的位置差异使得发射的信号不能同时到达目标处,即不同阵元发射的信号到达等相位面的时间不同,引起波束指向随时间变化,严重时不能正常形成天线波束。

宽带线性调频信号形式为:

第i 个振子的信号:

消除孔径渡越效应需要在通道间进行合适的延时,在采用宽带线性调频信号的前提下,可以通过调整通道间发射/接收的信号的频率,产生等效的延时,从而解决孔径渡越效应。消除孔径渡越需要分发射和接收过程分别进行。

发射时,根据天线阵面各天线单元的相位中心位置、波束指向的方向、发射线性调频信号的调频斜率计算得到各DDS 的频率控制字,由DDS 调整发射信号初始频率对各路发射信号延时分别进行补偿。

接收时,各个通道首先进行模拟去斜接收处理,再由信处分系统根据回波波束的指向性,计算出全阵面每个通道接收回波的时延,同时将其转换为对应的频率,再与回波信号进行相加补偿,用以处理大阵面多通道接收延时问题。

3.3 杂散

该系统对于杂散的抑制主要还是取决于不同频率间的混频比选择以及集成元器件本身的固有干扰。在进行设计时需考虑交调频率分量的相互叠加,以保证其干扰落在输出信号路径中放置的带通滤波器有效带宽带外,达到信号的有效输出,同时保持其低杂散特性。模块级电路设计中,混频、滤波、放大等元器件的选择及使用,均需对其带宽、驻波等技术指标进行统筹考虑,用以满足电路系统对瞬时宽带工作的特殊要求。

在系统运行过程中,有一部分杂散并非来自于主信号输出通道,而是来自于输出端口耦合通道。所以滤波器的设置需全局考虑,包括小型化密集的相邻信号通道以及同一信号通道经过某一元器件后产生不同相位的两个信号通道上也均需设置滤波器,用以加强隔离。另外,在放大链路设计上,应根据指标要求,进行两级或多级衰放处理,用来提高放大链路的反向隔离度。

4 产品研制结果

该数字变频单元研制取得了比较满意的结果,其具体指标满足输入要求,相噪恶化小于1dB,可实现窄带线性调频、相位编码、瞬时大带宽线性调频等多种信号波形,并具有实时移频、移相功能,可满足雷达目标识别、阵面孔径渡越等需求。

5 结束语

根据已有经验对该设备输入技术指标进行详细分解,设计了一种宽带数字变频单元,完成对其关键技术的剖析。目前,该产品已成功应用某雷达产品,工程应用意义重大。