基于FPGA和NAND Flash的存储器ECC设计与实现

2012-06-23邢开宇曹晓曼方火能

邢开宇,曹晓曼,方火能

(西安电子科技大学电子工程学院,陕西 西安 710071)

近年来,得益于大规模集成电路技术的发展,以NAND Flash为代表的半导体固态存储器发展迅速。与传统的磁带记录设备相比,NAND Flash具有存储密度高、可靠性强、体积小、重量轻、操作速度快、容量价格比高等多方面优势,从而逐渐在各领域取代传统的磁记录设备,更是成为航天、军事等对存储质量要求较高领域中的首选。

虽然NAND Flash已具有较高的可靠性,但受其制作工艺所限,同时考虑到星载设备所面临的复杂工作环境,在其使用过程中仍可能出现错“位”现象,即存储数据可能会有几个数据位出错。虽然这种错误出现的概率较低,但对于通常应用而言,无需特别注意,但在一些场合,若错误发生在某个重要的数据上,即可能导致严重后果。此时就需要为所设计的存储系统添加必要的纠错模块,以确保其稳定性,常用的有奇偶校验、循环冗余校验和ECC校验等[1]。

ECC(Error Correcting Code)校验算法[2]是在奇偶校验的基础上发展起来的数据纠错方法,能够纠正1 bit错误并能检测2 bit错误,但对于2 bit以上的错误不能保证检测。与其他纠错算法相比,ECC算法具有占用资源少、运行速度高的优点,可以方便地在FPGA中实现,同时具有较强的纠错能力。文中根据某星载高速大容量存储器的硬件组成和结构特点,在FPGA中设计和实现了ECC算法模块,该算法模块具有1 bit/4 kB的纠错能力,为存储器的稳定性提供有力保证。

1 存储器的主要硬件组成

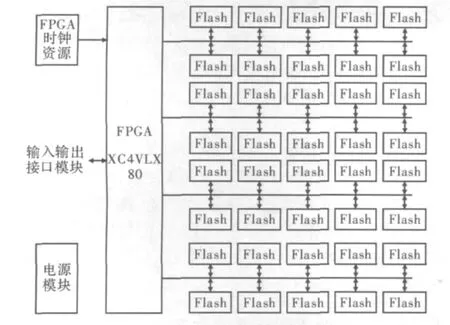

本存储器设备是某星载存储阵列系统的组成部分,负责对输入的高速数据进行实时不失真的存储和回读。该存储器主要由1片FPGA和40片NAND Flash芯片构成,其硬件结构如图1所示。

如图1所示,存储器采用Xilinx公司的高性能FPGA XC4VLX80作为核心控制芯片,主要负责对数据的缓存变速以及对NAND Flash阵列的控制,同时负责输入输出数据ECC校验码的产生和纠错工作。存储器的存储介质采用三星公司的NAND Flash芯片K9WBG08U1M[3],其单片存储容量为 4 GB,基本结构可以按块和页划分,读写操作均以页为单位进行,一页由4096 Byte的主存储空间和128 Byte的附加存储空间组成。

图1 存储器的硬件组成结构图

2 ECC校验模块的整体设计思路

根据NAND Flash的组成结构和读写数据的操作方式,存储器的输入输出数据均以4096个8位数据为单位组成数据包进行传送,因此,ECC校验码也是以1页数据为单位进行的[4]。

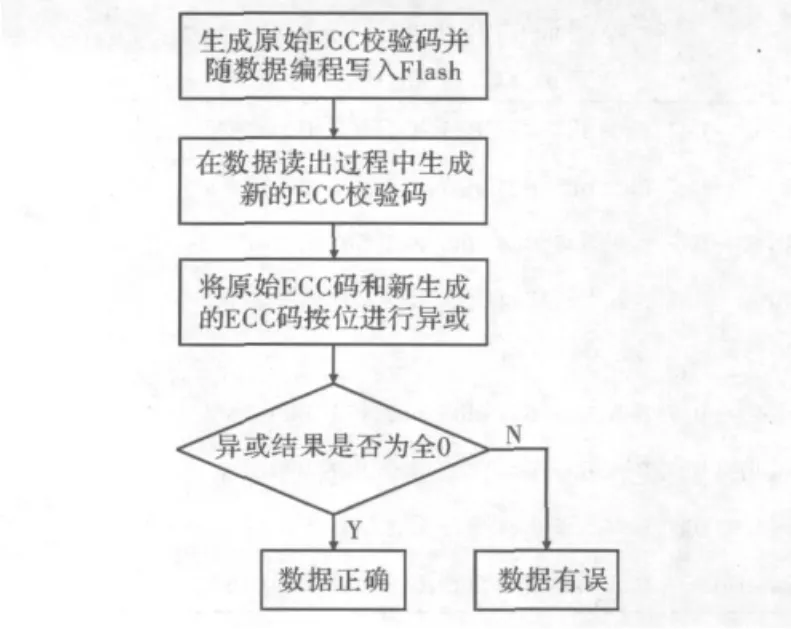

文中所设计的ECC校验模块的基本工作流程如下:

(1)在存储数据输入的过程中,以4096个数据为单位,实时地产生原始的ECC校验码,并将其与相应的数据存入同一个Flash页中,其中,4096 Byte数据存入Flash页的基本存储空间中,4个8位ECC编码存入附加存储空间中。

(2)在进行读出操作时,将在Flash中存储的数据和原始ECC校验码同时读出,并根据从主存储空间中读出的有效数据,同样以4096个数据为单位,生成新的ECC校验码。

(3)将原始和新生成的ECC校验码按位进行异或,并根据异或结果确定数据中是否出现了错“位”现象及进行纠错处理。

综上所述,ECC校验的流程如图2所示[5]。

3 ECC校验码的产生方法

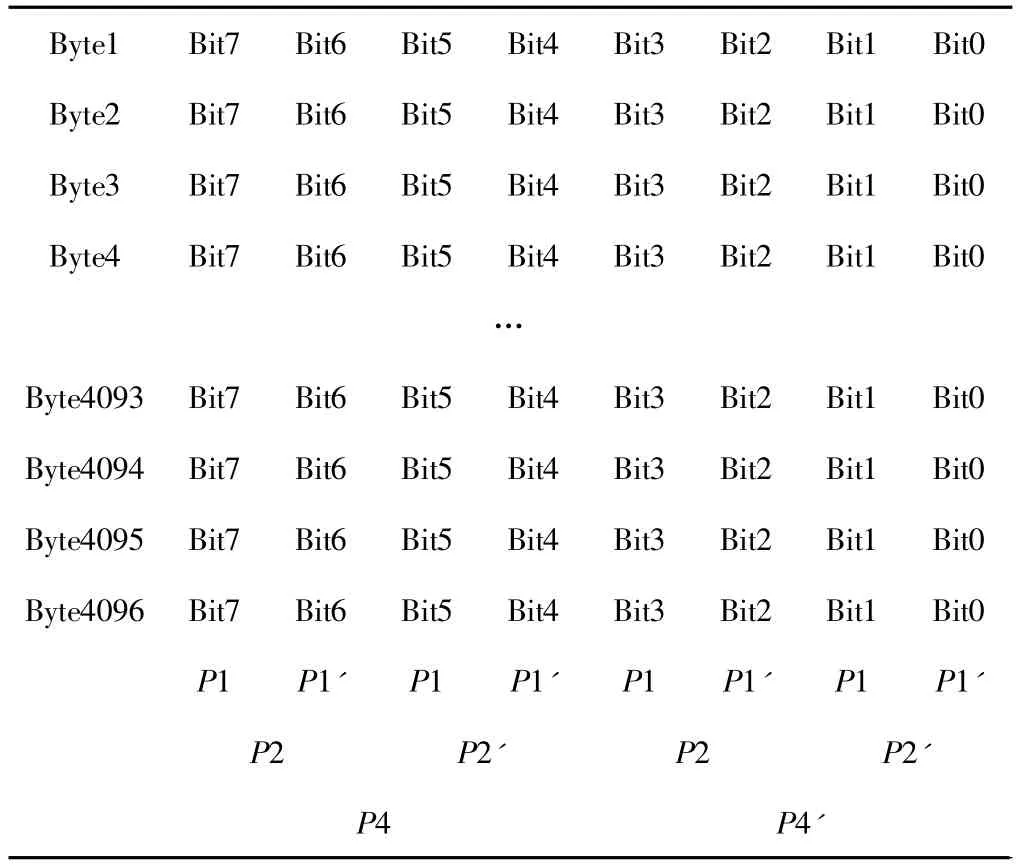

ECC校验码由列校验码和行校验码组成,按照ECC校验码的基本产生方法,4096个8位数据可以生成6位列校验码和24位行校验码。为方便存储,文中将生成的30位校验码封装在4个8位的编码数据中,如表1所示。

图2 ECC算法流程图

表1 ECC校验码结构组成表

表1中,P8~P16384是行校验码,P1~P4是列校验码,同时在列校验码的低两位补1,从而组成8位的列校验编码数据。ECC列校验码的产生方法如表2所示。

表2 ECC列校验码的产生方式表

表2中列校验码的产生方法可以用如下数学表达式表示,其中“(+)”符号代表异或运算。P1=bit7(+)bit5(+)bit3(+)bit1(+)P1;P1'=bit6(+)bit4(+)bit2(+)bit0(+)P1';P2=bit7(+)bit6(+)bit3(+)bit2(+)P2;P2'=bit5(+)bit4(+)bit1(+)bit0(+)P2';P4=bit7(+)bit6(+)bit5(+)bit4(+)P4;P4'=bit3(+)bit2(+)bit1(+)bit0(+)P4'。

ECC行校验码的产生方法如表3所示。

表3 ECC行校验码的产生式表

其中P8和P8′的产生方法的数学表达式如下,其余行校验码的产生方法类似。P8=bit7(+)bit6(+)bit5(+)bit4(+)bit3(+)bit2(+)bit1(+)bit0(+)P8(偶数Byte);P8'=bit7(+)bit6(+)bit5(+)bit4(+)bit3(+)bit2(+)bit1(+)bit0(+)P8'(奇数Byte)。

由以上ECC校验码的产生方法可知,列校验码与行校验码的生成没有本质的区别。ECC校验码可以看成是由不同的ECC校验码组组成,每个ECC校验码组包括两位ECC校验码,如P1和P1′即为一个ECC校验码组。在进行ECC编码时,可以将4096个8位数据看成是4096×8个顺序的1位数据,各ECC校验码组在生成时首先根据各自不同的分类方法,将参与ECC编码的数据以位为最小单位,均分为两组。如列校验码组P1和P1′是将数据每隔1位进行抽取而分成两组,而行校验码组P8和P8′则是将数据每隔1 Byte进行抽取而分成两组,因此,PN中的数据N也同时代表了分组时连续抽取的数据位数。之后将两组中的数据位分别进行异或,从而得到两个ECC校验码位。最后将所有的ECC校验码位组合就得到了最终的ECC校验码。

4 ECC算法对错误的检测和处理

根据文中所述ECC校验码的产生方法,以4096 Byte为单位,分别在存储和读取操作中对数据进行ECC编码,并将两次产生的ECC校验码中的有效数据按位进行异或,得到30位的异或结果,其不同情况所代表的实际意义如下:

(1)异或结果所有位均为0,即新旧ECC编码相同,表示数据完全正确。

(2)异或结果中,每组ECC编码均是一位为1,另一位为0,表示数据有一位出错,且该错误可以纠正。其中,出错数据的位置由不带“'”标的ECC编码的异或结果给出,其中行编码 P16384、P8192、P4096、P2048、P1024、P512、P256、P128、P64、P32、P16、P8 的异或结果表示出错数据的偏移地址,列编码P4、P2、P1的异或结果表示出错位在8位数据中的位置。

(3)异或结果中只有一位是1,表示ECC校验码错误。

(4)异或结果为上述结果以外的其他结果,表示数据有2位以上的错误,但该错误无法纠正。

当4096 Byte数据中产生了1位的错误时,可根据ECC校验码异或结果中所包含的位置信息和输出数据的序数,将出错数据的相应数据位与1异或,从而对错误进行纠正。

5 ECC算法实现结果的采样和分析

文中在ISE10.1开发环境中对所设计的ECC算法模块进行了搭建和实现,并下载至存储器FPGA中,通过ChipScope Pro在线逻辑分析仪对相关信号进行采样,以验证设计的正确性[6]。

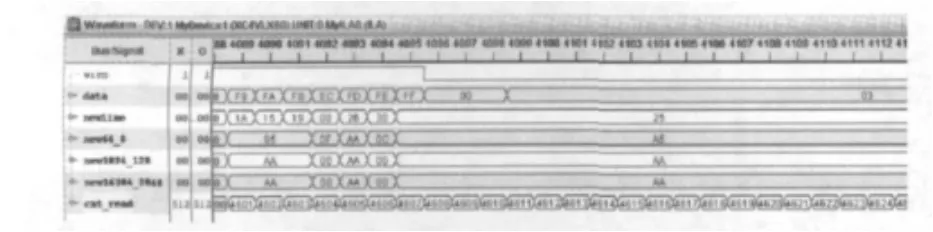

存储器的写入数据以4096个8位数据为单位组成数据包,速率为200 MB/s,有效数据的平均速率为150 MB/s。为方便测试,文中通过外部的模拟数据源,以循环顺序数0x00~0xFF组成数据包,因而4096个数据中含有16组0x00~0xFF。在FPGA对输入数据进行接收和缓存的同时,存入数据的ECC校验码产生模块以数据包为单位实时的计算ECC校验码,在进行Flash页编程时,FPGA将有效数据和相应的ECC校验码写入同一个Flash页中。其中,输入数据ECC校验码的产生效果采样如图3所示。

图3 输入数据ECC校验码产生效果采样

图3中,line信号和data信号分别是有效数据的使能信号和输入的8位数据;middle信号是根据当前输入数据产生的7位中间值,其最高位是当前输入的8位数据各位异或的结果,用于行校验码的计算,其余6位是按照不同的方式抽取当前输入数据的1/2进行异或的结果,用于列校验码的产生;code16384_2048、code1024_128、code64_8是实时计算的 ECC行校验码,linecode是ECC列校验码;cnt_data是ECC校验码计算过程的指令计数器,编码模块根据其取值的不同进行相应的操作。从图中可以看出,ECC校验码的计算模块工作正常,最终生成的校验码code16384_2048、code1024_128、code64_8和 linecode分别为 0x00、0x00、0x00和0x03,计算结果正确。

由于NAND Flash的错“位”概率较低,因此,为了对ECC模块的功能进行验证,在进行Flash页编程时,将数据包中最后一个0xFC改为0xEC进行存储,由于0xFC和0xEC的二进制形式分别为0b1111_1100和0b1110_1100,因而这一改变是对1 bit错误的模拟。其仅发生在Flash的页编程过程中,输入数据的ECC编码不受影响,依然按照改变前的数据计算。读出数据的ECC校验码的产生方法与存入数据相同,且同样是在数据缓存的过程中进行,其结果如图4所示。图中,wren用于指示从Flash读出的有效数据的范围;data是从Flash中读出的数据和ECC校验码,有效数据后面紧跟的4个数据是存入数据的ECC校验码;cnt_read是校验码计算过程的指令计数器。从图中可以看出,由于存储数据的改变,读出数据的 ECC校验码new16384_2048,new1024_128,new64_8 和 newline分别变为0xAA、0xAA、0xA5 和0x25。

图4 读出数据ECC校验码产生效果采样

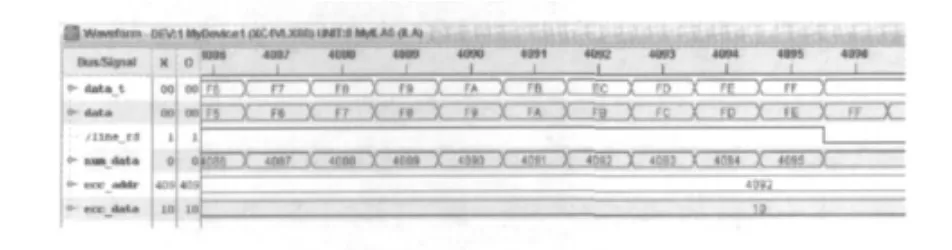

将新旧ECC校验码按位进行异或,并根据结果对输出数据进行检错和纠错,其采样效果如图5所示。

图5 ECC算法模块纠错效果采样图

如图5所示,data_t和data分别是纠错前和纠错后的输出数据;line_rd信号是输出数据的有效数据指示信号;ecc_addr和ecc_data分别是由ECC校验码计算出的出错数据的偏移地址和用于与出错数据进行异或运算的纠错数据;num_data是纠错前数据的实时偏移地址。从图中可以看出,ECC算法模块正确计算出了出错数据的地址4092,并且当输出数据到达该地址时,利用纠错数据0x10,成功将出错数据0xEC更正为0xFC,正确地实现了功能。

6 结束语

对ECC算法的原理及其实现的方法和流程进了分析和介绍,并在某高速大容量存储器的FPGA中设计和实现了ECC算法模块,根据实际采样结果,文中设计的ECC模块正确地实现了其功能。ECC算法具有纠错能力强、占用资源少、运行速度高,易于实现等优点,有效的保证了存储器的可靠性。

[1]Samsung Electronics Corpration.NAND Flash ECC Algorithm[M].Korea:Samsung Electronics Corpration,2004.

[2]贾红恩,刘瑞竹,罗丰.基于固态存储器的ECC算法分析及实现[J].电子科技,2009,22(10):43 -46.

[3]Samsung Electronics Corpration.K9WBG08U1M Flash Memory[M].Korea:Samsung Electronics Corpration,2007.

[4]Xilinx Corporation.Virtex-4 FPGA User Guide[M].USA:Xilinx Corporation,2008.

[5]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[6]王诚,薛小刚,钟信潮.FPGA/CPLD设计工具——Xilinx ISE使用详解[M].北京:人民邮电出版社,2005.